## AN11019

CLRC663, MFRC630, MFRC 631, SLRC610 Antenna Design Guide

Rev. 1.0 — 17 July 2012 205810 Application note COMPANY PUBLIC

#### Document information

| Info     | Content                                                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | CLRC663, MFRC630, MFRC631, SLRC610, antenna tuning, directly matched antenna design, reader tuning, matching procedure                                                                                                                            |

| Abstract | This document describes the principles of antenna tuning for the contactless reader IC CLRC663, MFRC630, MFRC631, SLRC610. A practical example is given to tune an ID2±10 antenna for all baud rates according to ISO/IEC 14443 and ISO/IEC 15693 |

#### **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 1.0 | 20120717 | Initial Release |

## **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

AN11019

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2012. All rights reserved.

Application note COMPANY PUBLIC

## 1. Introduction

This application note is intended to give a practical guide to match an application specific antenna coil to the output driver of the CLRC663 and its derivates MFRC630, MFRC631 and SLRC610; further reference as the "CLRC663 Family". The antenna is directly connected to the reader board without any cable in between the reader and the antenna.

## 2. How to use this document

The application note is intended to give a practical guide to design antennas and calculate the matching components for the CLRC663 Family.

The user can follow the guideline to design an antenna and the RF circuitry and will find a tuning procedure described as well. The guideline covers the following items:

- 1. RF field generation and data transmission part

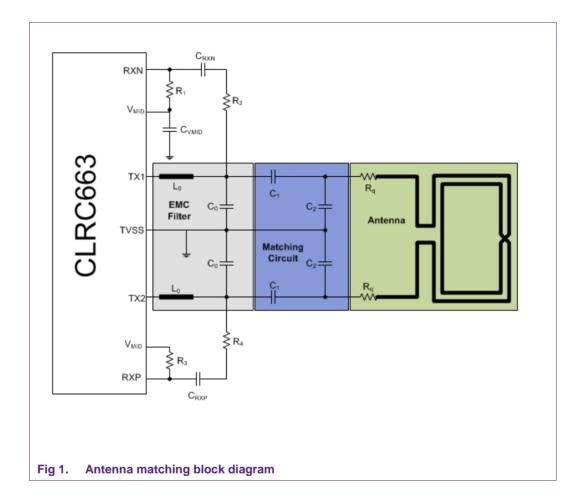

- a. The **RF part block diagram** in Fig 1 shows a recommended circuitry design with all relevant components required to connect an antenna to the CLRC663 Family. It also ensures the transmission of energy and data to the target device as well as the reception of a target device answer.

- b. The TX matching resistance R<sub>match</sub> is explained which is required to calculate the remaining components and to optimize the RF system properties.

- c. Formulas to calculate the EMC filter and the matching circuit

- d. Antenna tuning procedure

- 2. Receiver part

- a. Design and calculation of the receiver part

- 3. Example calculations

- **Note:** This application note does not replace the relevant specifications for the different operating modes.

"Card" or "Target device" in this document means a contactless smart card according to the ISO14443A (or MIFARE) scheme. Design hints on how to place the components on a PCB are not included.

Tuning and measurement of the reader antenna has always to be performed at the final mounting position to consider all parasitic effects, e.g. metal influence on quality factor, inductance and additional capacitance.

## 3. General aspects

The CLRC663 device is designed to communicate in the following operation modes:

- 1. read/write mode supporting ISO/IEC 14443A/MIFARE

- 2. read/write mode supporting ISO/IEC 14443B

- 3. read/write mode supporting FeliCa scheme

- 4. read/write mode supporting ISO/IEC 15693

- 5. read/write mode supporting ICODE EPC UID/ EPC OTP

- 6. read/write mode supporting ISO/IEC 18000-3 Mode 3

The MFRC630 device is designed to communicate in the following operation modes:

1. read/write mode supporting ISO/IEC 14443A/MIFARE

The MFRC631 device is designed to communicate in the following operation modes:

- 1. read/write mode supporting ISO/IEC 14443A/MIFARE

- 2. read/write mode supporting ISO/IEC 14443B

The SLRC610 device is designed to communicate in the following operation modes:

- 1. read/write mode supporting ISO/IEC 15693

- 2. read/write mode supporting ICODE EPC UID/ EPC OTP

- 3. read/write mode supporting ISO/IEC 18000-3 Mode 3

The communication distance is dependent on different factors including primarily

- the reader and card antenna size

- antenna area

- coupling between antennas

- generated Reader HF field

- minimum H-Field required by card

- environmental influences and other aspects.

The CLRC663 family's overall functionality can be separated into three functions:

- 1. **Generate the RF field**: The generated magnetic field has to be maximized within the limits of the transmitter supply current, general emission limits and requirements to protocol standards.

- 2. **Transmit data**: The coded and modulated data signal has to be transmitted in a way, that all supported card standards are able to receive it. The signal shape and timing according to relevant standards has to be considered.

- 3. **Receive data**: The response of a card or NFC passive device has to be transferred to the differential or single sided receive input of the CLRC663 considering various limits, e.g. maximum voltage and receiver sensitivity.

Application note COMPANY PUBLIC

## 4. Matching the CLRC663 family

The **RF block diagram** shows the circuitry design with all relevant components required to connect an antenna to the CLRC663 family. It also ensures the transmission of energy and data to the target device as well as the reception of a target device answer.

The following blocks and their functionality have to be considered to guarantee the proper working of the complete device:

- The EMC filter reduces 13.56 MHz harmonics and performs an impedance transformation.

- The EMC filter coil has to be chosen according to Table 1

- The matching circuit acts as an impedance transformation block.

- The antenna coil itself generates the magnetic field.

- The receiving part provides the received signal to the CLRC663 family's internal receiving stage.

| Table 1. C                                       | Component list and requirements for a basic RF Design                                                                                                                       |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abbreviatio                                      | n Explanation                                                                                                                                                               |

| Rq                                               | External damping resistors to adjust the quality factor. The power dissipation has to be considered.                                                                        |

| C <sub>0</sub> , C <sub>1</sub> , C <sub>2</sub> | Typically 0603 or 0805 SMD parts with low tolerance (< $\pm 2\%$ ). NP0 dielectric is required for temperature stability reasons. Voltage ratings must be higher than 200V. |

| $C_{vmid}, C_{RX}$                               | X7R capacitor (< ±10%)                                                                                                                                                      |

| Lo                                               | The EMC inductance must have a Q<20 at 13.56MHz. Current rating for the coil must be higher than 400mA.                                                                     |

| $R_1, R_2, R_3, R_4$                             | 4 0603 or 0805 SMD parts                                                                                                                                                    |

#### Table 1. Component list and requirements for a basic RF Design

**Note:** The center tap connection of the antenna (dotted line) may be neglected without negative influence on the EMC performance of the circuitry.

**Application note**

COMPANY PUBLIC

## 5. Step 1 – Antenna Matching

The antenna is matched without powering the CLRC663 family. The basic transmitter matching can be also done without assembly of the IC.

The following subchapters describe the matching procedure. It starts with the determination of the antenna parameters and ends with a fine tuning of the antenna circuitry.

The antenna equivalent circuit (inductance, capacitance and resistance) and quality factor have to be determined first.

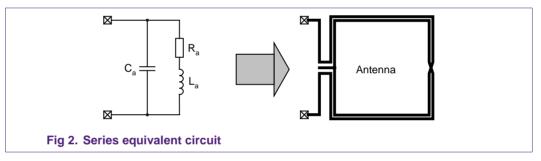

#### 5.1.1 Determination of series equivalent circuit

The antenna loop has to be connected to an impedance or network analyzer to measure the series equivalent components. The analyzer has to be calibrated accordingly before measurements are done.

**Note:** The equivalent circuit (see Fig 7) must be determined under final environmental conditions especially if the antenna will be operated in metal environment or a ferrite will be used for shielding.

It is recommended to measure the inductance as well as the series resistance value at 1MHz. The self resonance frequency and the parallel resistance can be obtained at the resonant point of the system where the imaginary part is zero.

Typical values:

$L_a = 0.3...4 \mu H$

$C_a = 3...30 pF$

R<sub>a</sub> = 0.3...8Ω

$f_{ra}$  = self-resonance frequency of the antenna

The antenna capacitance C<sub>a</sub> can be calculated with:

$$C_a = \frac{1}{\left(2 \cdot \pi \cdot f_{ra}\right)^2 L_a} \tag{1}$$

The antenna parasitic capacitance  $C_a$  should be kept low to achieve a self-resonance frequency > 35 MHz.

AN11019

#### 5.1.2 Calculation of damping resistor $R_{Q}$

The quality factor of the antenna is calculated with

$$Q_a = \frac{\omega \cdot L_a}{R_a} \tag{2}$$

If the calculated value of  $Q_a$  is higher than the target value of 30, an external damping resistor  $R_Q$  has to be inserted on each antenna side to reduce the Q-factor to a value of **30 (±10%)**.

The value of  $R_Q$  (each side of the antenna) is calculated by

$$R_{Q} = 0.5 \cdot \left(\frac{\omega \cdot L_{a}}{30} - R_{a}\right) \tag{3}$$

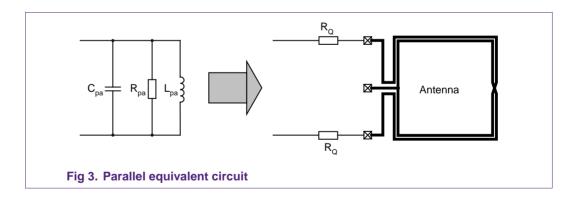

#### 5.1.3 Determination of parallel equivalent circuit

The parallel equivalent circuit of the **antenna together with the added external damping resistor**  $R_Q$  has to be measured. The quality factor should be checked again to be sure to achieve the required value of Q=30.

**Note:** The equivalent circuit (Fig 8) must be determined under final environmental conditions especially if the antenna will be operated in metal environment or a ferrite will be used for shielding.

The following formula applies

$$\begin{split} L_{pa} &\triangleq L_a \\ C_{pa} &\triangleq C_a \\ R_{pa} &\triangleq \frac{\left(\omega \cdot L_a\right)^2}{R_a + 2 \cdot R_0} \end{split}$$

(4)

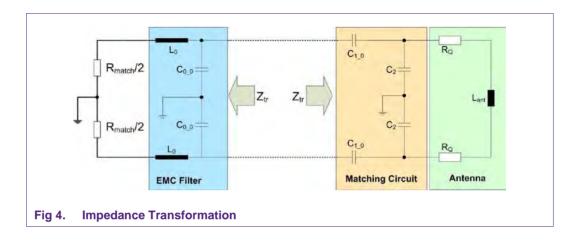

#### 5.2 EMC filter design

The EMC filter circuit for the CLRC663 family fulfills two functions: the filtering of the signal and impedance transformation block. The main properties of the impedance transformation are:

- Decreasing the amplitude rise time after a modulation phase

- Increasing the receiving bandwidth

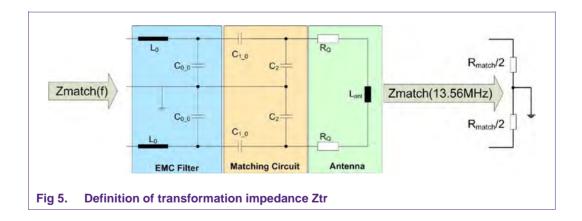

The EMC filter and the matching circuit must transform the antenna impedance to the required TX matching resistance  $Z_{match}(f)$  at the operating frequency of f = 13.56 MHz.

The measured  $Z_{\text{match(f)}}$  can be remodeled in an equivalent circuit loading each TX pin with  $R_{\text{match/2}}.$

When cutting the circuitry after the EMC filter the precondition Rmatch/2 needs to be introduced to calculate the remaining components.

#### Note, that R<sub>match/2</sub> does not reflect the driver resistance!

$$Z_{tr} = R_{tr} + jX_{tr}$$

(5)

$$Z_{tr}^{*} = R_{tr} - jX_{tr}$$

(6)

EMC filter general design rules:

$L_0 = 390$ nH - 1µH Filter resonance frequency  $f_{r0} = 21$  MHz, =>  $C_0$

$$C_0 = \frac{1}{\left(2 \cdot \pi \cdot f_{r0}\right)^2 L_0}$$

(7)

The EMC filter resonance frequency  $f_{r0}$  has to be higher than the upper sideband frequency determined by the highest data rate (848 kHz sub carrier) in the system.

#### Example:

# $\begin{array}{l} \mathsf{L}_0=470n\mathsf{H}\\ \mathsf{f}_{r0}=21\mathsf{M}\mathsf{Hz}\\ \mathsf{C}_0=122.2\mathsf{p}\mathsf{F}\rightarrow\mathsf{chosen:}\ 120\mathsf{p}\mathsf{F} \end{array}$

A recommended value of 470nH for  $L_0$  is chosen to calculate the capacitance  $C_0$ . The following formulas apply for  $Z_{ant} = Re(Z_{ant})+Im(Z_{ant})$  and are needed to calculate the matching components.

$$R_{tr} = \frac{R_{match}}{\left(1 - \omega^{2} \cdot L_{0} \cdot C_{0}\right)^{2} + \left(\omega \cdot \frac{R_{match}}{2} \cdot C_{0}\right)^{2}}$$

$$X_{tr} = 2 \cdot \omega \cdot \frac{L_{0} \cdot \left(1 - \omega^{2} \cdot L_{0} \cdot C_{0}\right) - \frac{R_{match}^{2}}{4} \cdot C_{0}}{\left(1 - \omega^{2} \cdot L_{0} \cdot C_{0}\right)^{2} + \left(\omega \cdot \frac{R_{match}}{2} \cdot C_{0}\right)^{2}}$$

(9)

AN11019

(11)

### 5.3 Matching circuit design

#### 5.3.1 Component calculation

The following formulas apply for the series and parallel matching capacitances:

$$C_1 \approx \frac{1}{\omega \cdot \left(\sqrt{\frac{R_{tr} \cdot R_{pa}}{4}} + \frac{X_{tr}}{2}\right)}$$

(10)

$$C_{2} \approx \frac{1}{\omega^{2} \cdot \frac{L_{pa}}{2}} - \frac{1}{\omega \cdot \sqrt{\frac{R_{tr} \cdot R_{pa}}{4}}} - 2 \cdot C_{pa}$$

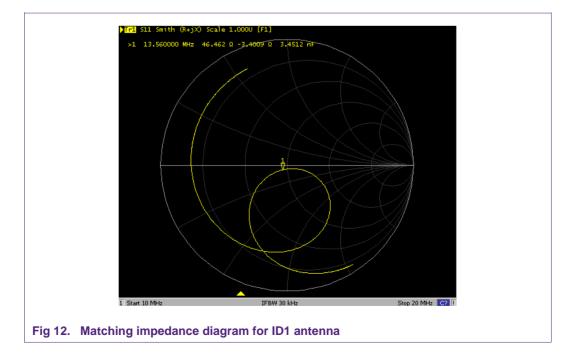

Finally, a fine tuning of the matching circuit is often necessary, since the calculated values are based on simplified equations and the equivalent circuit values contain some errors as well.

#### 5.4 Tuning procedure

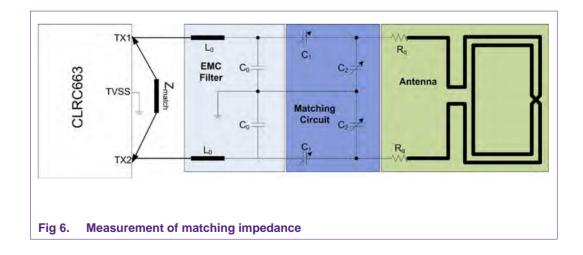

The matching circuit elements  $C_1$  and  $C_2$  must be tuned to get the required matching resistance  $R_{match}$  ( $X_{match} = 0$ ) at the CLRC663, MFRC630, MFRC631 or SLRC610 TX pins. The matching impedance  $Z_{match} = R_{match} + jX_{match}$  is measured with an impedance or network analyzer. The  $Z_{match}$  point between TX1 and TX2 as shown in Fig 12 is the probing point for the network/impedance analyzer.

**Application note**

COMPANY PUBLIC

205810

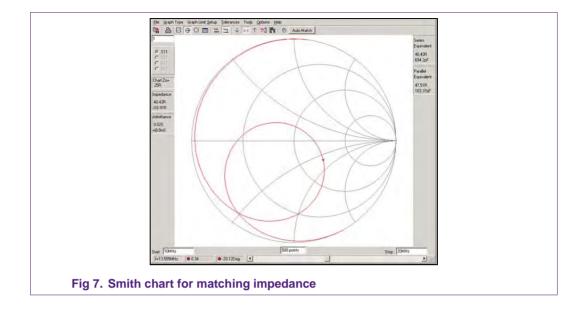

Fig 13 shows the smith chart simulation for  $Z_{match}/2$ :

**Note:** All tuning and measurement of the antenna has to be performed at the final mounting position to consider all parasitic effects like metal which influences the quality factor, the inductance and parasitic capacitance.

#### 5.4.1 Transmitter matching resistance R<sub>match</sub>

The transmitter (TX) matching resistance  $R_{match}$  defines the equivalent resistance at the operating frequency present between the transmitter output pins TX1 and TX2 of the CLRC663. Different equivalent resistive loads lead to different transmitter supply currents.

The optimum matching resistance is dependent on antenna shape, size and end application

## An optimum tuning R<sub>match</sub> for CLRC663 family is between 40-80Ohm This tuning is measured in an unloaded condition

#### 5.5 Impact of the tuning capacitors visualized on Smith chart

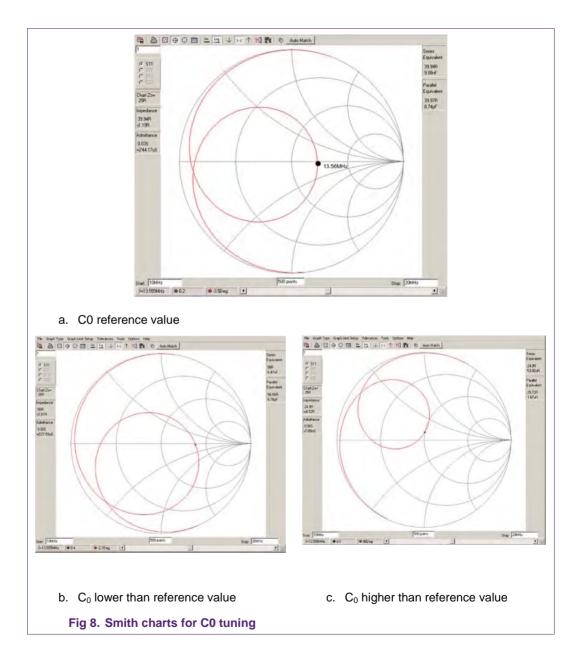

#### 5.5.1 EMC capacitance C0

The following diagrams show the effect to the impedance curve by changing C0. The smith charts show the matching impedance  $Z_{match}$  / 2 vs. frequency.

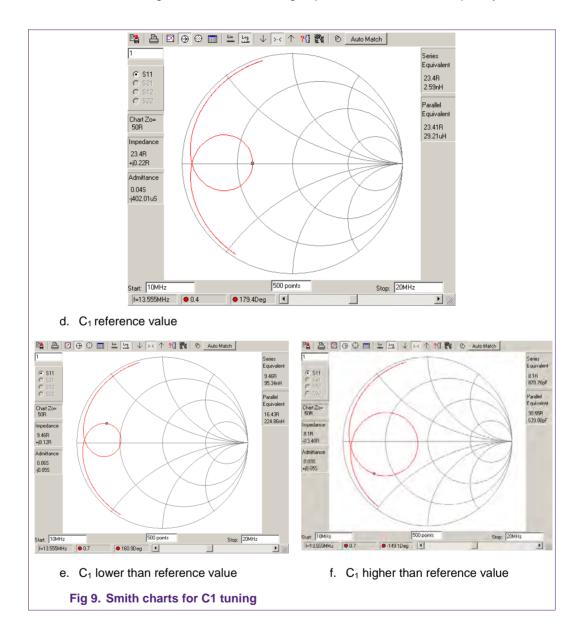

#### 5.5.2 Series capacitance C1

The following diagrams show the effect to the impedance curve by changing C1. The smith charts in Fig 15 show the matching impedance  $Z_{match}/2$  vs. frequency.

$C_1$  changes the magnitude of the matching impedance. After changing  $C_1$  the imaginary part of  $Z_{match}$  must be compensated by adjusting  $C_2$  as well.

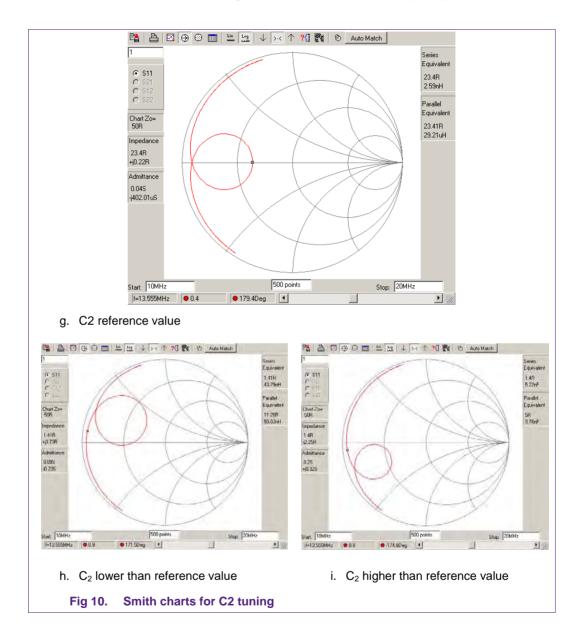

#### 5.5.3 Parallel matching capacitance C2

The following diagrams show the effect to the impedance curve by changing C2.

The smith charts show the matching impedance  $Z_{match}$  / 2 vs. frequency.

$C_2$  changes mainly the imaginary part of  $Z_{match}$ .

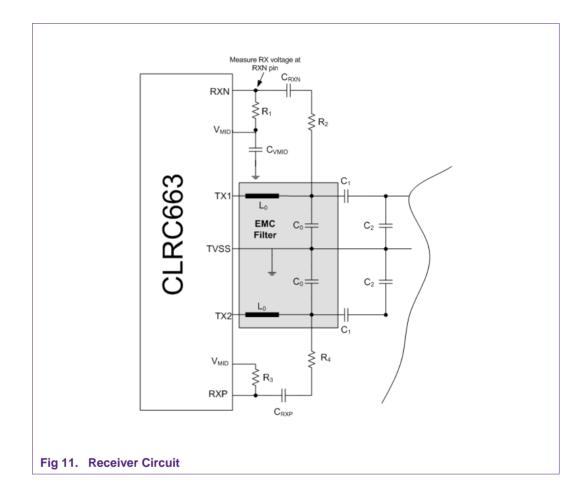

## 5.6 Receiver circuit design

Next step, after matching and tuning the Reader/Writer antenna, is the design and tuning of the receiver circuit. The investigations need to be carried out under various practical antenna loading effects like presenting different cards, mobile phones, etc.

Fig 11 shows the relevant components for the receiver circuit.

The internal receiving concept of the CLRC663 family makes use both side-bands of the sub-carrier load modulation of the card response via a differential receiving concept (RXP,RXN). No external filtering is required. It is recommended to use the internally generated VMID DC potential as the input potential of pin RXN and RXP. This DC voltage level of VMID has to be coupled to the RX-pins via R1 and R3. To provide a stable DC reference voltage, capacitances  $C_{VMID}$  has to be connected between VMID and ground.

Considering the (AC) voltage limits at the Rx-pins the AC voltage divider of R1 and R2 as well as R3 and R4 has to be designed. Depending on the antenna coil design and the impedance matching the voltage at the antenna coil varies from antenna to antenna. Therefore, the recommended way to design the receiving circuit is to use the given starting values for R1 (=R3) and R2(=R4) and adjust the voltage at the RX-pins by varying R2(=R4) in respect to the RX input limits.

AN11019

The voltage  $U_{RX}$  on RXN pin must be measured with a low capacitance probe (< 2 pF) for continuous transmitting mode

The voltage U<sub>RX</sub> must not exceed the maximum value U<sub>RXmax</sub>=1.7Vpp even when the antenna is detuned by a target or passive card

Hence, the RX-point must be checked under following conditions:

- 1. CLRC663 family antenna not detuned

- 2. CLRC663 family antenna loaded under various conditions

#### Matching Recommendations **6**.

Antennas of different shapes must be individually matched to the CLRC663 family. The tuning is dependent on the requirements (e.g. baud rates, protocols, environment, etc.) of the end application. The following subchapters explain matching recommendations for antennas with form factors of ID2 +10%.

#### 6.1 Matching Recommendations for Antenna Size ID2

This chapter explains the matching procedure of a 2turn ID2 (+10%) antenna for the ISO14443 protocol for all baud rates.

The recommended matching impedance at 13.56MHz is  $R_{match} \approx 500$ hm + j0.

The EMC filter resonance frequency recommendation is  $R_{res EMC} \approx 21 Mhz$

The following Fig shows the target matching for this antenna size. The matching steps are described below.

COMPANY PUBLIC

205810

AN11019

At first, the series equivalent parameters of the antenna have to be determined using a network analyzer. Details can be found in chapter 5.

Measurement results:

$R_{a} = 0.33Ohm$  $C_{a} \approx 7pF$  $L_{a} = 1.2\mu H$  $R_{p} \approx 3.8kOhm$

The calculation for the external damping resistor for a quality factor of 10 results to  $R_Q = 4.30$  hm. The chosen value for  $R_Q$  is 4.70 hm; the high damping resistor and low Q factor is required for realizing the tight modulation requirements for higher baud rates.

The provided excel sheet for matching calculation will help to determine the remaining components.

The parallel equivalent circuit (calculated at a frequency of 13.56MHz) of the antenna including quality factor damping resistors  $R_Q = 4.70$ hm is determined with the following values:

$R_{pa} = 7.7$ kOhm  $C_{pa} = 6,7$ pF  $L_{pa} = 1.2$ µH

The EMC filter is determined with:

$R_{res EMC} \approx 21MHz$   $L_0 = 470nH$  $C_0 = 56pF+68pF$

Calculation of Z<sub>tr</sub>:

$R_{tr} = 1550 hm$

$X_{tr} = 28.90 hm$

Calculation of the matching parts  $C_1$ ,  $C_2$

$C_1 = 57.10 pF \rightarrow 50 pF$  normalized value  $C_2 = 154.9 pF \rightarrow 162 pF$  normalized value

The receiver path has been assembled with R2=22 kOhm and R1=1kOhm The receiver is connected at the antenna between the points of C1 and C2.

AN11019

## 7. Legal information

#### 7.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

## 7.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

AN11019

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 7.3 Licenses

Purchase of NXP ICs with NFC technology

Purchase of an NXP Semiconductors IC that complies with one of the Near Field Communication (NFC) standards ISO/IEC 18092 and ISO/IEC 21481 does not convey an implied license under any patent right infringed by implementation of any of those standards.

#### Purchase of NXP ICs with ISO/IEC 14443 type B functionality

This NXP Semiconductors IC is ISO/IEC 14443 Type B software enabled and is licensed under Innovatron's Contactless Card patents license for ISO/IEC 14443 B.

The license includes the right to use the IC in systems and/or end-user equipment.

RATP/Innovatron Technology

## 7.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

MIFARE — is a trademark of NXP B.V.

## 8. List of figures

| Fig 1.  | Antenna matching block diagram              | 6  |

|---------|---------------------------------------------|----|

| Fig 2.  | Series equivalent circuit                   | 8  |

| Fig 3.  | Parallel equivalent circuit                 | 9  |

| Fig 4.  | Impedance Transformation                    | 10 |

| Fig 5.  | Definition of transformation impedance Ztr. | 10 |

| Fig 6.  | Measurement of matching impedance           | 12 |

| Fig 7.  | Smith chart for matching impedance          | 13 |

| Fig 8.  | Smith charts for C0 tuning                  | 14 |

| Fig 9.  | Smith charts for C1 tuning                  | 15 |

| Fig 10. | Smith charts for C2 tuning                  | 16 |

| Fig 11. | Receiver Circuit                            | 17 |

| Fig 12. | Matching impedance diagram for ID1          |    |

|         | antenna                                     | 18 |

Application note COMPANY PUBLIC

## 9. List of tables

| Table 1. | Component list and requirements for a basic RF |

|----------|------------------------------------------------|

|          | Design7                                        |

AN11019

Application note COMPANY PUBLIC

## **10. Contents**

| 1.    | Introduction                                       | 3  |

|-------|----------------------------------------------------|----|

| 2.    | How to use this document                           | 3  |

| 3.    | General aspects                                    | 4  |

| 4.    | Matching the CLRC663 family                        | 6  |

| 5.    | Step 1 – Antenna Matching                          | 8  |

| 5.1.1 | Determination of series equivalent circuit         | 8  |

| 5.1.2 | Calculation of damping resistor R <sub>Q</sub>     | 9  |

| 5.1.3 | Determination of parallel equivalent circuit       | 9  |

| 5.2   | EMC filter design                                  |    |

| 5.3   | Matching circuit design                            | 12 |

| 5.3.1 | Component calculation                              | 12 |

| 5.4   | Tuning procedure                                   |    |

| 5.4.1 | Transmitter matching resistance R <sub>match</sub> |    |

| 5.5   | Impact of the tuning capacitors visualized on      | i  |

|       | Smith chart                                        |    |

| 5.5.1 | EMC capacitance C0                                 |    |

| 5.5.2 | Series capacitance C1                              |    |

| 5.5.3 | Parallel matching capacitance C2                   |    |

| 5.6   | Receiver circuit design                            | 17 |

| 6.    | Matching Recommendations                           | 18 |

| 6.1   | Matching Recommendations for Antenna Siz           | ze |

|       | ID2                                                | 18 |

| 7.    | Legal information                                  | 20 |

| 7.1   | Definitions                                        |    |

| 7.2   | Disclaimers                                        |    |

| 7.3   | Trademarks                                         | 20 |

| 8.    | List of figures                                    | 21 |

| 9.    | List of tables                                     | 22 |

| 10.   | Contents                                           | 23 |

|       |                                                    | -  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

#### © NXP B.V. 2012.

#### All rights reserved.

For more information, visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 17 July 2012 205810 Document identifier: AN11019