1048576-Word x 8-bit / 524288-word x 16-bit CMOS Flash Memory

# HITACHI

ADE-203-537(Z) Preliminary Rev. 0.0 Jun. 14, 1996

#### Description

The Hitachi HN29WT800 Series, HN29WB800 Series are 1-Mword x 8-bit/512-kword x 16-bit CMOS Flash Memory with DINOR (D Ivided bitline NOR) type memory cells, that realize programming and erase capabilities with a single 3.3 V power supply. The built-in Sequence Controller allows Automatic Program/Erase without complex external control. HN29WT800 Series, HN29WB800 Series enable the low power and high performance systems such as mobile, personal computing and communication products.

#### Features

- On-board single power supply ( $V_{cc}$ ):  $V_{cc} = 3.3 \text{ V} \pm 0.3 \text{ V}$

- Access time: 80/100/120 ns (max)

- Low power dissipation:

- I<sub>cc</sub> = 30 mA (max) (Read)

- $I_{cc} = 200 \ \mu A \ (max) \ (Standby)$

- I<sub>CC</sub> = 40 mA (max) (Program)

- I<sub>cc</sub> = 40 mA (max) (Erase)

- $I_{cc} = 1 \ \mu A \ (typ) \ (Deep \ powerdown)$

- Automatic page programming:

- Programming time: 25 ms (typ)

- Program unit: 128 word

This product is compatible with M5M29FB/T800xx by Ltd. Mitsubishi.

Preliminary: This document contains information on a new product. Specifications and information contained herein are subject to change without notice.

- Automatic erase:

- Erase time: 50 ms (typ)

- Erase unit: Boot block; 8-kword/16-kbyte x 1

- Parameter block; 4-kword/8-kbyte x 2

- Main block; 16-kword/32-kbyte x 1

- 32-kword/64-kbyte x 15

- Block boot:

\_\_\_\_

- HN29WT800 Series: Top boot

- HN29WB800 Series: Bottom boot

- Other functions:

- Software command control

- Selective block lock

- --- Program suspend/Resume

- Erase suspend/Resume

- Status register read

- Sleep

- Compatible with M5M29FB/T800xx by Ltd. Mitsubishi

#### **Ordering Information**

| Туре No.                        | Access time     | Package                                                   |

|---------------------------------|-----------------|-----------------------------------------------------------|

| HN29WT800FP-8<br>HN29WT800FP-10 | 80 ns<br>100 ns | 44-pin plastic SOP (FP-44D)                               |

| HN29WT800FP-12                  | 120 ns          |                                                           |

| HN29WB800FP-8                   | 80 ns           |                                                           |

| HN29WB800FP-10                  | 100 ns          |                                                           |

| HN29WB800FP-12                  | 120 ns          |                                                           |

| HN29WT800T-8                    | 80 ns           | 12 x 20.0 mm <sup>2</sup> 48-pin plastic TSOP I (TFP-48D) |

| HN29WT800T-10                   | 100 ns          |                                                           |

| HN29WT800T-12                   | 120 ns          |                                                           |

| HN29WB800T-8                    | 80 ns           |                                                           |

| HN29WB800T-10                   | 100 ns          |                                                           |

| HN29WB800T-12                   | 120 ns          |                                                           |

| HN29WT800R-8                    | 80 ns           | 12 x 20.0 mm <sup>2</sup> 48-pin plastic TSOP I (Reverse) |

| HN29WT800R-10                   | 100 ns          | (TFP-48DR)                                                |

| HN29WT800R-12                   | 120 ns          |                                                           |

| HN29WB800R-8                    | 80 ns           |                                                           |

| HN29WB800R-10                   | 100 ns          |                                                           |

| HN29WB800R-12                   | 120 ns          |                                                           |

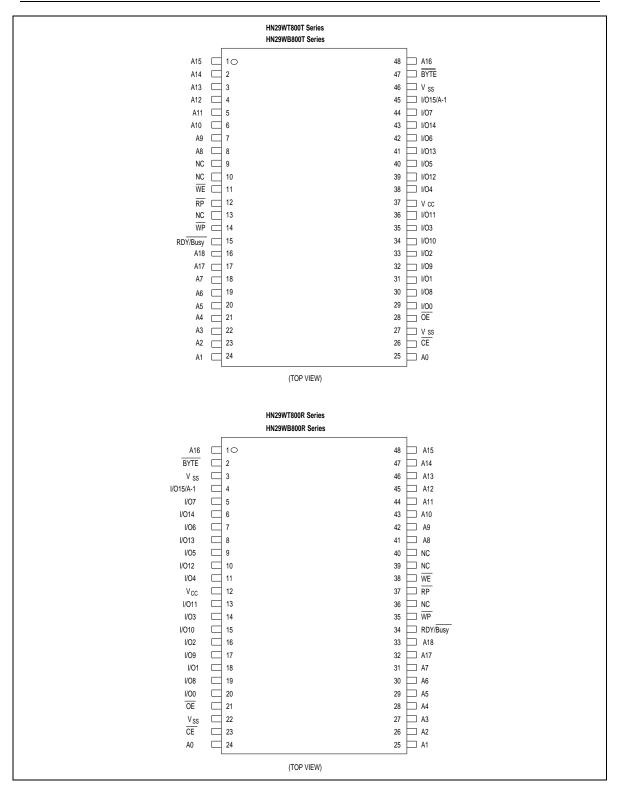

**Pin Arrangement**

| HN29WT800FP Series |                   |    |                         |  |  |  |  |  |

|--------------------|-------------------|----|-------------------------|--|--|--|--|--|

| H H                | N29WB800FP Series |    |                         |  |  |  |  |  |

|                    |                   |    | ]                       |  |  |  |  |  |

| NC 🗆               | 1                 | 44 | $\square \overline{RP}$ |  |  |  |  |  |

| A18                | 2                 | 43 |                         |  |  |  |  |  |

| A17 🗔              | 3                 | 42 | ☐ A8                    |  |  |  |  |  |

| A7 🗔               | 4                 | 41 | ☐ A9                    |  |  |  |  |  |

| A6                 | 5                 | 40 | A10                     |  |  |  |  |  |

| A5 🗌               | 6                 | 39 | ☐ A11                   |  |  |  |  |  |

| A4 🗌               | 7                 | 38 | ☐ A12                   |  |  |  |  |  |

| A3 🗆               | 8                 | 37 | ☐ A13                   |  |  |  |  |  |

| A2 🗆               | 9                 | 36 | ☐ A14                   |  |  |  |  |  |

| A1 🗔               | 10                | 35 | □ A15                   |  |  |  |  |  |

| A0 🗆               | 11                | 34 | ☐ A16                   |  |  |  |  |  |

| CE 🗆               | 12                | 33 | BYTE                    |  |  |  |  |  |

| V <sub>SS</sub>    | 13                | 32 | U V <sub>SS</sub>       |  |  |  |  |  |

| OE 🗆               | 14                | 31 | I/O15/A-1               |  |  |  |  |  |

| I/O0               | 15                | 30 | I/07                    |  |  |  |  |  |

| I/O8 🗔             | 16                | 29 | I/O14                   |  |  |  |  |  |

| I/O1 🗔             | 17                | 28 | ☐ I/O6                  |  |  |  |  |  |

| I/O9 🗔             | 18                | 27 | ☐ I/O13                 |  |  |  |  |  |

| I/O2               | 19                | 26 | I/O5                    |  |  |  |  |  |

| I/O10              | 20                | 25 | I/O12                   |  |  |  |  |  |

| I/O3 🗌             | 21                | 24 | I/O4                    |  |  |  |  |  |

| I/O11 🗔            | 22                | 23 |                         |  |  |  |  |  |

|                    | (TOP VIEW)        |    |                         |  |  |  |  |  |

|                    |                   |    |                         |  |  |  |  |  |

Pin Arrangement (cont.)

#### HITACHI

### HN29WT800 Series, HN29WB800 Series

### **Pin Description**

| Pin name        | Function        |

|-----------------|-----------------|

| A-1 to A-18     | Address         |

| I/O0 to I/O15   | Input/output    |

| CE              | Chip enable     |

| ŌĒ              | Output enable   |

| WE              | Write enable    |

| RP              | Reset/Powerdown |

| RDY/Busy        | Ready/Busy      |

| WP              | Write protect   |

| BYTE            | Byte enable     |

| V <sub>cc</sub> | Power supply    |

| V <sub>ss</sub> | Ground          |

| NC              | No connection   |

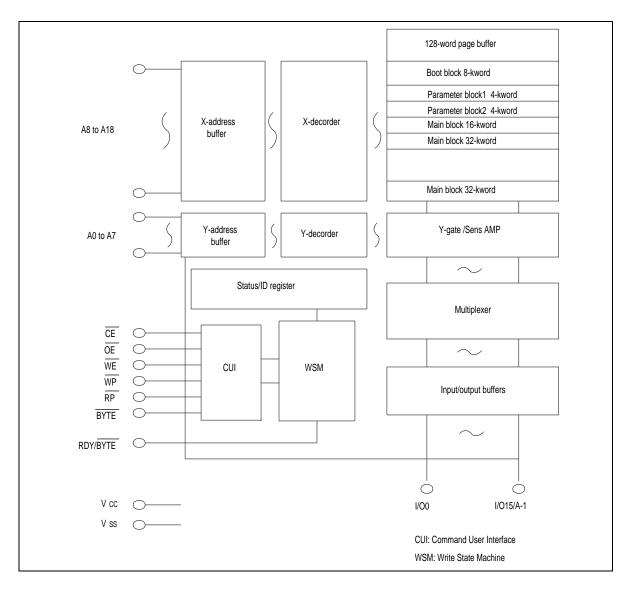

**Block Diagram**

### Memory Map

| HN29WT800 Series Mem  | ory Map                |                         | HN29WB800 S      | HN29WB800 Series Memory Map |               |                         |   |  |

|-----------------------|------------------------|-------------------------|------------------|-----------------------------|---------------|-------------------------|---|--|

| x 8 (Byte mode)       | x 16 (word mode)       |                         | x 8 (Byte mode   | i) x 16                     | 6 (word mode) |                         |   |  |

| FC000H to FFFFFH      | 7E000H to 7FFFFH       | 8-kword boot block      | F0000H to FFF    | FFH 780                     | 00H to 7FFFFH | 32-kword main block     | ] |  |

| FA000H to F8FFFH      | 7D000H to 7DFFFH       | 4-kword parameter block | E0000H to EFI    | FFH 700                     | 00H to 77FFFH | 32-kword main block     | ] |  |

| F8000H to F9FFFH      | 7C000H to 7CFFFH       | 4-kword parameter block | D0000H to DF     | FFH 680                     | 00H to 6FFFFH | 32-kword main block     | ] |  |

| F0000H to F7FFFH      | 78000H to 7BFFFH       | 16-kword main block     | C0000H to CF     | FFH 600                     | 00H to 67FFFH | 32-kword main block     | ] |  |

| E0000H to EFFFFH      | 70000H to 77FFFH       | 32-kword main block     | B0000H to BFI    | FFH 580                     | 00H to 5FFFFH | 32-kword main block     | ] |  |

| D0000H to DFFFFH      | 68000H to 6FFFFH       | 32-kword main block     | A0000H to AFI    | FFH 500                     | 00H to 57FFFH | 32-kword main block     | ] |  |

| C0000H to CFFFFH      | 60000H to 67FFFH       | 32-kword main block     | 90000H to 9FF    | FFH 480                     | 00H to 4FFFFH | 32-kword main block     | ] |  |

| B0000H to BFFFFH      | 58000H to 5FFFFH       | 32-kword main block     | 80000H to 8FF    | FFH 400                     | 00H to 47FFFH | 32-kword main block     | ] |  |

| A0000H to AFFFFH      | 50000H to 57FFFH       | 32-kword main block     | 70000H to 7FF    | FFH 380                     | 00H to 3FFFFH | 32-kword main block     | 1 |  |

| 90000H to 9FFFFH      | 48000H to 4FFFFH       | 32-kword main block     | 60000H to 6FF    | FFH 300                     | 00H to 37FFFH | 32-kword main block     | 1 |  |

| 80000H to 8FFFFH      | 40000H to 47FFFH       | 32-kword main block     | 50000H to 5FF    | FFH 280                     | 00H to 2FFFFH | 32-kword main block     | 1 |  |

| 70000H to 7FFFFH      | 38000H to 3FFFFH       | 32-kword main block     | 40000H to 4FF    | FFH 200                     | 00H to 27FFFH | 32-kword main block     | 1 |  |

| 60000H to 6FFFFH      | 30000H to 37FFFH       | 32-kword main block     | 30000H to 3FF    | FFH 180                     | 00H to 1FFFFH | 32-kword main block     | 1 |  |

| 50000H to 5FFFFH      | 28000H to 2FFFFH       | 32-kword main block     | 20000H to 2FF    | FFH 100                     | 00H to 17FFFH | 32-kword main block     | 1 |  |

| 40000H to 4FFFFH      | 20000H to 27FFFH       | 32-kword main block     | 10000H to 1FF    | FFH 080                     | 00H to 0FFFFH | 32-kword main block     | 1 |  |

| 30000H to 3FFFFH      | 18000H to 1FFFFH       | 32-kword main block     | 08000H to 0FF    | FFH 040                     | 00H to 07FFFH | 16-kword main block     | 1 |  |

| 20000H to 2FFFFH      | 10000H to 17FFFH       | 32-kword main block     | 06000H to 07F    | FFH 030                     | 00H to 03FFFH | 4-kword parameter block | 1 |  |

| 10000H to 1FFFFH      | 08000H to 0FFFFH       | 32-kword main block     | 04000H to 05F    | FFH 020                     | 00H to 02FFFH | 4-kword parameter block | 1 |  |

| 00000H to 0FFFFH      | 00000H to 07FFFH       | 32-kword main block     | 00000H to 03F    | FFH 000                     | 00H to 07FFFH | 8-kword boot block      | 1 |  |

| A-1 to 18 (Byte mode) | A 0 to A18 (Word mode) |                         | A- 1 to 18 (Byte | mode) A 0 to A18 (W         | lord mode)    |                         | , |  |

### **Mode Selection**

#### Word Mode $(\overline{BYTE} = V_{IH})$

| Mode            | Pin                      | CE              | ŌĒ              | WE              | RP               | RDY/Busy                 | I/O0 to I/O15           |

|-----------------|--------------------------|-----------------|-----------------|-----------------|------------------|--------------------------|-------------------------|

| Read            | Array                    | V               | V               | $V_{\mu}$       | $V_{\mathbb{H}}$ | V <sub>oн</sub> (High-Z) | Dout                    |

|                 | Status register          | V <sub>IL</sub> | V               | V <sub>IH</sub> | $V_{\rm IH}$     | X* <sup>5</sup>          | Status Register<br>Data |

|                 | Lock bit status          | V               | V               | $V_{\rm IH}$    | $V_{\rm IH}$     | х                        | Lock bit data (I/O6)    |

|                 | Identifier (Maker)*1,*2  | V               | V               | V <sub>IH</sub> | V <sub>IH</sub>  | V <sub>он</sub> (High-Z) | 07H                     |

|                 | Identifier (Device)*1,*3 | $V_{\rm IL}$    | $V_{\rm IL}$    | $V_{IH}$        | V <sub>IH</sub>  | V <sub>он</sub> (High-Z) | 85H/86H* <sup>6</sup>   |

| Output disable  |                          | V               | V               | V <sub>IH</sub> | V <sub>IH</sub>  | х                        | High-Z                  |

| Standby         |                          | V <sub>⊮</sub>  | х               | х               | V <sub>⊮</sub>   | х                        | High-Z                  |

| Command write*4 | Program                  | $V_{\rm IL}$    | $V_{\text{IH}}$ | V               | $V_{\rm IH}$     | х                        | Command/Data in         |

|                 | Erase                    | V               | V <sub>H</sub>  | V               | $V_{\mu}$        | х                        | Command                 |

|                 | Others                   | V               | V <sub>⊮</sub>  | V               | V <sub>⊮</sub>   | х                        | Command                 |

| Deep powerdown  |                          | х               | х               | х               | $V_{\rm IL}$     | V <sub>oн</sub> (High-Z) | High-Z                  |

Notes: 1. The command programming mode is used to output the identifier code. Refer to the table of Software Command Definition.

2. A0 = V<sub>IL</sub>

3. A0 = V<sub>IH</sub>

- 4. Refer to the table of Software Command Definition. Programming and erase operation begins after mode setting by command input.

- 5. x can be  $V_{IL}$  or  $V_{IH}$  for control pins, and  $V_{OL}$  or  $V_{OH}$  (High-Z) for RDY/Busy pin. The RDY/Busy is an open drain output pin and indicates status of the internal WSM. When low, it indicates the WSM is Busy performing an operation. A pull-up resistor of 10 k to 100 k $\Omega$  is required to allow the RDY/Busy signal to transition high indicating a Ready WSM condition.

6. 85H: HN29WT800 Series, 86H: HN29WB800 Series.

| Mode            | Pin                      | CE               | ŌĒ               | WE              | RP                | RDY/Busy                 | I/O0 to I/O7            |

|-----------------|--------------------------|------------------|------------------|-----------------|-------------------|--------------------------|-------------------------|

| Read            | Array                    | $V_{\rm L}$      | V                | $V_{_{H}}$      | V <sub>⊮</sub>    | V <sub>он</sub> (High-Z) | Dout                    |

|                 | Status register          | V <sub>IL</sub>  | $V_{IL}$         | $V_{\text{IH}}$ | $V_{\rm IH}$      | X* <sup>5</sup>          | Status Register<br>Data |

|                 | Lock bit status          | V <sub>IL</sub>  | V                | V <sub>IH</sub> | $V_{\rm IH}$      | х                        | Lock bit data<br>(I/O6) |

|                 | Identifier (Maker)*1,*2  | V                | $V_{\rm IL}$     | $V_{\rm IH}$    | V <sub>IH</sub>   | V <sub>он</sub> (High-Z) | 07H                     |

|                 | Identifier (Device)*1,*3 | V                | V                | V               | V <sub>IH</sub>   | V <sub>он</sub> (High-Z) | 85H/86H*6               |

| Output disable  |                          | $V_{\rm IL}$     | $V_{IH}$         | $V_{IH}$        | V <sub>IH</sub> x | High-Z                   |                         |

| Standby         |                          | $V_{\mathbb{H}}$ | х                | х               | V <sub>⊮</sub>    | Х                        | High-Z                  |

| Command write*4 | Program                  | $V_{\rm IL}$     | $V_{IH}$         | V               | V <sub>IH</sub>   | Х                        | Command/Data in         |

|                 | Erase                    | V                | $V_{\mathbb{H}}$ | V <sub>⊾</sub>  | V <sub>IH</sub>   | Х                        | Command                 |

|                 | Others                   | V <sub>⊾</sub>   | $V_{\mathbb{H}}$ | V <sub>⊾</sub>  | V <sub>⊮</sub>    | Х                        | Command                 |

| Deep powerdown  |                          | х                | х                | х               | V                 | V <sub>он</sub> (High-Z) | High-Z                  |

#### $\overline{BYTE}$ Mode ( $\overline{BYTE} = V_{II}$ )

Notes: 1. The command programming mode is used to output the identifier code. Refer to the table of Software Command Definition.

2. A0 = V<sub>II</sub>

3. A0 = V<sub>⊪</sub>

4. Refer to the table of Software Command Definition. Programming and erase operation begins after mode setting by command input.

5. x can be  $V_{IL}$  or  $V_{OH}$  for control pins, and  $V_{OL}$  or  $V_{OH}$  (High-Z) for RDY/Busy pin. The RDY/Busy is an open drain output pin and indicates status of the internal WSM. When low, it indicates the WSM is Busy performing an operation. A pull-up resistor of 10 k to 100 k $\Omega$  is required to allow the RDY/Busy signal to transition high indicating a Ready WSM condition.

6. 85H: HN29WT800 Series, 86H: HN29WB800 Series.

#### **Software Command Definition**

|                                 | First bus cycle        |         |                                         | Second bu         | s cycle          |                           | Third bus cycle   |         |                           |  |

|---------------------------------|------------------------|---------|-----------------------------------------|-------------------|------------------|---------------------------|-------------------|---------|---------------------------|--|

| Command                         | Oper-<br>ation<br>mode | Address | Data<br>(I/O7<br>to I/O0)* <sup>1</sup> | Operation<br>mode | Address          | Data<br>(I/O7<br>to I/O0) | Operation<br>mode | Address | Data<br>(I/O7<br>to I/O0) |  |

| Read array<br>(memory)          | Write                  | х       | FFH                                     |                   |                  |                           |                   |         |                           |  |

| Read<br>identifier<br>codes     | Write                  | x       | 90H                                     | Read              | IA* <sup>2</sup> | ID* <sup>2</sup>          |                   |         |                           |  |

| Read status register            | Write                  | х       | 70H                                     | Read              | x                | SRD* <sup>3</sup>         |                   |         |                           |  |

| Clear status register           | Write                  | х       | 50H                                     |                   |                  |                           |                   |         |                           |  |

| Page<br>program*⁵               | Write                  | х       | 41H                                     | Write             | WA0*4            | WD0*4                     | Write             | WA1     | WD1                       |  |

| Block erase                     | Write                  | х       | 20H                                     | Write             | BA* <sup>6</sup> | D0H                       |                   |         |                           |  |

| Suspend                         | Write                  | х       | B0H                                     |                   |                  |                           |                   |         |                           |  |

| Resume                          | Write                  | х       | D0H                                     |                   |                  |                           |                   |         |                           |  |

| Read lock<br>bit status         | Write                  | х       | 71H                                     | Read              | BA               | I/O6*7                    |                   |         |                           |  |

| Lock bit<br>program/co<br>nfirm | Write                  | x       | 77H                                     | Write             | BA               | D0H                       |                   |         |                           |  |

| Erase all<br>unlocked<br>blocks | Write                  | x       | A7H                                     | Write             | x                | D0H                       |                   |         |                           |  |

| Sleep*8                         | Write                  | х       | F0H                                     |                   |                  |                           |                   |         |                           |  |

Notes: 1. In the word mode, upper byte data (I/O8 to I/O15) is ignored.

2. IA = Identifier address, A0 =  $V_{\parallel}$  (Manufacture code), A0 =  $V_{\parallel}$  (Device code), ID = ID code,  $\overline{\text{BYTE}}$ =  $V_{\parallel}$ : A-1, A1 to A18 =  $V_{\parallel}$ ,  $\overline{\text{BYTE}}$  =  $V_{\parallel}$ : A1 to A18 =  $V_{\parallel}$ .

3. SRD = Status register data

4. WA = Write address, WD = Write data

BYTE = V<sub>µ</sub>: Write address and write data must be provided sequentially from 00H to FFH for A-1 to A6. Page size is 256 byte (256-byte x 8-bit).

BYTE = V<sub>IH</sub>: Write address and write data must be provided sequentially from 00H to 7FH for A0 to A6. Page size is 128 word (128-word x 16-bit).

6. BA = Block address (A16 to A20), (Addresses except block address must be  $V_{\mu}$ )

7. I/O6 provides block lock status, I/O6 = 1: Block unlocked, I/O6 = 0: Block locked.

Sleep command (F0H) put the device into the sleep mode after completing the current operation. The active current is reduced to deep powerdown levels. The Read Array command (FFH) must be written to get the device out of sleep mode.

#### Block Locking (TSOP package)

| RP               | WP                                  | Lock bit (internally) | Write protection provided                 |

|------------------|-------------------------------------|-----------------------|-------------------------------------------|

| $V_{\rm L}$      | Х                                   | Х                     | All blocks locked (Deep powerdown mode)   |

| $V_{_{\!H\!H}}$  | х                                   | Х                     | All blocks unlocked                       |

| $V_{\mathbb{H}}$ | $V_{\mathbb{L}}$                    | 0                     | Blocks locked (Depend on lock bit data)   |

| V <sub>IH</sub>  | V                                   | 1                     | Blocks unlocked (Depend on lock bit data) |

| $V_{H}$          | $V_{\scriptscriptstyle \mathbb{H}}$ | Х                     | All blocks unlocked                       |

Note: I/O6 provided lock status of each block after writing the Read lock status command (71H). WP pin must not be switched during performing Read/Write operations or WSM busy (WSMS = 0).

#### Block Locking (SOP package)

| RP               | Lock bit (internally) | Write protection provided                 |

|------------------|-----------------------|-------------------------------------------|

| $V_{\rm L}$      | Х                     | All blocks locked (Deep powerdown mode)   |

| $V_{\rm HH}$     | х                     | All blocks unlocked                       |

| V <sub>IH</sub>  | 0                     | Blocks locked (Depend on lock bit data)   |

| $V_{\mathbb{H}}$ | 1                     | Blocks unlocked (Depend on lock bit data) |

|                  |                       |                                           |

Note: I/O6 provided lock status of each block after writing the Read lock status command (71H).

#### Status Register Data (SRD)

| Symbol       | Function                   | Definition                                                                      |                                     |  |  |

|--------------|----------------------------|---------------------------------------------------------------------------------|-------------------------------------|--|--|

| SR. 7 (I/O7) | Write state machine status | 1 = Ready                                                                       | 0 = Busy                            |  |  |

| SR. 6 (I/O6) | Suspend status             | 1 = Suspend                                                                     | 0 = Operation in progress/completed |  |  |

| SR. 5 (I/O5) | Erase status               | 1 = Error                                                                       | 0 = Successful                      |  |  |

| SR. 4 (I/O4) | Program status             | 1 = Error                                                                       | 0 = Successful                      |  |  |

| SR. 3 (I/O3) | Block status after program | 1 = Error                                                                       | 0 = Successful                      |  |  |

| SR. 2 (I/O2) | Reserved                   | The function and the definition for these bits are to be                        |                                     |  |  |

| SR. 1 (I/O1) | Reserved                   | determined. These bits should be masked out when the sta<br>register is polled. |                                     |  |  |

| SR. 0 (I/O0) | Device sleep status        | 1 = Device in sleep                                                             | 0 = Device not in sleep             |  |  |

Note: The RDY/Busy is an open dran output pin and indicates status of the internal WSM. When low, it indicates that the WSM is Busy performing an operation. A pull-up resistor of 10kΩ to 100kΩ is required to allow the RDY/Busy signal to transition high indicating a Ready WSM condition.

I/O3 indicates the block status after the page programming. When I/O3 is High, the page has the over-programmed cell. If over-program occures, the device is block failed. However, if I/O3 is High, please try the block erase to the block. The block may revive.

#### **Device Identifier Mode**

The device identifier mode allows the reading out of binary codes that identify manufacturer and type of device, from outputs of Flash Memory. By this mode, the device will be automatically matched its own corresponding erase and programming algorithm.

| Pins                   | <b>A0</b> | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 | Hex. data |

|------------------------|-----------|------|------|------|------|------|------|------|------|-----------|

| Manufacturer code      | 0         | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 07H       |

| Device code (T series) | 1         | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 85H       |

| Device code (B series) | 1         | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 86H       |

HN29WT800 Series, HN29WB800 Series Identifier Code

Notes: 1. Device identifier code can be read out by using the read identified codes command.

2. In the word mode, the same data as I/O7 to I/O0 is read out from I/O15 to I/O8.

3. A9 =  $V_{HH}$  mode. A9 = 11.5 V to 13.0 V. Set A9 to  $V_{HH}$  min 200 ns before falling edge of  $\overline{CE}$  in ready status. Min 200 ns after return to V<sub>HH</sub>, device can't be accessed. A1 to A8, A10 to A18,  $\overline{CE}$ ,  $\overline{OE}$ , = V<sub>1</sub>, WE = V<sub>14</sub>, I/O15/A-1 = V<sub>1</sub> ( $\overline{BYTE}$  = L).

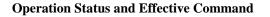

#### **Operations of the HN29WT800 Series, HN29WB800 Series**

The HN29WT800 Series, HN29WB800 Series include on-chip program/erase control circuitry. The Write State Machine (WSM) controls block erase and page program operations. Operational modes are selected by the commands written to the Command User Interface (CUI). The Status Register indicates the status of the WSM and when the WSM successfully completes the desired program or block erase operation. A Deep Powerdown mode is enabled when the  $\overline{\text{RP}}$  pin is at  $V_{ss}$  minimizing power consumption.

Read: The HN29WT800 Series, HN29WB800 Series have three read modes, which accesses to the memory array, the Device Identifier and the Status Register. The appropriate read command are required to be written to the CUI. Upon initial device powerup or after exit from deep powerdown, the HN29WT800 Series, HN29WB800 Series automatically reset to read array mode. In the read array mode, low level input to CE and  $\overline{OE}$ , high level input to  $\overline{WE}$  and  $\overline{RP}$ , and address signals to the address inputs (A0 to A18) output the data of the addressed location to the data input/output (I/O0 to I/O15).

Write: Writes to the CUI enable reading of memory array data, device identifiers and reading and clearing of the Status Register, they also enable block erase and program. The CUI is written by bringing  $\overline{WE}$  to low level, while CE is at low level and OE is at high level. Addresses and data are latched on the earlier rising edge of WE and CE. Standard micro-processor write timings are used.

**Output Disable:** When  $\overline{OE}$  is at  $V_{IH}$  output from the device is disabled. Data input/output are in a high impedance (High-Z) state.

**Standby:**When  $\overline{CE}$  is at  $V_{\text{IH}}$ , the device is in the standby mode and its power consumption is reduced. Data input/output are in a high impedance (High-Z) state. If the memory is deselected during block erase or program, the internal control circuits remain active and the device consume normal active power until the operation completes.

**Deep Powerdown:** When  $\overline{\text{RP}}$  is at  $V_{IL}$ , the device is in the deep powerdown mode and its power consumption is substantially low. During read modes, the memory is deselected and the data input/output are in a high impedance (High-Z) state. After return from powerdown, the CUI is reset to Read Array and the Status Register is cleared to value 80H. During block erase or program modes,  $\overline{\text{RP}}$  low will abort either operation. Memory array data of the block being altered become invalid.

#### **Functional Description**

The device operations are selected by writing specific software command into the CUI.

**Read Array Command (FFH):** The device is in read array mode on initial device power up and after exit from deep power down, or by writing FFH to the CUI. The device remains in Read Array mode until the other commands are written.

**Read Device Identifier Command (90H):**Though PROM programmers can normally read device identifier codes by raising A9 to high voltage, multiplexing high voltage onto address lines is not desired for microprocessor system. It is an other means to read device identifier codes that Read Device Identifier Code Command (90H) is written to the command latch. Following the write of the Read Device Identifier command of 90H, the manufacturer code and the device code can be read from addresses 00000H and 00001H, respectively.

**Read Status Register Command (70H):** The Status Register is read after writing the read status register command of 70H to the CUI. The contents of Status Register are latched on the later falling edge of  $\overline{OE}$  or  $\overline{CE}$ . So  $\overline{CE}$  or  $\overline{OE}$  must be toggled every status read.

**Clear Status Register Command (50H):** The Erase Status and Program Status bits are set to High by the Write State Machine and can be reset by the Clear Status Register command of 50H. These bits indicates various failure conditions.

**Block Erase/Confirm Command (20H/D0H):** Automated block erase is initiated by writing the Block Erase of 20H followed by the Confirm command of D0H. An address within the block to be erased is required. The WSM executes iterative erase pulse application and erase verify operation.

**Suspend/Resume Command (B0H/D0H):** Writing the suspend command of B0H during block erase operation interrupts the block erase operation and allows read out from another block of memory. Writing the suspend command of B0H during program operation interrupts the program operation and allows read out from another block of memory. The device continues to output status register data when read, after the suspend command is written to it. Polling the WSM status and suspend status bits will determine when the erase operation or program operation has been suspended. At this point, writing of the read array command to the CUI enables reading data from blocks other than that which is suspended. When the resume command of D0H is written to the CUI, the WSM will continue with the erase or program processes.

**Page Program Command (41H):** Page program allows fast programming of 128-word of data. Writing of 41H initiates the page program operation. From 2nd cycle to 129th cycle write data must be serially inputted. Address A6 to A0 have to be incremented from 00H to 7FH. After completion of data loading, the WSM controls the program pulse application and verify operation. Basically re-program must not be done on a page which has already programmed.

**Data Protection:** The HN29WT800 Series, HN29WT800 Series provide selective block locking of memory blocks. Each block has an associated nonvolatile lock-bit which determines the lock status of the block. In addition, the HN29WT800 Series, HN29WT800 Series have a master write protect pin ( $\overline{WP}$ ) which prevents any modifications to memory blocks whose lock-bits are set to Low, when  $\overline{WP}$  is low. When  $\overline{WP}$  is high or  $\overline{RP}$  is  $V_{\text{HH}}$ , all blocks can be programmed or erased regardless of the state of lock-bits, and the lock-bits are cleared to High by erase.

**Power Supply Voltage:** When the power supply voltage ( $V_{cc}$ ) is less than 2.2 V, the device is set to the Readonly mode. A delay time of 2 µs is required before any device operation is initiated. The delay time is measured from the time  $V_{cc}$  reaches  $V_{cc}$  min (3.0 V). During powerup,  $\overline{RP} = V_{ss}$  is recommended. Falling in Busy status is not recommended for possibility of damaging the device.

| Parameter                                                                  | Symbol                     | Value         | Unit | Notes |

|----------------------------------------------------------------------------|----------------------------|---------------|------|-------|

| V <sub>cc</sub> voltage                                                    | V <sub>cc</sub>            | -0.2 to +4.6  | V    | 1     |

| All input and output voltages except $V_{\rm cc},$ A9, $\overline{\rm RP}$ | Vin, Vout                  | -0.6 to +4.6  | V    | 1, 2  |

| A9, RP supply voltage                                                      | $V_{_{\!H\!H}},V_{_{\!D}}$ | -0.6 to +14.0 | V    | 1, 2  |

| Operating temperature range                                                | Topr                       | 0 to +70      | °C   |       |

| Storage temperature range                                                  | Tstg                       | -65 to +125   | °C   |       |

| Storage temperature under bias                                             | Tbias                      | -10 to +80    | °C   |       |

#### Absolute Maximum Ratings

Notes: 1. Relative to V<sub>ss</sub>.

2. Minimum DC voltage is -0.5 V on input/output pins. During transition, this level may undershoot to -2.0 V for periods < 20 ns. Maximum DC voltage on input/output pins are V<sub>cc</sub> +0.5 V which, during transitions, may overshoot to V<sub>cc</sub> +1.5 V for periods < 20 ns.

| Parameter          | Symbol | Min | Тур | Max | Unit | Test conditions |

|--------------------|--------|-----|-----|-----|------|-----------------|

| Input capacitance  | Cin    |     |     | 8   | pF   | Vin = 0 V       |

| Output capacitance | Cout   | _   | _   | 12  | pF   | Vout = 0 V      |

#### Capacitance (Ta = $25^{\circ}$ C, f = 1 MHz)

#### DC Characteristics ( $V_{cc} = 3.3 \text{ V} \pm 0.3 \text{ V}$ , Ta = 0 to +70°C)

| Parameter                                   | Symbol           | Min                       | Тур  | Мах      | Unit | Test conditions                                                                                        |

|---------------------------------------------|------------------|---------------------------|------|----------|------|--------------------------------------------------------------------------------------------------------|

| Input leakage current                       | I <sub>LI</sub>  | -1                        | _    | 1        | μΑ   | $Vin = V_{ss} to V_{cc}$                                                                               |

| Output leakage current                      | I <sub>LO</sub>  | -10                       | _    | 10       | μA   | Vout = $V_{ss}$ to $V_{cc}$                                                                            |

| Standby $V_{cc}$ current                    | I <sub>SB1</sub> | —                         | 50   | 200      | μΑ   | $Vin = V_{\mu}/V_{\mu} \overline{CE} = \overline{RP} = \overline{WP} = V_{\mu}$                        |

|                                             | I <sub>SB2</sub> | —                         | 1    | 5        | μA   | $Vin = V_{ss} \text{ or } V_{cc},$                                                                     |

|                                             |                  |                           |      |          |      | $\overline{\text{CE}} = \overline{\text{RP}} = \overline{\text{WP}} = V_{\text{cc}} \pm 0.3 \text{ V}$ |

| Deep powerdown $V_{cc}$ current             | I <sub>SB3</sub> | —                         | 5    | 15       | μΑ   | $Vin = V_{IH} V_{IL}, \ \overline{RP} = V_{IL}$                                                        |

|                                             | I <sub>SB4</sub> | _                         | 1    | 5        | μA   | Vin = $V_{ss}$ or $V_{cc}$ , $\overline{RP} = V_{ss} \pm 0.3 V$                                        |

| Read V <sub>cc</sub> current                | I <sub>CC1</sub> | —                         | 7    | 30       | mA   | $Vin = V_{IH}/V_{IL}, \ \overline{CE} = V_{IL},$                                                       |

|                                             |                  |                           |      |          |      | $\overline{\text{RP}} = \overline{\text{OE}} = V_{\mu}, f = 10 \text{ Mhz},$                           |

|                                             |                  |                           |      |          |      | lout = 0 mA                                                                                            |

| Write V <sub>cc</sub> current               | I <sub>CC2</sub> | _                         |      | 30       | mΑ   | $Vin = V_{IH}/V_{IL}, \ \overline{CE} = \overline{WE} = V_{IL},$                                       |

|                                             |                  |                           |      |          |      | $\overline{RP} = \overline{OE} = V_{IH}$                                                               |

| Programming $V_{cc}$ current                | I <sub>CC3</sub> | _                         |      | 40       | mΑ   | $Vin = V_{IH} / V_{IL}, \ \overline{CE} = \overline{RP} = \overline{WP} = V_{IH}$                      |

| Erasing $V_{cc}$ current                    | I <sub>CC4</sub> | —                         | —    | 40       | mΑ   | $Vin = V_{IH}/V_{IL}, \ \overline{CE} = \overline{RP} = \overline{WP} = V_{IH}$                        |

| Suspend V <sub>cc</sub> current             | I <sub>CC5</sub> | _                         |      | 200      | μA   | $Vin = V_{IH}/V_{IL}, \ \overline{CE} = \overline{RP} = \overline{WP} = V_{IH}$                        |

| RP all block unlocked current               | I <sub>RP</sub>  | _                         |      | 100      | μA   | RP = V <sub>HH</sub> max                                                                               |

| A9 intelligent identifier voltage           | I <sub>ID</sub>  | _                         | _    | 100      | μA   | $A9 = V_{iD}max$                                                                                       |

| A9 intelligent identifier voltage           | V <sub>ID</sub>  | 11.4                      | 12.0 | 12.6     | V    |                                                                                                        |

| RP unlocked voltage                         | V <sub>HH</sub>  | 11.4                      | 12.0 | 12.6     | V    |                                                                                                        |

| Input voltage                               | V                | -0.5                      |      | 0.8      | V    |                                                                                                        |

|                                             | V <sub>IH</sub>  | 2.0                       | _    | $V_{cc}$ | V    |                                                                                                        |

|                                             |                  |                           |      | +<br>0.5 |      |                                                                                                        |

| Output voltage                              | V <sub>ol</sub>  |                           |      | 0.45     | V    | I <sub>oL</sub> = 5.8 mA                                                                               |

| Output voltage                              |                  | 0.85                      |      | 0.40     | V    | $I_{0L} = -2.5 \text{ mA}$                                                                             |

|                                             | V <sub>oh1</sub> | 0.85<br>x V <sub>cc</sub> |      | _        | v    | и <sub>он</sub> – -2.5 ША                                                                              |

|                                             | V <sub>OH2</sub> | V <sub>cc</sub> -<br>0.4  | -    |          | V    | I <sub>OH</sub> = -100 μA                                                                              |

| Low $V_{cc}$ lock-out voltage* <sup>2</sup> | V                | 1.5                       |      | 2.5      | V    |                                                                                                        |

Notes: 1. All currents are RMS unless otherwise noted. Typical values at  $V_{cc}$ = 3.3 V, Ta = 25°C.

2. To protect initiation of write cycle during  $V_{cc}$  powerup/powerdown, a write cycle is locked out for  $V_{cc}$  less than  $V_{LKO}$  If  $V_{cc}$  is less than  $V_{LKO}$  Write State Machine is reset to read mode. When the Wirte State Machine is in Busy state, if  $V_{cc}$  is less than  $V_{LKO}$ , the alternation of memory contents may occur.

#### AC Characteristics ( $V_{cc} = 3.3 \text{ V} \pm 0.3 \text{ V}$ , Ta = 0 to + 70°C)

#### **Test Conditions**

- Input pulse levels:  $V_{IL} = 0 V$ ,  $V_{IH} = 3.0 V$

- Input rise and fall time  $:\leq 10 \text{ ns} (\text{HN29WT/WB800-10/12 Series})$

- :  $\leq 5 \text{ ns} (\text{HN29WT/WB800-8 Series})$

- Output load : 1 TTL gate + 50 pF (Including scope and jig.) (HN29WT/WB800-10/12 Series)

- : 1 TTL gate + 30 pF (Including scope and jig.) (HN29WT/WB800-8 Series)

- Reference levels for measuring timing: 1.5 V

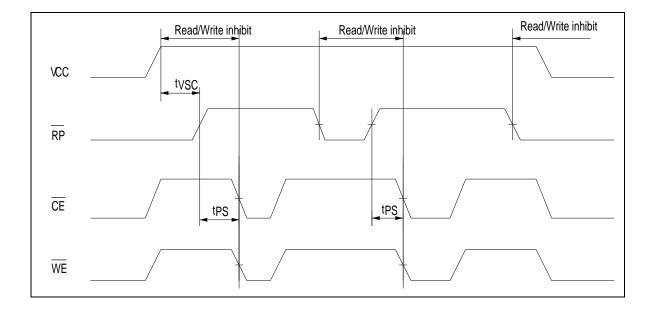

#### V<sub>cc</sub> Powerup/Powerdown Timing

| Parameter                                                        | Symbol           | Min        | Тур            | Max           | Unit                  |

|------------------------------------------------------------------|------------------|------------|----------------|---------------|-----------------------|

| $RP = V_{{}_{\rm I\!H}}$ setup time from $V_{{}_{\rm C\!C}}$ min | t <sub>vcs</sub> | 2          | _              | —             | μs                    |

| Note: During powerup/powerdown                                   | , by the noise   | e pulses c | on control pir | ns, the devid | ce has possibility of |

accidental erasure or programming. The device must be protected against initiation of write cycle for memory contents during powerup/powerdown. The delay time of min 2 µs is always required before read operation or write operation is initiated from the time  $V_{cc}$  reaches  $V_{cc}$  min during powerup/powerdown. By holding RP  $V_{\mu}$ , the contents of memory is protected during  $V_{cc}$ powerup/powerdown. During powerup, RP must be held  $V_{\mu}$  for min 2 µs from the time  $V_{cc}$  reaches  $V_{cc}$  min. During powerdown, RP must be held  $V_{\mu}$  until  $V_{cc}$  reaches  $V_{ss}$ . RP doesn't have latch mode, so RP must be held  $V_{\mu}$  during read operation or erase/program operation.

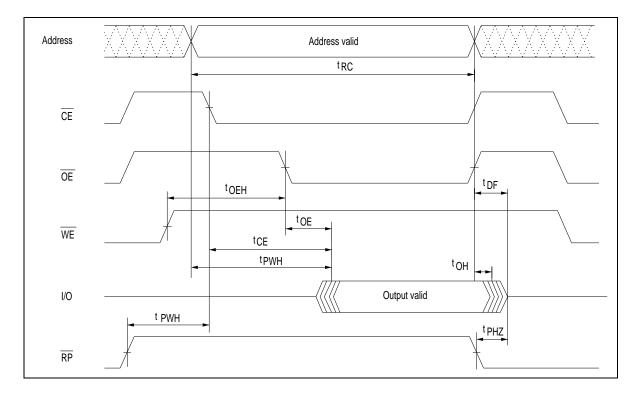

#### **Read Operation**

|                                                              |                   | HN29 | WT800 | /HN29V | VB800 |     |     |      |

|--------------------------------------------------------------|-------------------|------|-------|--------|-------|-----|-----|------|

|                                                              |                   | -8   |       | -10    |       | -12 |     |      |

| Parameter                                                    | Symbol            | Min  | Max   | Min    | Max   | Min | Max | Unit |

| Read cycle time                                              | t <sub>RC</sub>   | 80   | —     | 100    |       | 120 |     | ns   |

| Address to output delay                                      | t <sub>ACC</sub>  | _    | 80    |        | 100   | _   | 120 | ns   |

| CE to output delay                                           | t <sub>ce</sub>   | _    | 80    | —      | 100   | _   | 120 | ns   |

| OE to output delay                                           | t <sub>oe</sub>   | _    | 40    | _      | 50    | _   | 60  | ns   |

| RP access time                                               | t <sub>RP</sub>   | _    | 300   | _      | 300   | _   | 600 | ns   |

| $\overline{CE}$ or $\overline{OE}$ high to output float*1    | t <sub>DF</sub>   | —    | 25    | —      | 25    | _   | 30  | ns   |

| Address to output hold                                       | t <sub>он</sub>   | 0    | _     | 0      | _     | 0   | _   | ns   |

| $\overline{\text{OE}}$ hold from $\overline{\text{WE}}$ high | t <sub>oeh</sub>  | 80   | —     | 100    | _     | 120 | _   | ns   |

| Status register read in busy                                 |                   |      |       |        |       |     |     |      |

| $\overline{\text{OE}}$ hold from $\overline{\text{WE}}$ high | t <sub>oeh</sub>  | 0    | _     | 0      | _     | 0   | _   | ns   |

| Other read                                                   |                   |      |       |        |       |     |     |      |

| RP recovery time before read                                 | t <sub>PWH</sub>  | 0    | _     | 0      | _     | 0   |     | ns   |

| RP low to output High-Z                                      | t <sub>PHZ</sub>  |      | 150   | —      | 150   | _   | 300 | ns   |

| $\overline{CE}$ low to $\overline{BYTE}$ high or low         | t <sub>BCD</sub>  | —    | 5     | —      | 5     | —   | 5   | ns   |

| Address to BYTE high or low                                  | t <sub>BAD</sub>  | _    | 5     |        | 5     | —   | 5   | ns   |

| BYTE to output delay                                         | t <sub>BYTE</sub> | _    | 80    |        | 100   | —   | 120 | ns   |

| BYTE low to output High-Z                                    | t <sub>BHZ</sub>  | —    | 25    | _      | 25    | _   | 30  | ns   |

Notes: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

2. Timing measurements are made under read timing waveform.

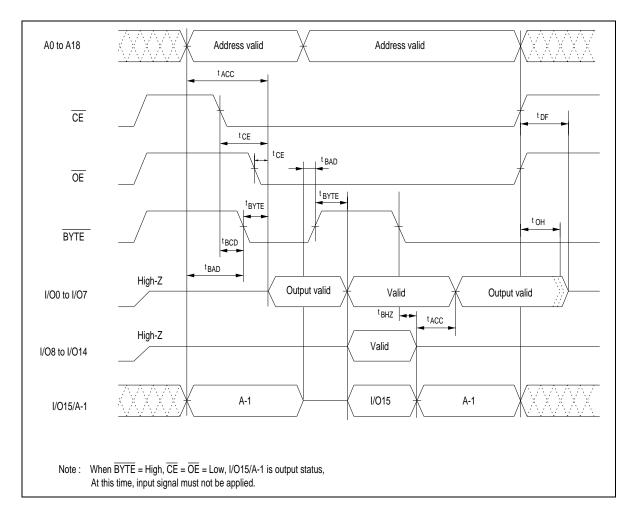

Read Timing Waveform (Byte Mode or Word Mode)

### Read Timing Waveform (Byte Mode, Word Mode Switch)

### **Command Write Operation**

|                                       |                     | HN29 | WT800 | /HN29V | VB800 |     |     |     |     |     |      |

|---------------------------------------|---------------------|------|-------|--------|-------|-----|-----|-----|-----|-----|------|

|                                       |                     | -8   |       |        | -10   |     |     | -12 |     |     |      |

| Parameter                             | Symbol              | Min  | Тур   | Max    | Min   | Тур | Max | Min | Тур | Мах | Unit |

| Write cycle time                      | t <sub>wc</sub>     | 80   |       |        | 100   |     |     | 120 |     |     | ns   |

| Address setup time                    | t <sub>AS</sub>     | 50   | —     |        | 50    | _   |     | 50  |     |     | ns   |

| Address hold time                     | t <sub>AH</sub>     | 10   | —     | _      | 10    | _   | _   | 10  |     |     | ns   |

| Data setup time                       | t <sub>DS</sub>     | 50   | _     | _      | 50    | _   | _   | 50  | _   | _   | ns   |

| Data hold time                        | t <sub>DH</sub>     | 10   | —     | —      | 10    | _   |     | 10  |     | —   | ns   |

| CE setup time                         | t <sub>cs</sub>     | 0    | —     | —      | 0     | _   |     | 0   |     |     | ns   |

| CE hold time                          | t <sub>ch</sub>     | 0    | —     |        | 0     | _   |     | 0   |     |     | ns   |

| Write pulse width                     | t <sub>wP</sub>     | 60   | _     | _      | 60    |     |     | 60  |     | _   | ns   |

| Write pulse high time                 | t <sub>wph</sub>    | 20   | _     |        | 20    |     |     | 20  |     |     | ns   |

| WE setup time                         | t <sub>ws</sub>     | 0    | —     | —      | 0     | _   |     | 0   |     |     | ns   |

| WE hold time                          | t <sub>wH</sub>     | 0    | —     | —      | 0     | _   |     | 0   |     |     | ns   |

| CE pulse width                        | t <sub>CEP</sub>    | 60   | _     | _      | 60    |     |     | 60  |     | _   | ns   |

| CE pulse high time                    | t <sub>CEPH</sub>   | 20   | —     | —      | 20    | _   |     | 20  |     | —   | ns   |

| Duration of program operation         | t <sub>DAP</sub>    | _    | 25    | 120    | _     | 25  | 120 | _   | 25  | 120 | ms   |

| Duration of block erase operation     | t <sub>DAE</sub>    | _    | 50    | 600    |       | 50  | 600 | _   | 50  | 600 | ms   |

| BYTE high or low setup time           | t <sub>BS</sub>     | 50   | _     |        | 50    |     |     | 50  |     |     | ns   |

| BYTE high or low hold time            | t <sub>BH</sub>     | 80   | _     | _      | 100   |     |     | 120 |     | _   | ns   |

| RP high recovery to WE low            | t <sub>PS</sub>     | 500  | —     | —      | 500   | _   |     | 500 |     | —   | ns   |

| Block lock setup to write enable high | t <sub>BLS</sub>    | 80   | _     | _      | 100   |     | _   | 120 | —   | —   | ns   |

|                                       | t <sub>wps</sub>    | 80   | _     | _      | 100   |     |     | 120 |     | _   | ns   |

| Block lock hold from valid SRD        | t <sub>BLH</sub>    | 0    | —     | —      | 0     | _   | —   | 0   | —   | _   | ns   |

|                                       | t <sub>wph</sub>    | 0    | _     | _      | 0     |     | _   | 0   | _   | _   | ns   |

| WE high to RDY/Busy low               | $\mathbf{t}_{WHRL}$ | _    | _     | 80     | _     |     | 100 |     |     | 120 | ns   |

| CE high to RDY/Busy low               | t <sub>ehrl</sub>   |      |       | 80     |       |     | 100 |     |     | 120 | ns   |

Note: Read operation parameters during command write operations mode are the same as during read timing waveform. Typical values at  $V_{cc}$  = 3.3 V, Ta = 25°C.

#### **Erase and Program Performance**

| Parameter                        | Min | Тур | Max  | Unit |  |

|----------------------------------|-----|-----|------|------|--|

| Main block write time (Page mode | —   | 6.4 | 38.4 | S    |  |

| Page write time                  | _   | 25  | 120  | ms   |  |

| Block erase time                 | _   | 50  | 600  | ms   |  |

Note: Typical values at V<sub>cc</sub> = 3.3 V, Ta = 25 C. These values exclude system level overhead.

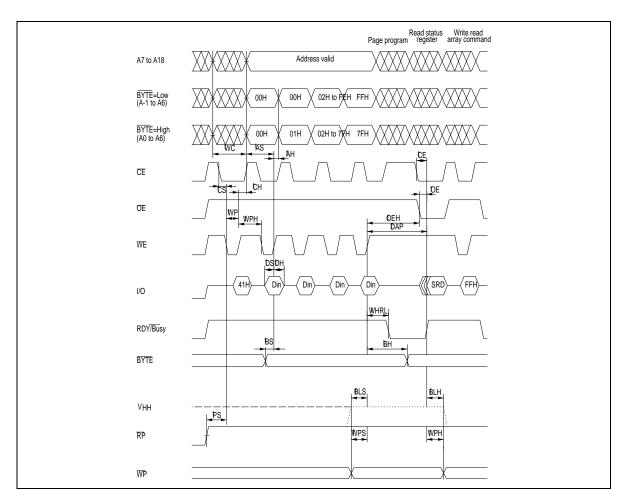

### Page Program Timing Waveform (WE control)

Read status Write read array command Page program register A7 to A18 Address valid BYTE=Low (A-1 to A6) 02H to FEH 01H FFH 00H BYTE=High 00H 01H 02H to 7FH 7FH (A0 to A6) tAS tWC t AH tC CE <sup>t</sup>CEPH tOE ŌE t wh <sup>t</sup>OEH t DAP tws  $\overline{\mathsf{WE}}$ t DS tDH 41H Din Din Din SRD FFH Din I/O <sup>t</sup>EHRL RDY/Busy tBS t<sub>BH</sub> BYTE t BLH t BLS V <sub>HH</sub> RP twps tWPH  $\overline{\mathsf{WP}}$

### Page Program Timing Waveform (CE control)

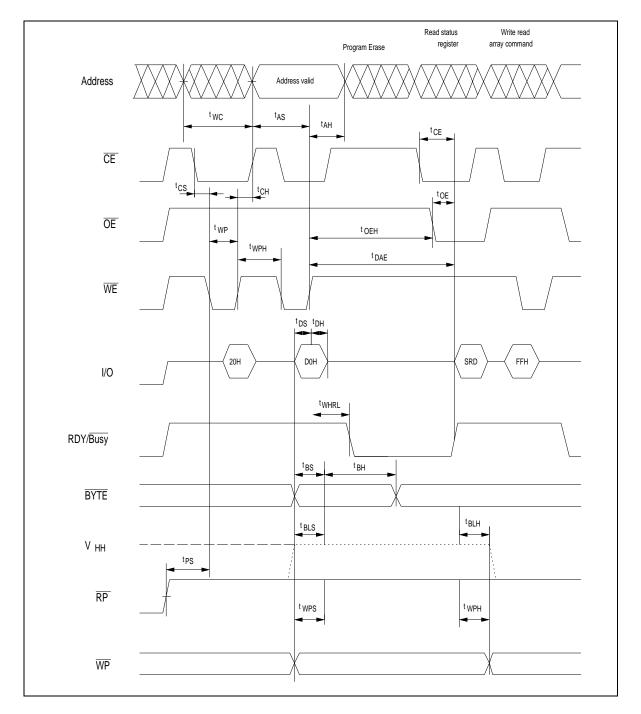

### Write Timing Waveform for Erase Operations ( $\overline{\text{WE}} \text{ control})$

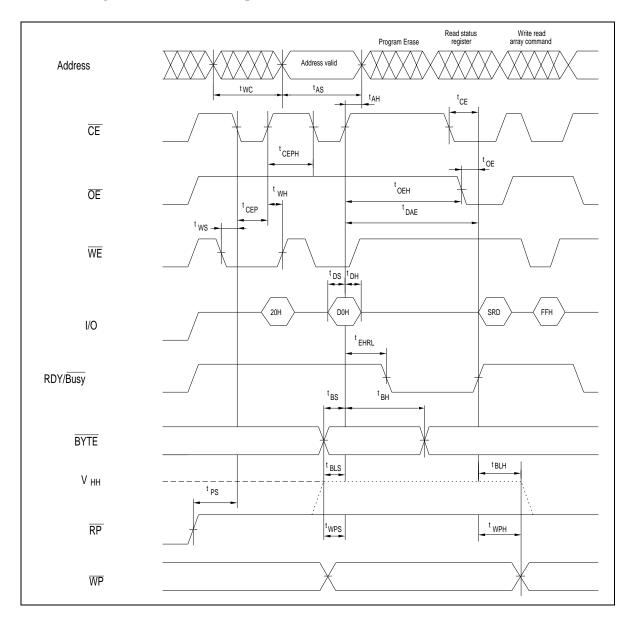

### Write Timing Waveform for Erase Operations ( $\overline{\text{CE}}$ control)

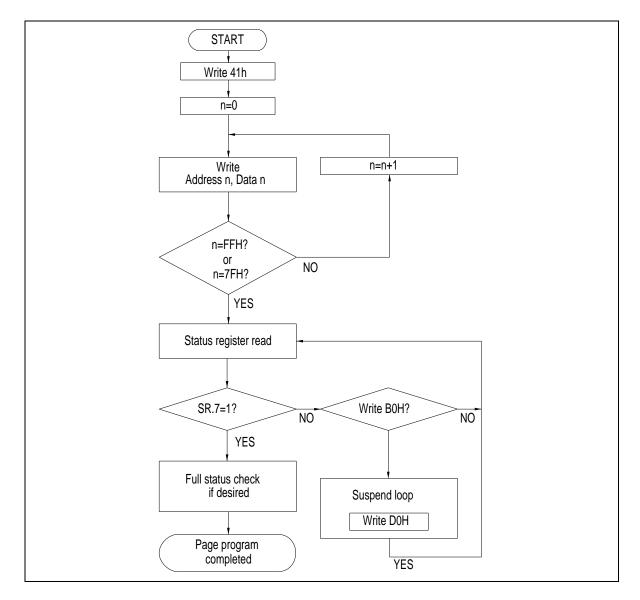

#### Page Program Flowchart

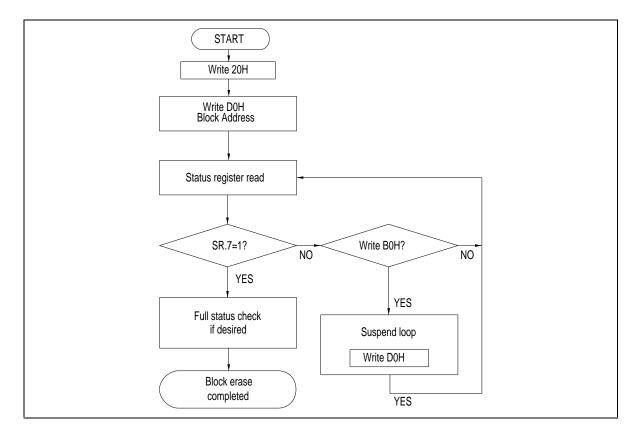

#### **Block Erase Flowchart**

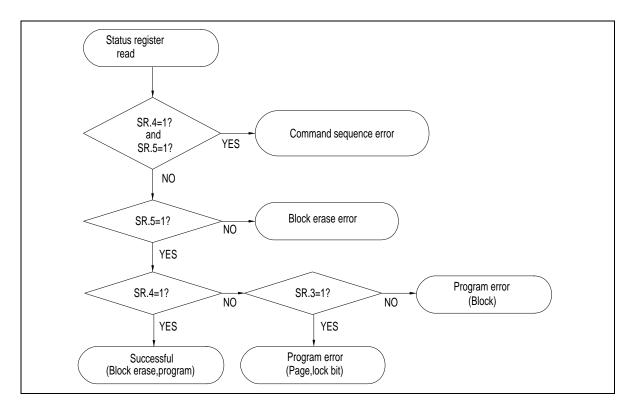

#### **Full Status Check Procedure**

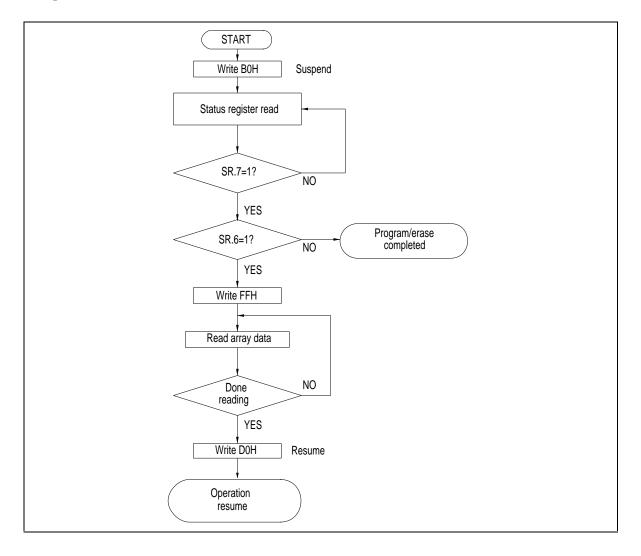

#### Suspend/Resume Flowchart

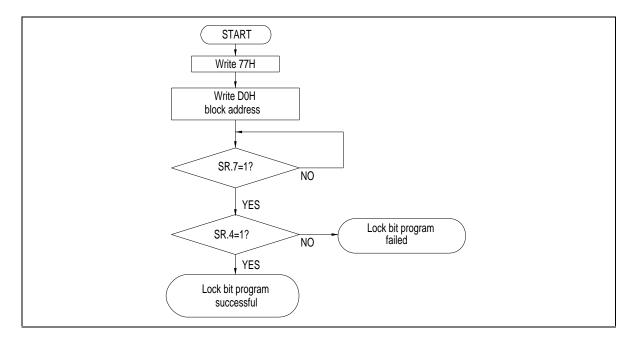

### Lock Bit Program Flowchart

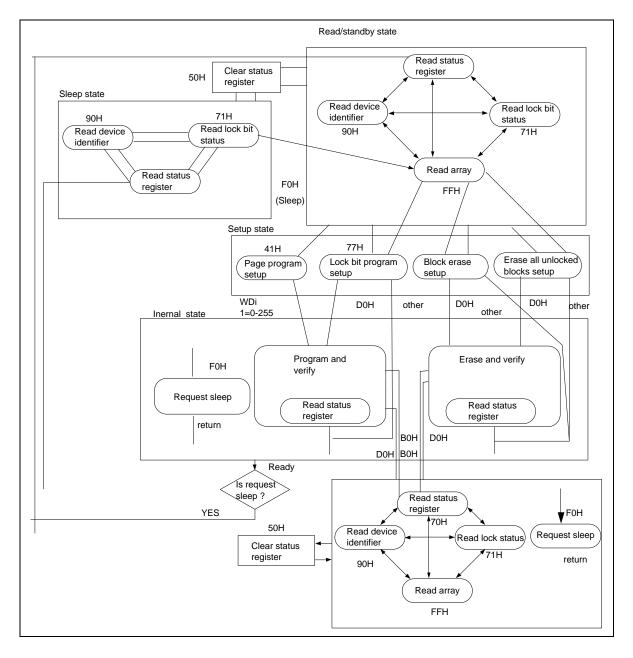

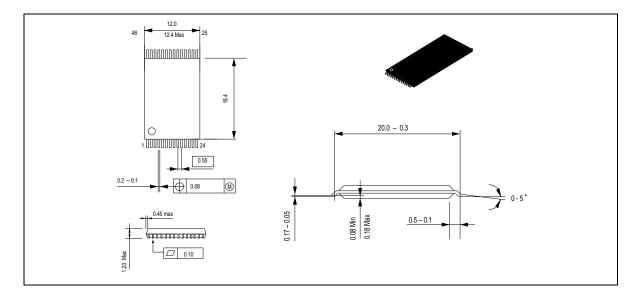

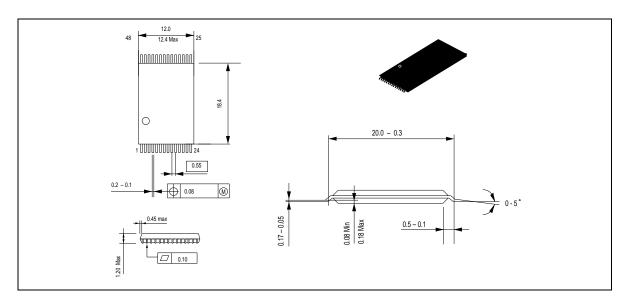

### **Package Dimensions**

#### HN29WT800FP/HN29WB800FP Series (FP-44D)

#### HN29WT800T/HN29WB800T Series (TFP-44D)

#### HN29WT800R/HN29WB800R Series (TFP-48DR)

#### Notice

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.