# CT8020 TrueSpeech® G.723.1 Co-Processor

### Introduction

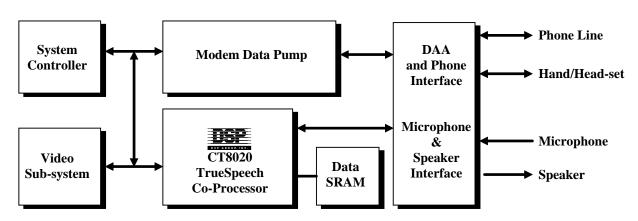

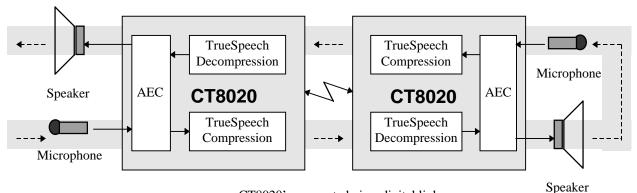

The CT8020 is a TrueSpeech co-processor which performs full duplex speech compression and decompression functions. It provides speech compression for H.323 and H.324 Multimedia Visual Telephony / Video Conferencing products, and DSVD Modems (Digital Simultaneous Voice and Data) for use over standard PSTN phone line connections. TrueSpeech 8.5 is compatible with Microsoft Sound System 2.0, and is a standard part of Windows<sup>®</sup> 95. TrueSpeech 6.3 and 5.3 are fully compatible with the ITU-T G.723.1 speech compression standard specified under H.324 and H.323. The CT8020 supports TrueSpeech compressed data rates of 8.5, 6.3, 5.3, 4.8 and 4.1 Kbps. In DSVD Modems and Video Conferencing applications, the CT8020 device is designed to coexist with the modem data pump ICs (and video compression device) to provide the speech compression/de-compression functions under the control of the host controller. In addition, the Acoustical Echo Canceller feature complements the TrueSpeech functions of this device by providing hands-free operation concurrently with TrueSpeech operation.

The TrueSpeech algorithm delivers highly compressed speech without compromising the speech quality. TrueSpeech 6.3 has a MOS score of 3.9 while running at 6.3 Kbps. TrueSpeech 6.3 with 6.3 and 5.3 kbps rates, has been approved as G.723.1 by ITU-T for the H.324 and H.323 family of products.

-continued on pg. 2

#### **Features**

- TrueSpeech at 8.5, 6.3, 5.3, 4.8 and 4.1 kbps at 8KHz sampling rate

- G.723.1 (including Annex A VAD/CNG) and Windows<sup>®</sup> 95 TrueSpeech 8.5 compatibility

- Real-time Full duplex or Half duplex speech compression and decompression

- Acoustic Echo Cancellation concurrent with TrueSpeech and G.723.1 operation

- Full Duplex Speakerphone

- Host-to-Host (codec-less) and Host-CODEC modes of operation

- Parallel 8-bit host interface provides simple "zero-glue" memory-mapped I/O host connection.

- 1 or 2-channel DMA support (Single Cycle and Burst Modes)

- Flexible A-to-D/D-to-A CODEC interface, low cost PCM µ/A-Law and 16-bit Linear

- CODEC interface supports TDM bus connection

- Automatic handling of frame slippage and frame synchronization

- Automatic AGC for message recording

- Speech level detection and Silence compression

- DTMF and Tone Generation

- DTMF and Programmable Tone Detection

- Pass-through modes 8-bit and 16-bit linear at 8 KHz and 11 KHz (host programmable codec sample rate)

- Power Down and Power Save modes

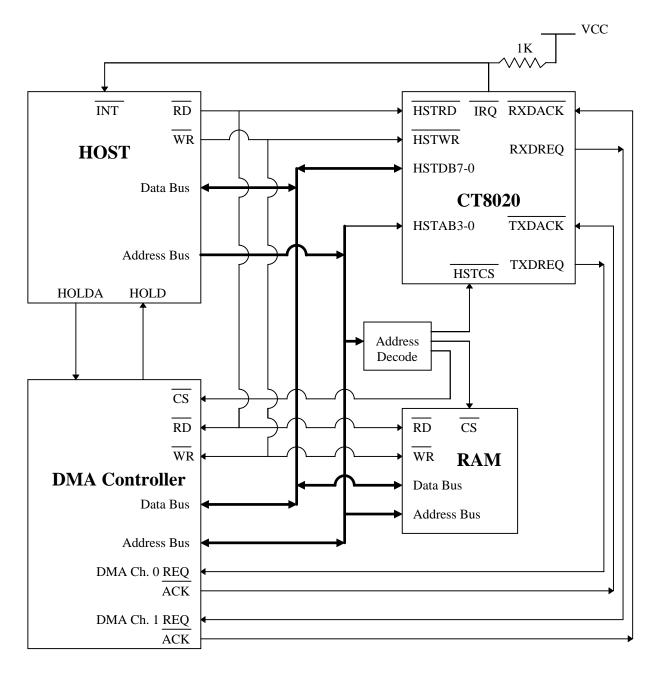

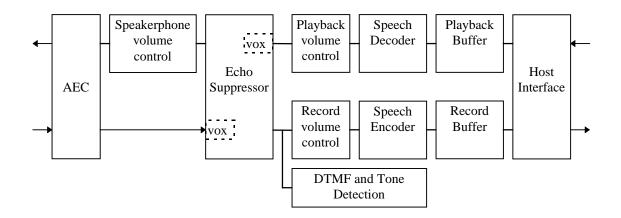

**CT8020 System Block Diagram**

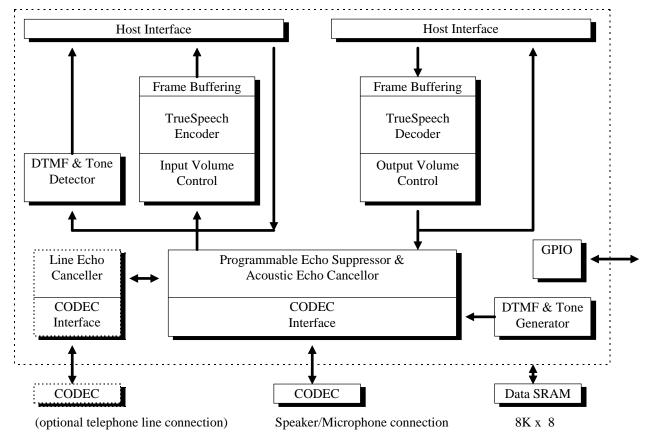

The CT8020, an Application Specific Digital Signal Processor, is controlled by the system's host processor through a simple host interface command protocol. The host processor provides activation and control of all system functions. The CT8020 host interface is capable of full duplex data transfer, aided by variable depth transmit and receive buffers. The host interface supports data transfer using DMA as well as host-interrupt and host-polling modes. The CT8020 supports two modes of uncompressed speech input/output. In HOST-CODEC mode, the uncompressed speech input/output is provided by one of the external serial codecs. In HOST-HOST (codec-less) mode, the Host provides the uncompressed speech input/output via the host interface. In both CODEC and HOST mode, the TrueSpeech compressed speech input/output data is transferred via the host interface.

# The only additional external component ICs needed to implement these functions are a low cost 8Kx8 or 32Kx8 SRAM, a CODEC and oscillator crystal circuit.

Note: MOS, Mean Opinion Score is a subjective measure of speech quality where a score of 5 means that the speech quality is Excellent, 4 is Good or Toll Quality (as expected in PSTN) and 3 is fair.

### Applications

- Simultaneous Voice and Data Modems

- Teleconferencing and Video Conferencing

- CTI Computer-Telephony Applications

- Digital Telephony Applications

- Voice Enabled Wireless Terminals

- Real-time compression and de-compression of TrueSpeech 8.5 Windows Sound System and Windows 95 compatible PC speech files

- Store & Forward applications for speech

- Desktop Telephony & Speakerphone

### **CT8020 Functional Block Diagram**

| 1. PIN-OUT AND PIN DESCRIPTIONS                         | 1-1 |

|---------------------------------------------------------|-----|

| 2. EXTERNAL COMPONENT CONNECTIONS                       | 2-1 |

| 2.1 PLL CIRCUIT                                         |     |

| 2.2 CT8020 8-BIT EXTERNAL DATA SRAM CONNECTION          |     |

| 2.3 CODEC CONNECTION                                    |     |

| 3. FEATURE OVERVIEW                                     |     |

| 3.1 INTRODUCTION                                        |     |

| 3.2 Speech Modes                                        |     |

| 3.3 TRUESPEECH                                          |     |

| 3.4 TRUESPEECH 8.5                                      |     |

| 3.5 TRUESPEECH 6.3 (G.723.1)                            |     |

| 3.6 TRUESPEECH 5.3 (G.723.1)                            |     |

| 3.7 TRUESPEECH 4.8                                      |     |

| 3.8 TRUESPEECH 4.1                                      |     |

| 3.9 Automatic Gain Control                              |     |

| 3.10 RECORD AND PLAYBACK VOLUME                         |     |

| 3.11 DSVD                                               |     |

| 3.12 Microsoft Windows <sup>®</sup> Sound System        |     |

| 3.13 DATA COMPRESSION/DE-COMPRESSION ACCELERATOR        |     |

| 3.14 DTMF / TONE GENERATOR                              |     |

| 3.15 TONE DETECTION                                     |     |

| 3.16 DTMF DETECTION                                     |     |

| 3.17 FULL DUPLEX SPEAKERPHONE                           |     |

| 3.18 ACOUSTICAL ECHO CANCELLATION                       |     |

| 3.19 8 / 16 BIT HOST CONTROLLER INTERFACE               |     |

| 3.20 CODEC INTERFACE                                    |     |

| 3.21 CT8020 CRYSTAL                                     |     |

| 3.22 POWER SAVE MODES                                   |     |

| 4. HOST CONTROLLER INTERFACE                            |     |

| 4.1 8 OR 16 BIT HOST CONTROLLER INTERFACE               |     |

| 4.2 HOST INTERFACE SIGNALS                              |     |

| 4.3 CT8020 Host Connection with external DMA controller |     |

| 4.4 HOST PROGRAMMERS MODEL                              |     |

| 4.5 REGISTER DESCRIPTIONS                               |     |

| 4.5.1 Hardware Control Register                         |     |

| 4.5.2 Hardware Status Register                          |     |

| 4.5.3 Software Control Register                         |     |

| 4.5.4 Software Status Register                          |     |

| 4.5.5 Host Receive and Transmit Data Buffer Blocks      |     |

| 4.6 DMA TRANSFERS                                       |     |

| 4.6.1 DMA modes                                         |     |

| 4.6.1.1 Full-Duplex Mode                                |     |

| 4.6.1.2 Half-Duplex Mode                                |     |

| 4.6.2 Burst Mode and Single Cycle Mode Transfers        |     |

| 4.6.3 Flow-Through DMA Transfers                        |     |

| 5. CT8020 CODEC INTERFACE                               | 5-1 |

| 5.1 CODEC OPTIONS                                       |     |

| 5.1.1 Master/Slave                                      |     |

|                                                         |     |

| 5.1.2 8-bit A-law/Mu-law and 16-bit linear codec                       |     |

|------------------------------------------------------------------------|-----|

| 5.1.3 Short or Long FSYNC                                              |     |

| 5.1.4 Programmable SCLK and FSYNC rates                                |     |

| 5.1.5 Stop Codec                                                       |     |

| 6. HOST DATA TRANSFER MODES                                            | 6-1 |

| 6.1 DATA TRANSFER USING THE DATA BUFFERS                               |     |

| 6.1.1 DMA Transfers                                                    |     |

| 6.1.2 Host Processor Transfers                                         |     |

| 6.2 DATA TRANSFER USING THE SOFTWARE CONTROL AND STATUS REGISTERS      |     |

| 6.2.1 Host Control/Status Register Data Transfer Synchronization Modes |     |

| 6.2.1.1 Codec Sync Mode                                                |     |

| 6.2.1.2 Data Sync Mode                                                 |     |

| 6.2.1.3 Poll Sync Mode                                                 |     |

| 6.3 DATA TRANSFER OPTIONS SUMMARY                                      |     |

|                                                                        |     |

| 7. PLAY & RECORD DELAY MANAGEMENT                                      |     |

| 7.1 DELAY AND LATENCY MANAGEMENT.                                      |     |

| 7.2 DATA UNDER-RUN AND OVER-RUN                                        |     |

| 7.3 BUFFER MONITORING.                                                 |     |

| 7.4 FRAME CREATION AND DELETION                                        |     |

| 7.5 BUFFER FREEZING (PAUSING)                                          |     |

| 7.6 VARIABLE BUFFER DEPTH                                              |     |

| 7.7 SILENCE GENERATION DURING TRANSMIT (PLAYBACK) DATA UNDER-RUN       |     |

|                                                                        |     |

| 8. TEST MODES                                                          |     |

| 8.1 Test Mode 1: Count mode                                            |     |

| 8.2 TEST MODE 2: DIGITAL MILLIWATT                                     |     |

| 8.3 TEST MODE 3: INTERNAL LOOPBACK                                     |     |

| 8.4 CODEC LOOPBACK AND MONITORING                                      |     |

| 9. CT8020 HOST CONTROL PROTOCOL                                        |     |

| 9.1 OPERATIONAL MODES                                                  |     |

| 9.2 BASIC PROTOCOL                                                     |     |

| 9.3 RESET & START-UP SEQUENCE                                          |     |

| 9.4 IDLE                                                               |     |

| 9.5 CODEC CONFIGURATION                                                |     |

| 9.5.1 Codec Configuration Command                                      |     |

| 9.5.2 Example codec configurations                                     |     |

| 9.6 RECORD                                                             |     |

| 9.6.1 Transfer Mode                                                    |     |

| 9.6.2 Recording Modes                                                  |     |

| 9.6.3 Peak Level Indication                                            |     |

| 9.6.4 Record Protocol                                                  |     |

| 9.6.5 Select TrueSpeech/G.723.1 Record Rate                            |     |

| 9.6.6 Enable VAD                                                       |     |

| 9.6.7 Switching between TrueSpeech/G.723.1 6.3 and 5.3                 |     |

| 9.6.8 G.723.1 Frame Type Encoding.                                     |     |

| 9.6.9 Programming the Record Peak Threshold                            |     |

| 9.6.10 Reading the Record Level Value and Threshold Value              |     |

| 9.7 PLAYBACK                                                           |     |

| 9.7.1 Transfer Mode<br>9.7.2 Playback Modes                            |     |

| 7.1.2 I MYDUCK 1410UCS                                                 |     |

| 9.7.3 Playback Protocol                                                                                            |             |

|--------------------------------------------------------------------------------------------------------------------|-------------|

| 9.7.4 Playback Frame Alignment Using Transmit Data Buffer                                                          |             |

| 9.7.5 Select TrueSpeech Playback Rate                                                                              |             |

| 9.7.6 Inserting Silence During Compressed Speech Playback                                                          |             |

| 9.7.7 Activating The G.723.1 Frame Erasure Mechanism                                                               |             |

| 9.7.8 G.723.1 Comfort Noise Generation (CNG)                                                                       |             |

| 9.8 STOP RECORD/PLAYBACK                                                                                           |             |

| 9.9 PLAYBACK & RECORD VOLUME CONTROL                                                                               |             |

|                                                                                                                    |             |

| 9.9.1 Read Record/Playback Volume Control Command:                                                                 |             |

| 9.9.2 Set Record/Playback Volume Control                                                                           |             |

| 9.9.3 Automatic Gain/Level Control (AGC or ALC)                                                                    |             |

| 9.9.3.1 Programming the AGC                                                                                        |             |

| 9.10 PRE-SCALING OF DTMF AND CALL PROGRESS FILTER INPUT                                                            |             |

| 9.11 HOST SYNC MODES                                                                                               |             |

| 9.12 PLAYBACK & RECORD BUFFER CONTROL                                                                              |             |

| 9.12.1 Monitoring Buffer Depth                                                                                     |             |

| 9.12.2 Speech Frame Create                                                                                         |             |

| 9.12.3 Speech Frame Delete                                                                                         |             |

| 9.12.4 Playback & Record Buffer Freeze (Pause)                                                                     |             |

| 9.12.5 Buffer Depth Limit                                                                                          |             |

| 9.12.6 Playback Auto-Repeat                                                                                        |             |

| 9.13 FULL DUPLEX SPEECH MODE                                                                                       |             |

| 9.14 ACOUSTIC ECHO CANCELLOR IN DSVD MODE                                                                          |             |

| 9.14.1 Concurrent AEC and Speech Operation                                                                         |             |

| 9.14.1 Concurrent ALC and Speech Operation<br>9.14.2 Activating the Advanced Echo Canceller features in the CT8020 |             |

|                                                                                                                    |             |

| 9.14.3 Adding Additional Echo Suppression                                                                          |             |

| 9.14.3.1 Set Echo Suppresser Attenuation                                                                           |             |

| 9.14.4 AEC Train and Lock                                                                                          |             |

| 9.14.4.1 AEC Locked State                                                                                          |             |

| 9.14.4.2 Setting the Lock Threshold<br>9.14.4.3 Setting the Un-Lock Threshold                                      |             |

|                                                                                                                    |             |

| 9.14.4.4 Freezing the AEC<br>9.14.5 Controling the Automatic Loop Adjustment Attenuation                           |             |

| 9.14.5 Controlling the Automatic Loop Adjustment Attenuation<br>9.14.5.1 Programming the Loop Adjustment Threshold |             |

| 9.14.5.2 Programming the Loop Adjustment Attenuation                                                               |             |

| 9.14.6 Reading the instantaneous AEC attenuation                                                                   |             |

|                                                                                                                    |             |

| 9.14.7 Saving and Restoring the AEC and EEC coefficients                                                           |             |

| 9.14.7.1 Save AEC coefficients                                                                                     |             |

| 9.14.7.2 Restore AEC Coefficients<br>9.14.7.3 Save EEC coefficients                                                |             |

| 9.14.7.4 Restore EEC coefficients                                                                                  |             |

| 9.14.8 Evaluating Echo Canceller Performance                                                                       |             |

|                                                                                                                    |             |

| 9.15 SPEECH FRAME INTERRUPT                                                                                        |             |

| 9.15.1 Frame Interrupt via the FR pin                                                                              |             |

| 9.15.2 Frame Interrupt via Aux Software Status Register                                                            |             |

| 9.16 DEVICE SELF-TEST                                                                                              |             |

| 9.16.1 Check Internal Program ROM Integrity                                                                        |             |

| 9.16.2 Test External Data SRAM                                                                                     |             |

| 9.16.3 External Data SRAM Configuration                                                                            |             |

| 9.17 DEVICE IDENTIFICATION                                                                                         |             |

| 9.17.1 Get Device Identification code                                                                              |             |

| 9.17.2 Get Device Version (revision) code                                                                          |             |

| 9.18 TONE GENERATION IN IDLE MODE                                                                                  |             |

| 9.18.1 Synchronous mode                                                                                            |             |

| 9.18.2 Asynchronous mode                                                                                           |             |

| 9.18.3 Tone Generation in Asynchronous mode:                                                                       |             |

| 2.10.0 10.00 Ocher anton in 115 yneni onous moae                                                                   | ······ >-05 |

| 9.18.5 New Tone Initialization<br>9.18.6 Default (Power-On) Tone Table Contents |      |

|---------------------------------------------------------------------------------|------|

| 9.18.6 Default (Power-On) Tone Table Contents                                   |      |

|                                                                                 |      |

| 9.19 CT8020 Line Monitor Commands                                               |      |

| 9.19.1 Line Monitor Command                                                     |      |

| 9.19.2 Synchronous and Asynchronous Monitor Mode                                |      |

| 9.19.3 Enabling and Disabling the DTMF Detector                                 |      |

| 9.19.4 Controlling the Call Progress Tone Filters F0-F3                         |      |

| 9.19.5 Reading the Filter Energy Output                                         |      |

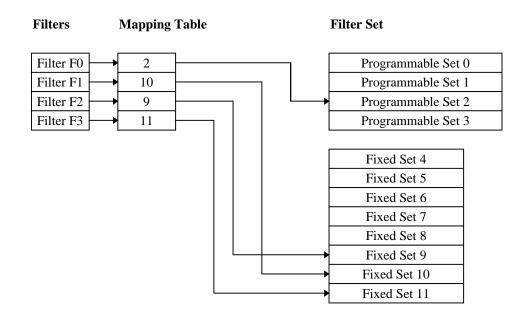

| 9.19.6 Selecting the Filter Characteristics                                     |      |

| 9.19.7 Changing the Filter Parameter Set Mapping Table                          |      |

| 9.19.8 Filter Detection Algorithm                                               |      |

| 9.19.9 Reading the Filter History Register                                      |      |

| 9.19.10 Reading the Frame Counter                                               |      |

| 9.19.10 Redaing the Frame Counter<br>9.19.11 Programming the CT8020 Filters     |      |

| 9.20 STANDALONE SPEAKERPHONE                                                    |      |

|                                                                                 |      |

| 9.20.1 Enter Standalone Speakerphone Mode Command:                              |      |

| 9.20.2 Get Speakerphone Status Command:                                         |      |

| 9.20.3 Set Speakerphone Parameters Command:                                     |      |

| 9.20.4 SpeakerPhone Configuration Command:                                      |      |

| 9.20.5 Generate Tone (in speakerphone mode):                                    |      |

| 9.20.6 Get Electrical Echo Canceller Quality Factor Command:                    |      |

| 9.21 HOST-TO-HOST DATA COMPRESSION AND DECOMPRESSION                            |      |

| 9.21.1 Host-to-Host compression                                                 |      |

| 9.21.1.1 Recording (Compression) Modes                                          |      |

| 9.21.2 Host-to-Host decompression                                               |      |

| 9.21.2.1 Playback (Decompression) Modes                                         |      |

| 9.21.3 Full Duplex Host-to-Host Compression-Decompression                       |      |

| 9.22 TEST MODES                                                                 |      |

| 9.22.1 Test Mode 1: count mode                                                  |      |

| 9.22.2 Test Mode 2: digital milliwatt                                           |      |

| 9.22.3 Test Mode 3: loopback                                                    |      |

| 9.22.4 Exit Test Mode                                                           |      |

| 9.22.5 Codec Loopback                                                           |      |

| 9.22.6 Codec (Audio) Monitoring                                                 | 9-92 |

| 9.23 Power Save Modes                                                           | 9-93 |

| 9.23.1 CT8020 Stop Mode                                                         | 9-93 |

| 9.23.2 Stop Codec Mode                                                          |      |

| 9.23.3 Re-Start Codec                                                           | 9-93 |

| 9.23.4 CT8020 Slow Down (Power Save) Modes                                      | 9-94 |

| 9.24 GENERAL PURPOSE INPUT OUTPUT PINS (GPIO)                                   | 9-95 |

| 9.24.1 Configure GPIO input/output direction:                                   | 9-95 |

| 9.24.2 Write GPIO pins                                                          |      |

| 9.24.3 Read GPIO pins                                                           |      |

|                                                                                 |      |

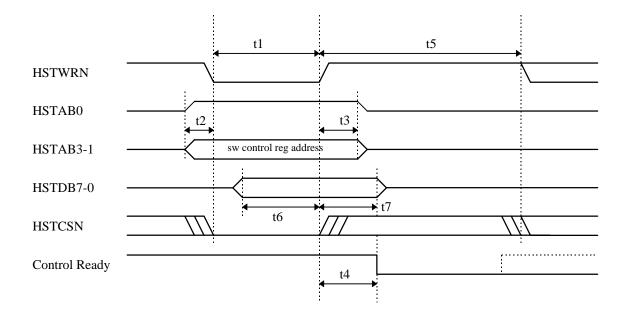

| 10. CT8020 HOST INTERFACE TIMING                                                | 10-1 |

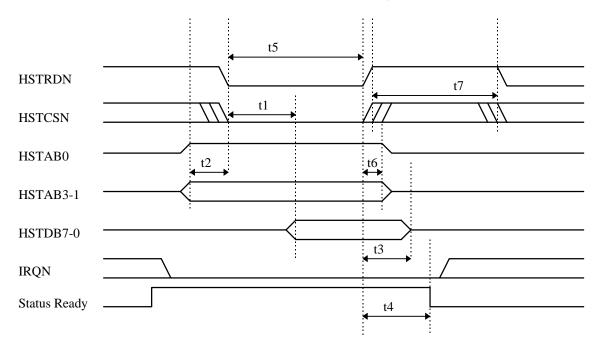

| 10.1 HOST WRITE TO SOFTWARE CONTROL REGISTER M.S. BYTE                          | 10-1 |

| 10.2 HOST READ FROM SOFTWARE STATUS REGISTER M.S. BYTE                          | 10-3 |

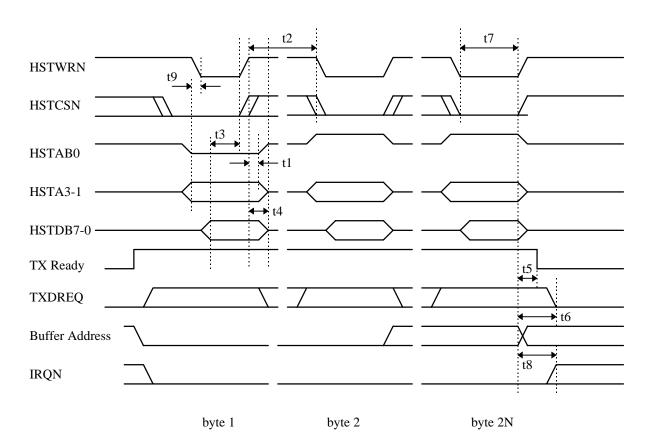

| 10.3 HOST WRITE TO HOST TRANSMIT DATA BUFFER ACCESS PORT                        |      |

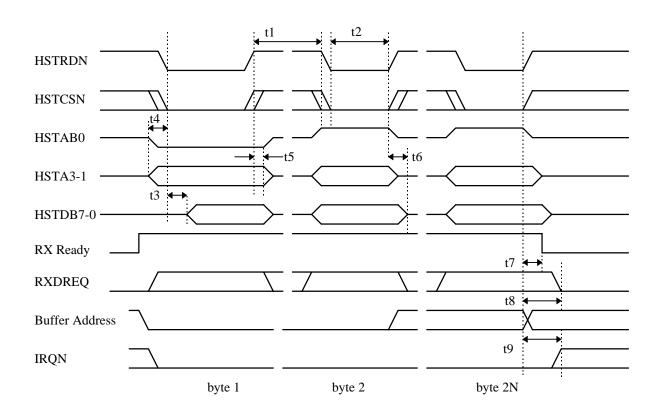

| 10.4 HOST READ FROM HOST RECEIVE DATA BUFFER ACCESS PORT                        |      |

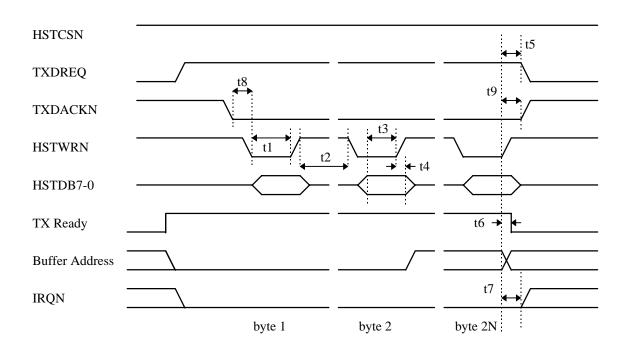

| 10.5 DMA WRITE TO HOST TRANSMIT DATA BUFFER ACCESS PORT (BURST MODE)            |      |

| 10.6 DMA WRITE TO HOST TRANSMIT DATA BUFFER ACCESS PORT (SINGLE CYCLE MODE)     |      |

| 10.7 DMA READ FROM HOST RECEIVE DATA BUFFER ACCESS PORT (BURST MODE)            |      |

| 10.8 DMA READ FROM HOST RECEIVE DATA BUFFER ACCESS PORT (SINGLE CYCLE MODE)     |      |

| 11. CT8020 CODEC INTERFACE TIMING AND AC SPECIFICATION |      |

|--------------------------------------------------------|------|

| 11.1 SHORT FRAME SYNC                                  |      |

| 11.2 LONG FRAME SYNC                                   |      |

| 12. ELECTRICAL CHARACTERISTICS                         | 12-1 |

| 13. MECHANICAL DATA - CT8020                           |      |

| APPENDIX A : SPEAKERPHONE THEORY OF OPERATION                 |                    |

|---------------------------------------------------------------|--------------------|

| INTRODUCTION                                                  | A-2                |

| ANALOG CIRCUITRY                                              |                    |

| ACOUSTIC SYSTEM                                               | A-2                |

| CT8020 DIGITAL CANCELER                                       | A-3                |

| Half-Duplex mode                                              | A-3                |

| Full-Duplex mode                                              |                    |

| VOLUME CONTROL                                                | A-4                |

| DIAL TONE DETECTION                                           | A-4                |

| Performance                                                   | A-4                |

| EXAMPLE CONTROL ALGORITHM                                     | A-5                |

| APPENDIX B : AEC PERFORMANCE IN DSVD APPLICATIONS Error! Book | cmark not defined. |

| APPENDIX C : WAVE FILE FORMAT (.WAV)                          | C-1                |

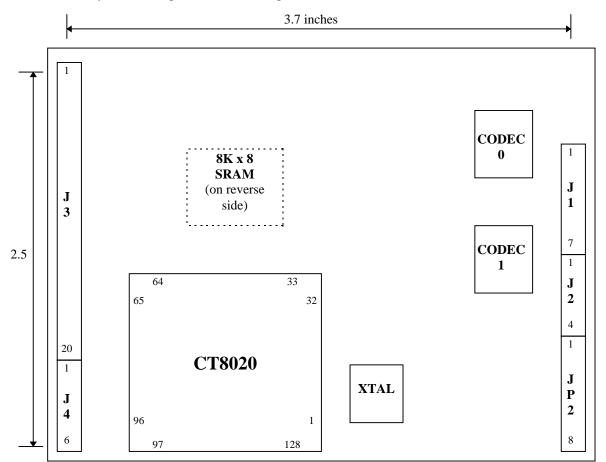

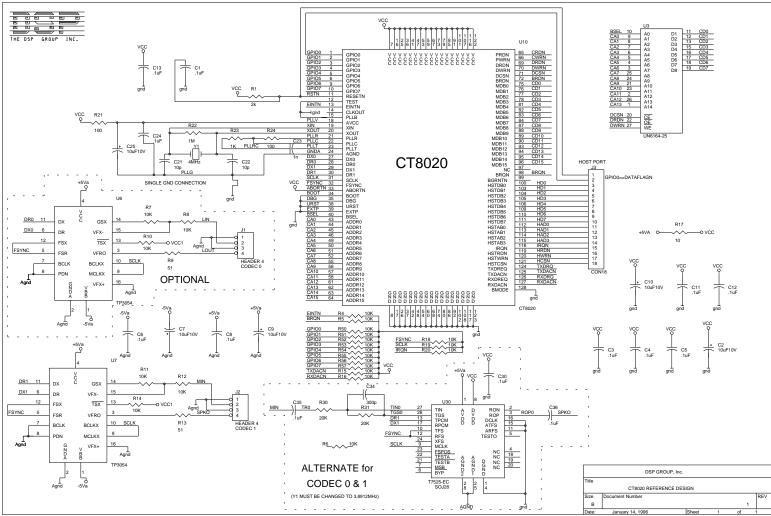

| APPENDIX D : CT8020 EVALUATION BOARD                          | D-1                |

| APPENDIX E : G.723.1 FRAME STRUCTURE                          | E-1                |

| G.723.1 VERSION HISTORY                                       | E-3                |

| G.723.1 CONTROL BITS                                          | E-4                |

# **List Of Figures**

| FIGURE 2-1 PLL CIRCUIT                                           |  |

|------------------------------------------------------------------|--|

| FIGURE 2-2 EXTERNAL SRAM CONNECTION                              |  |

| FIGURE 2-3 CODEC CONNECTION                                      |  |

| FIGURE 4-1 CT8020 CONNECTION TO HOST AND EXTERNAL DMA CONTROLLER |  |

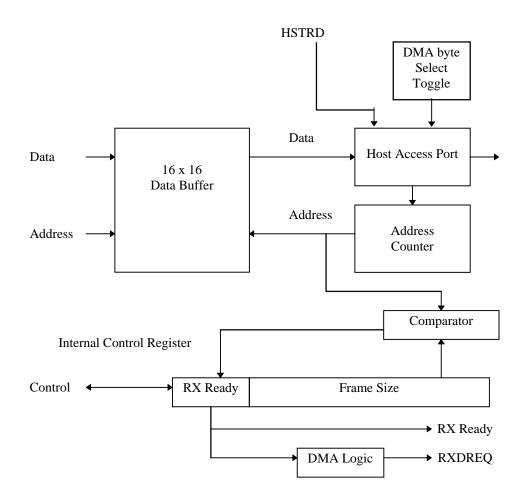

| FIGURE 4-2 HOST RECEIVE DATA BUFFER BLOCK                        |  |

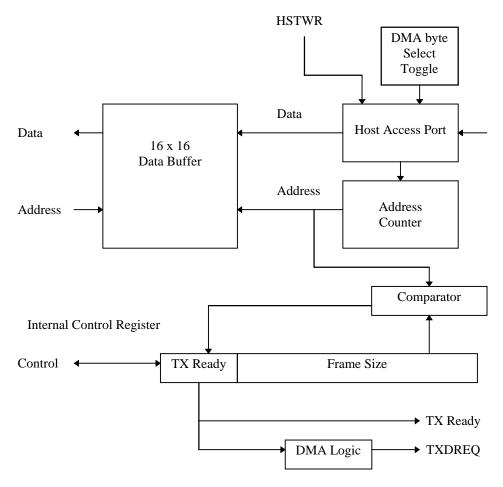

| FIGURE 4-3 HOST TRANSMIT DATA BUFFER BLOCK                       |  |

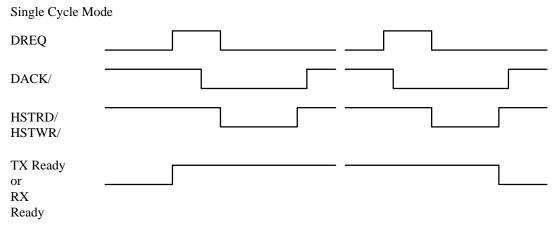

| FIGURE 4-4 SINGLE CYCLE DMA MODE                                 |  |

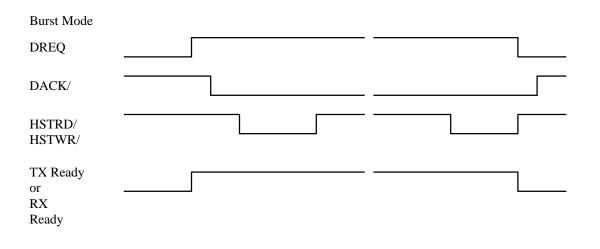

| FIGURE 4-5 BURST MODE DMA                                        |  |

| FIGURE 4-6 FLOW-THROUGH DMA.                                     |  |

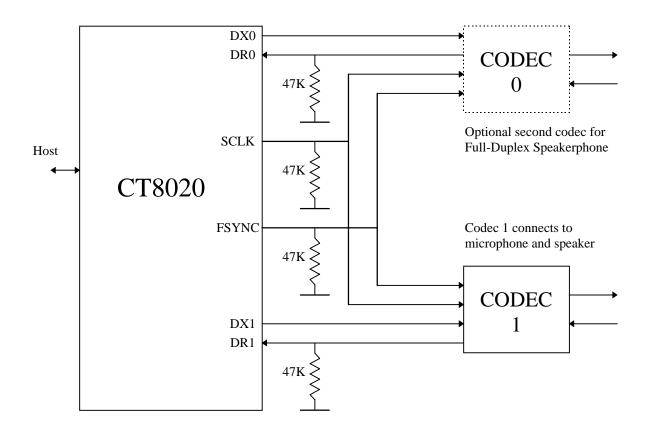

| FIGURE 5-1 CT8020 CODEC INTERFACE CONNECTION                     |  |

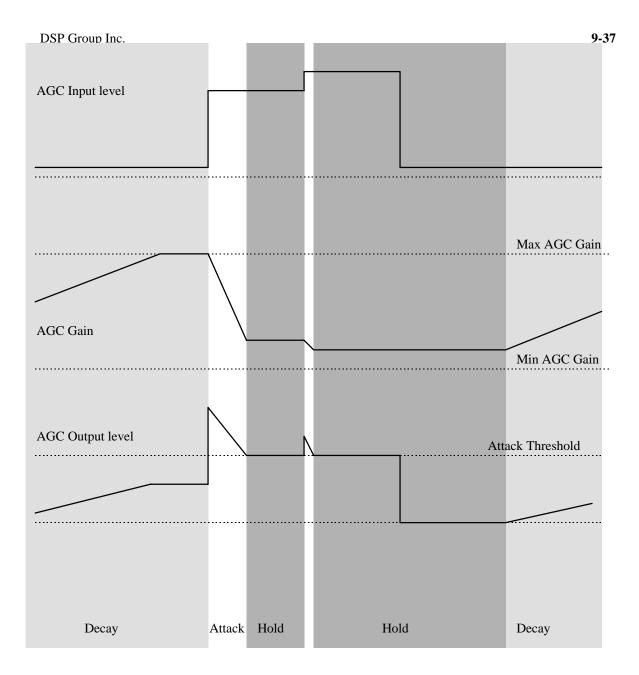

| FIGURE 9-1 AGC ATTACK HOLD & DECAY                               |  |

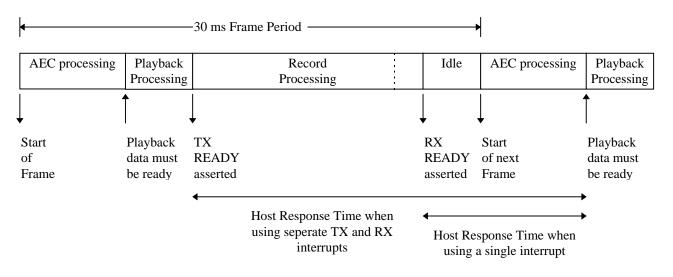

| FIGURE 9-2 CT8020 INTERNAL PROCESSING ACTIVITY                   |  |

| FIGURE 9-3 AEC AND SPEECH COMPRESSION                            |  |

| FIGURE 9-4 FILTER MAPPING                                        |  |

| FIGURE 9-5 HOST-TO-HOST OPERATION                                |  |

|                                                                  |  |

# **1. PIN-OUT AND PIN DESCRIPTIONS**

Not available electronically at this time. Call (408) 986-4300 and request to have it faxed to your location, or check back shortly.

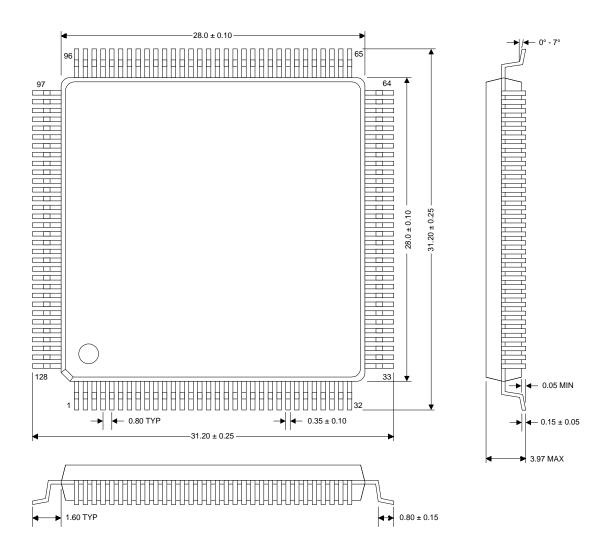

128 pin PQFP/TQFP

This section contains a list of the CT8020 pins:

Note that the CT8020 is a CMOS device. It is important to make sure that all input pins are connected and have a valid logic level present at all times. Where noted, certain input pins may require external pull-up or pull-down resistors.

Signal naming convention: Active low signals are indicated by a trailing "/" or "N" in the signal name. For example SRAMCS/ or SRAMCSN.

| Pin names                                      | Pin Numbers                     | type  | function                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|---------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSTDB0<br>HSTDB1<br>HSTDB2<br>HSTDB3<br>HSTDB4 | 100<br>103<br>104<br>105<br>106 | I/O/Z | Host Data Bus. HSTDB0 is the least significant data bit.                                                                                                                                                                                                                                                                                                                                                          |

| HSTDB5<br>HSTDB6<br>HSTDB7                     | 109<br>110<br>111               |       |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HSTAB0                                         | 112                             | I     | HSTAB0 is the least significant Host Address bit, it selects between the high and low byte of the host interface register selected by HSTAB3-1.                                                                                                                                                                                                                                                                   |

| HSTAB1<br>HSTAB2<br>HSTAB3                     | 113<br>114<br>115               | Ι     | Host Address Bus. These address bits are used to select<br>host interface register addressed by host (in conjunction<br>with HSTCS/).                                                                                                                                                                                                                                                                             |

| HSTRD/<br>(HSTRDN)                             | 119                             | Ι     | Host Read signal. Active Low, output enables HSTDB<br>pins, allowing host to read from the selected host<br>interface register. The interface register is selected via a<br>decode of HSTAB1-3 if HSTCS/ is active, or the Host<br>Receive Data Buffer access port is selected directly if<br>RXDACK/ is asserted.                                                                                                |

| HSTWR/<br>(HSTWRN)                             | 120                             | I     | Host Write signal. Active Low, clocks data from HSTDB<br>pins into selected host interface register. The interface<br>register is selected via a decode of HSTAB1-3 if<br>HSTCS/ is active, or the Host Transmit Data Buffer<br>access port is selected directly if TXDACK/ is asserted.                                                                                                                          |

| HSTCS/<br>(HSTCSN)                             | 121                             | I     | Host Interface Chip Select. Active Low. This signal gates<br>the HSTWR/ and HSTRD/ and HSTAB3-0 address<br>decode during a host processor access cycle. The<br>HSTAB3-0 signals should be stable and valid when<br>HSTCS/ is asserted.<br>This signal <b>must not be asserted</b> during a DMA cycle<br>on the host port. <b>HSTCS/ must be high when either</b><br><b>TXDACK/ or RXDACK/ are asserted (low).</b> |

| TXDREQ                                         | 124                             | 0     | Active High signal. DMA transmit request. This signal is<br>asserted to indicate that the device is ready to accept<br>transmit data. Data can be transferred either by DMA or<br>a host processor access cycle. This signal can be enabled<br>or disabled by the host via the Hardware Control<br>Register. By default, this signal is disabled.                                                                 |

| TXDACK/<br>(TXDACKN)                           | 125                             | Ι     | Active Low signal. DMA Transmit Acknowledge. This signal is asserted by an external DMA controller on the host port, together with HSTWR/, to clock a byte from                                                                                                                                                                                                                                                   |

|                |          |       | the HSTDB databus pins into the host interface Transmit     |

|----------------|----------|-------|-------------------------------------------------------------|

|                |          |       | Data Buffer Access port. This signal provides direct        |

|                |          |       | access to the Host Transmit Data Buffer Access Port,        |

|                |          |       | without involving HSTAB0-3 or HSTCS/. If this signal is     |

|                |          |       | not used, it should be connected to VCC via a 10K ohm       |

|                |          |       | pull-up resistor. This signal must not be asserted when     |

|                |          |       | either RXDACK/ or HSTCS/ are active.                        |

| RXDREQ         | 126      | 0     | Active High signal. DMA receive request. This signal is     |

|                |          |       | asserted to indicate that the device is ready to provide    |

|                |          |       | receive data. Data can be transferred either by DMA or a    |

|                |          |       | host processor access cycle. This signal can be enabled     |

|                |          |       | or disabled by the host via the Hardware Control            |

|                |          |       | Register. By default, this signal is disabled.              |

| RXDACK/        | 127      | Ι     | Active Low signal. DMA Receive Acknowledge. This            |

|                |          |       | signal is asserted by an external DMA controller on the     |

| (RXDACKN)      |          |       | host port, together with HSTRD/, to accept a receive data   |

|                |          |       | byte via the HSTDB databus pins from the host interface     |

|                |          |       | Receive Data Buffer Access port. This signal provides       |

|                |          |       | direct access to the Host Receive Data Buffer Access        |

|                |          |       | Port, without involving HSTAB0-3 or HSTCS/. If this         |

|                |          |       | signal is not used, it should be connected to VCC via a     |

|                |          |       | 10K ohm pull-up resistor. <b>This signal must not be</b>    |

|                |          |       | asserted when either TXDACK/ or HSTCS/ are active.          |

| IRQ/           | 118      | OC    | Interrupt Request. Open collector output (requires          |

| IKQ/           | 110      | UC    | external pull-up resistor with min value 1K ohm). This      |

| (IRQN)         |          |       | signal is asserted to indicate an interrupt request to the  |

| (Interv)       |          |       | host controller.                                            |

| MDB0           | 75       | I/O/Z | External Memory Data Bus, used to interface to external     |

| MDB1           | 76       |       | memory. When the CT8020 is used with external 8-bit         |

| MDB2           | 77       |       | wide data SRAM, the SRAM data lines should be               |

| MDB3           | 78       |       | connected to the l.s. CT8020 data pins (MDB7-0). The        |

| MDB4           | 81       |       | CT8020 supports external data memory configured as          |

| MDB5           | 82       |       | 8Kx8 or 4Kx16.                                              |

| MDB6           | 83       |       |                                                             |

| MDB7           | 84       |       |                                                             |

|                |          |       |                                                             |

| MDB8           | 87       |       |                                                             |

| MDB9           | 88       |       |                                                             |

| MDB10          | 89       |       |                                                             |

| MDB11          | 90       |       |                                                             |

| MDB12          | 93       |       |                                                             |

| MDB13          | 94       |       |                                                             |

| MDB14<br>MDB15 | 95       |       |                                                             |

| ADDR0          | 96<br>43 | O/Z   | External Memory Address Bus, used to interface to           |

| ADDR0<br>ADDR1 | 43       | U/L   | external memory. Note that the CT8020 is a 16-bit           |

| ADDR1<br>ADDR2 | 44 45    |       | device and the address lines indicate access to 16-bit data |

| ADDR2<br>ADDR3 | 46       |       | words. When the CT8020 is used with external 8-bit          |

| ADDR3<br>ADDR4 | 40       |       | wide SRAM, the least significant address line of the        |

| ADDR4<br>ADDR5 | 50       |       | SRAM should be connected to the BSEL pin (byte              |

| ADDR6          | 50       |       | select). In this configuration, the SRAM pin A1 connects    |

| ADDR7          | 52       |       | to the CT8020 pin A0, SRAM pin A2 connects to the           |

|                |          |       | CT8020 pin A1etc.                                           |

| ADDR8      | 55 |     | Note that the CT8020 address pins indicate the <b>16-bit</b>                                                        |

|------------|----|-----|---------------------------------------------------------------------------------------------------------------------|

| ADDR9      | 56 |     | word address being accessed, the BSEL pin is used to                                                                |

| ADDR10     | 57 |     | select between the upper and lower bytes within a word                                                              |

| ADDR11     | 58 |     | when a byte-wide memory is used.                                                                                    |

| ADDR12     | 61 |     |                                                                                                                     |

| ADDR13     | 62 |     |                                                                                                                     |

| ADDR14     | 63 |     |                                                                                                                     |

| ADDR15     | 64 |     |                                                                                                                     |

| BSEL       | 40 | O/Z | Byte Select. Used to select the low or high byte accessed during an 8-bit external data access cycle. Driven low to |

|            |    |     | select the low byte. Driven high to select the high byte.<br>When the CT8020 is used with external 8-bit wide       |

|            |    |     | SRAM, the BSEL signal should be used to drive the                                                                   |

|            |    |     | SRAW, the DSEE signal should be used to unvertice<br>SRAM A0 pin. The SRAM A1 pin should be connected               |

|            |    |     | to the CT8020 A0 pin, the SRAM A2 pin should be                                                                     |

|            |    |     | connected to the CT8020 A1 pinetc.                                                                                  |

|            |    |     | The state of this pin is defined only during an external                                                            |

|            |    |     | data cycle in 8-bit mode. At other times, this pin may be                                                           |

|            |    |     |                                                                                                                     |

| DATARD/    | 60 | O/Z | high or low.                                                                                                        |

| DATARD     | 69 | 0/Z | External Data Memory Read. Active Low, used to                                                                      |

|            |    |     | indicate a read cycle from external data memory                                                                     |

| (DATARDN)  | 70 | 0/7 | Enternal Data Manuary Write Active Law wood to                                                                      |

| DATAWR/    | 70 | O/Z | External Data Memory Write. Active Low, used to                                                                     |

| (DATAWRN)  |    |     | indicate a write cycle to external data memory.                                                                     |

| PREAD/     | 65 | O/Z | Reserved - NC (do not connect)                                                                                      |

| PWRITE/    | 66 | O/Z | Reserved - NC (do not connect)                                                                                      |

| BOOTRD/    | 72 | O/Z | Reserved - NC (do not connect)                                                                                      |

| SRAMCS/    | 71 | O/Z | external data SRAM chip select. Active low. This signal                                                             |

|            |    |     | is asserted during external data access.                                                                            |

| (SRAMCSN)  |    |     | C C                                                                                                                 |

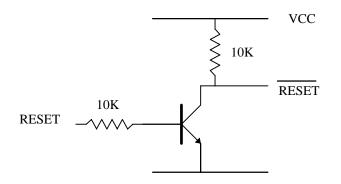

| RESET/     | 11 | Ι   | Reset signal. Active Low, the pin is driven low to reset                                                            |

|            |    |     | the device. Note - this pin is not a TTL input. VIH =                                                               |

| (RESETN)   |    |     | 4.25 volts max. $VIL = 1.3$ volts min.                                                                              |

| GPIO0,     | 1  | I/O | General purpose Input/Output pins.                                                                                  |

| DATAFLAG   |    |     | for CT8015 compatibility:                                                                                           |

| - 1        |    |     | GPIO 0 may be assigned as DATAFLAG/ (output)                                                                        |

| GPIO1      | 2  |     | GPIO 5 may be assigned as Frame Interrupt, FR/ (output)                                                             |

| GPIO2      | 3  |     | (ouput)                                                                                                             |

| GPIO3      | 4  |     | During reset, the GPIO pins are all configured as inputs.                                                           |

| GPIO4      | 5  |     | or the second     |

|            |    |     | Connect 47K ohm pull-down resistors to GND on                                                                       |

| GPIO5, FR\ | 6  |     | each GPIO pin to ensure that a valid input signal<br>level is present at all times.                                 |

| GPIO6      | 9  |     | it with is present at an units.                                                                                     |

| GPIO7      | 10 |     |                                                                                                                     |

| SCLK       | 31 | I/O | Shift Clock for codec interface. During and after reset,                                                            |

| JULK       | 51 | 1/0 | this pin is configured as an input. <b>Connect 47K ohm</b>                                                          |

|            |    |     |                                                                                                                     |

|            |    |     | pull-down resistors to GND to this pin to ensure that                                                               |

|            |    |     | a valid input signal level is present at all times. If this                                                         |

|            |    |     | pin is permanently driven by an external signal, no pull-                                                           |

|            |    |     | down is required. The SCLK signal is typically expected                                                             |

|            |    |     | to operate at 2.048 MHz. When used as an output                                                                     |

|            |    |     | (master mode) the SCLK rate is programmable by the                                                                  |

|                      |                |                            | host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FSYNC                | 32             | I/O                        | Frame Sync clock for codec interface. During and after<br>reset, this pin is configured as an input. <b>Connect 47K</b><br><b>ohm pull-down resistors to GND to this pin to ensure</b><br><b>that a valid input signal level is present at all times.</b> If<br>this pin is permanently driven by an external signal, no<br>pull-down is required. The FSYNC signal is typically<br>expected to operate at 8 KHz to provide the 8KHz<br>sample clock required by the external serial codec. When<br>used as an output (master mode), the FSYNC rate is<br>programmable by the host. |

| DX0                  | 27             | O/Z                        | Serial Transmit Data Output for codec 0. This output is<br>always high impedance when not transmitting data. This<br>codec pin is used for telephone line output in Standalone<br>Speakerphone mode.                                                                                                                                                                                                                                                                                                                                                                                |

| DR0                  | 28             | I                          | Serial Receive Data Input for codec 0. Connect 47K<br>ohm pull-down resistors to GND to this pin to ensure<br>that a valid input signal level is present at all times.<br>Note that codec chip output pins typically tri-state when<br>not actually transmitting data. This codec pin is used for<br>telephone line input in Standalone Speakerphone mode.                                                                                                                                                                                                                          |

| DX1                  | 29             | O/Z                        | Serial Transmit Data Output for codec 1. This output is<br>always high impedance when not transmitting data.<br>This is the default codec output used for playback.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DR1                  | 30             | I                          | Serial Receive Data Input for codec 1 <b>Connect 47K ohm</b><br><b>pull-down resistors to GND to this pin to ensure that</b><br><b>a valid input signal level is present at all times.</b><br>Note that codec chip output pins typically tri-state when<br>not actually transmitting data. This is the default codec<br>input used for record.                                                                                                                                                                                                                                      |

| XIN                  | 19             | Ι                          | Crystal Input or external oscillator input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XOUT                 | 20             | 0                          | Crystal Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CLKOUT               | 14             | 0                          | Clock Out = MAINCLOCK/(CLK_RATE+1). This is the<br>internal CT8020 DSP core clock. The output may be<br>disabled to reduce power consumption. The<br>MAINCLOCK frequency in PLL mode, is the external<br>crystal frequency * 10. In PLL by-pass mode,<br>MAINCLOCK is the external oscillator frequency<br>divided by 2. See section 9.23.4 for definition of<br>CLK_RATE.                                                                                                                                                                                                          |

| TEST                 | 12             | I                          | Reserved - connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PLLR<br>PLLC<br>PLLT | 21<br>22<br>23 | Analog<br>Analog<br>Analog | PLL support circuitry pins. Connect to external PLL filter circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AVCC3                | 18             | Ι                          | PLL VCC connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AGND3                | 24             | Ι                          | PLL GND connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLLBYPASS            | 15             | I                          | Disables internal PLL when high and allows direct use of<br>an external (80 MHz) clock applied to the XIN pin.<br>Connect to GND when operating using PLL and external<br>4 MHz crystal.                                                                                                                                                                                                                                                                                                                                                                                            |

| BUSREQ/              | 98             | Ι                          | Reserved input, active low. Connect this pin to VCC via a 10K ohm pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BUSGRANT/     | 99       | 0 | Reserved - NC (do not connect)                            |

|---------------|----------|---|-----------------------------------------------------------|

| EXTP          | 39       | Ι | Reserved - connect to GND                                 |

| BOOTMODE      | 128      | Ι | Reserved - connect to GND                                 |

| DBG           | 35       | Ι | Reserved - connect to GND                                 |

| ABORT/        | 33       | Ι | Reserved, active low - connect to VCC via 10 Kohm         |

|               |          | _ | pull-up resistor.                                         |

| BOOT          | 34       | Ι | Reserved - connect to GND                                 |

| URST          | 38       | I | Reserved - connect to GND                                 |

| EXTINT/       | 13       | I | Reserved, active low - connect to VCC via 10 Kohm         |

|               | 15       | 1 | pull-up resistor.                                         |

| GND1          | 8        | Ι | Ground pins                                               |

| GND1<br>GND2  | 17       | 1 | Ground phis                                               |

| UND2          | 1/       |   |                                                           |

| GND4          | 26       |   |                                                           |

| GND4<br>GND5  | 37       |   |                                                           |

| GND5<br>GND6  | 42       |   |                                                           |

| GND6<br>GND7  | 42 48    |   |                                                           |

|               | 48<br>54 |   |                                                           |

| GND8<br>GND9  | 54<br>60 |   |                                                           |

| GND9<br>GND10 | 60<br>68 |   |                                                           |

|               |          |   |                                                           |

| GND11         | 74       |   |                                                           |

| GND12         | 80       |   |                                                           |

| GND13         | 86       |   |                                                           |

| GND14         | 92       |   |                                                           |

| GND15         | 102      |   |                                                           |

| GND16         | 108      |   |                                                           |

| GND17         | 117      |   |                                                           |

| GND18         | 123      |   |                                                           |

| VCC1          | 7        | Ι | Power Supply pins                                         |

| VCC2          | 16       |   |                                                           |

| NGGA          | 25       |   |                                                           |

| VCC4          | 25       |   |                                                           |

| VCC5          | 36       |   |                                                           |

| VCC6          | 41       |   |                                                           |

| VCC7          | 47       |   |                                                           |

| VCC8          | 53       |   |                                                           |

| VCC9          | 59       |   |                                                           |

| VCC10         | 67       |   |                                                           |

| VCC11         | 73       |   |                                                           |

| VCC12         | 79       |   |                                                           |

| VCC13         | 85       |   |                                                           |

| VCC14         | 91       |   |                                                           |

| VCC15         | 101      |   |                                                           |

| VCC16         | 107      |   |                                                           |

| VCC17         | 116      |   |                                                           |

| VCC18         | 122      |   |                                                           |

| Unused        | 97       |   | This pin has no internal connection to the device. It may |

|               |          |   | be left un-connected.                                     |

Note, pins marked "Reserved - NC (no connect)" should be left un-connected. These Reserved pins are outputs, connecting them to either GND or VCC may cause damage to the device. Other pins are marked either "Reserved - connect to GND" or "Reserved - connect to VCC via 10 K ohm pull-up resistor". These Reserved pins are inputs which require a defined input signal level. They should not be left to "float". Pins

marked as Reserved are not intended for active use by the user. However these pins may be used by other devices in the CT8000 series family.

# 2. External Component Connections

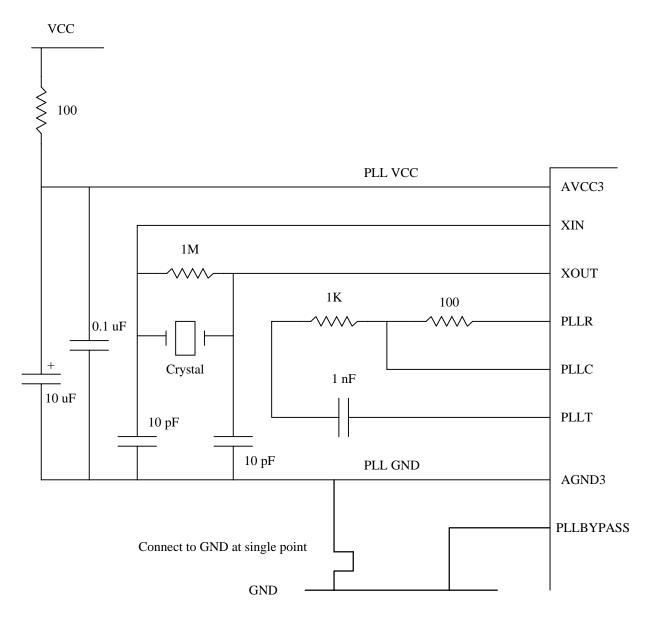

# 2.1 PLL Circuit

Crystal frequency is nominal 4 MHz. Crystal may be replaced by external 4MHz clock source. *Figure 2-1 PLL Circuit*

| DATARD                                                                                                               |                       | RD                                                                               |

|----------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------|

| DATAWR                                                                                                               |                       | WR                                                                               |

| SRAMCS                                                                                                               |                       | CS                                                                               |

| ADDR13<br>ADDR12                                                                                                     | for 32K x 8 sram only | A14<br>A13                                                                       |

| ADDR11<br>ADDR10<br>ADDR09<br>ADDR08<br>ADDR07<br>ADDR06<br>ADDR05<br>ADDR04<br>ADDR03<br>ADDR02<br>ADDR01<br>ADDR01 |                       | A12<br>A11<br>A10<br>A09<br>A08<br>A07<br>A06<br>A05<br>A04<br>A03<br>A02<br>A01 |

| BSEL                                                                                                                 |                       | A00                                                                              |

| MDB07<br>MDB06<br>MDB05<br>MDB04<br>MDB03<br>MDB02<br>MDB01<br>MDB00                                                 |                       | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0                                     |

| CT8020                                                                                                               | 1                     | 8K x 8                                                                           |

### 2.2 CT8020 8-bit external data SRAM connection

Note that the CT8020 BSEL pin is used to drive the SRAM A0 address line. The CT8020 requires only a 8Kx8 SRAM, but a 32Kx8 SRAM may be used as an alternative.

SRAM 25 ns

Figure 2-2 External SRAM connection

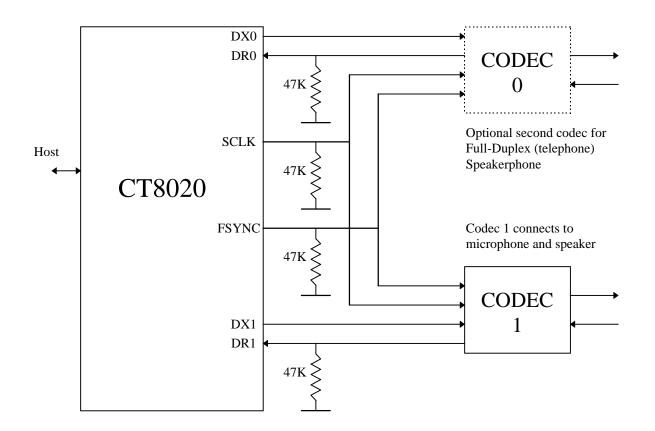

# 2.3 Codec Connection

Figure 2-3 CODEC connection

In Master mode, the CT8020 generates the FSYNC and SCLK signals.

In Slave mode, the FSYNC and SCLK signals are generated externally. In slave mode, the CT8020 FSYNC and SCLK pins are inputs.

Note that during and after reset, the SCLK and FSYNC pins are configured as inputs. As such, they require external pull-down resistors to ensure that a safe and defined logic level is present.

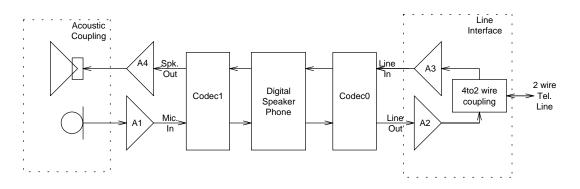

CODEC 0 is required only if "Standalone" Full Duplex Speakerphone operation is desired (e.g for use as an analog phone line speakerphone). In this configuration, CODEC 0 connects to the audio input/output of an analog telephone line. CODEC 0 is not required for DSVD/Video Conferencing Speakerphone operation.

For codec-less operation, both CODEC 0 and CODEC 1 may be omitted. In this case, the FSYNC, SCLK, DR0 and DR1 inputs should have pull-down resistors connected to ground to ensure a valid input signal level.

# 3. FEATURE OVERVIEW

# 3.1 Introduction

The CT8020 is a full duplex TrueSpeech real-time speech compression Encoder/Decoder. It is designed to operate in conjunction with a host processor and one or two external A-to-D/D-to-A serial CODECs. The host processor is responsible for managing the bi-directional stream of compressed speech data provided by the CT8020. The CT8020 accepts un-compressed speech in 8-bit A-law/mu-law or 16-bit Linear formats at 64/128 Kbits/sec from the receive channel of the external serial CODEC and compresses the speech to TrueSpeech at 8.5, 6.3, 5.3, 4.8 or 4.1 Kbits/sec. The compressed speech is passed to the host processor in frames every 30 ms. At the same time that the CT8020 is compressing speech, it can concurrently accept compressed speech from the host for decompression, outputting the uncompressed speech to the transmit channel of the external codec. The CT8020 supports independent and asynchronous operation of the host receive and transmit (compressed) data streams. The transmit and receive interfaces to the external codec operate synchronously. The device contains variable length buffers for each data direction and also provides support of frame deletion and insertion to accommodate sample clock differences between the source and destination devices.

# 3.2 Speech Modes

The CT8020 playback (transmit) and record (receive) channels can operate in several different speech modes : TrueSpeech (compressed), A-law/Mu-law (non-compressed), 8-bit and 16-bit linear. In TrueSpeech mode, speech data is exchanged with the host in compressed form, in appropriate sized frames every 30ms. In A-law/Mu-law or 8-bit linear mode, speech data is exchanged with the host in non-compressed mode in frames of 120 words (240 bytes) of A-law/Mu-law or linear data every 30 ms. In this mode, the data rate is 64,000 bits/sec. In 16-bit mode, the data frame size is 240 words (480 bytes). In this mode, the data rate is 128 Kbits/sec. The mode of operation of the playback and record channel can be selected independently of each other.

# 3.3 TrueSpeech

TrueSpeech is a speech compression technology which reduces or compresses the amount of data used to encode a speech waveform. TrueSpeech compression reduces speech sampled (digitized) at 8,000 samples per second, in 16-bit samples (128,000 bits/sec) to 8.5, 6.3, 5.3, 4.8 or 4.1 Kbits/sec with minimal degradation in speech quality.

In the CT8020, uncompressed speech is obtained from an external codec operating at 8,000 samples per second. If an external A-law or Mu-law codec is used, the speech is sampled by the external codec with 14bits of resolution. The codec converts the 14-bits (linear) samples to 8-bit A-law/Mu-law for transmission to the CT8020 (at 64,000 bits/sec). The CT8020 receives the speech samples from the codec and converts them back to 14-bit linear form. The 14-bit data is converted to 16 bits by appending two zero bits in the least significant bit positions. The 16-bit data is collected into blocks of 240 samples (480 byte) every 30 ms and TrueSpeech compressed for transfer to the host. If an external linear 16-bit codec is used, the speech data is sampled with 16-bit resolution and passed directly from the CODEC to the CT8020 at 128,000 bits/sec.

The CT8020 supports simultaneous compression and decompression of TrueSpeech data in real-time.

# 3.4 TrueSpeech 8.5

In TrueSpeech 8.5 mode, speech data is compressed/decompressed into 16-word (32 byte) blocks, which are transferred to or from the host every 30 ms. This corresponds to a data rate of 8,533.33 bits/sec. The CT8020 TrueSpeech 8.5 implementation is compatible with the TrueSpeech 8.5 format used in the CT8005 TrueSpeech Messaging Co-Processor, CT8015 TrueSpeech DSVD Co-Processor and Microsoft Windows Sound System 2.0 and Windows 95 software TrueSpeech CODECs.

# 3.5 TrueSpeech 6.3 (G.723.1)

The CT8020D11AQC version of the CT8020 implements the final (version 5.1) ITU-T formal release of the G.723.1 speech coder standard, including G.723.1 Annex A.

In TrueSpeech 6.3 (G.723.1), data is compressed into 12-word blocks. This provides 192 bits per block. However, only 189 bits are used for actual speech data, giving a raw data rate of 6,300 bits/sec. When used in compliance with G.723.1 two of the spare bits are assigned for control information. The CT8020 G.723.1 implementation includes the optional G.723.1 Annex A VAD/CNG "silence" compression feature (Voice Activity Detection / Comfort Noise Generation). When this feature is enabled, the CT8020 can generate and decode the 4-byte and 1-byte Annex A silence frames. The CT8020 supports dynamic switching between the G.723.1 6.3 and 5.3 rates for both the encoder and decoder. In addition, the G.723.1 6.3 and 5.3 decoders support frame erasure (for corrupt or missing frames) using specially marked data frames.

# 3.6 TrueSpeech 5.3 (G.723.1)

In TrueSpeech 5.3, data is compressed into 10-word blocks. This provides 160 bits per block. However, only 158 bits per block are used for actual speech data, giving a raw data rate of 5,266.67 bits/sec. When used in compliance with G.723.1, the two "spare" bits are used for control information. The 5.3 rate can be operated in conjunction with the VAD/CNG silence compression feature.

# 3.7 TrueSpeech 4.8

In TrueSpeech 4.8, data is compressed into 9-word blocks. This provides 144 bits per block. However only 142 bits per block are used for actual speech data, giving a raw data rate of 4733.33 bits/sec. The 4.8 rate can be operated in conjunction with the VAD/CNG silence compression feature.

# 3.8 TrueSpeech 4.1

In TrueSpeech 4.1, data is compressed into 8-word blocks. This provides 128 bits per block. However only 124 bits per block are used for actual speech data, giving a raw data rate of 4133.33 bits/sec. The 4.1 rate can be operated in conjunction with the VAD/CNG silence compression feature.

# 3.9 Automatic Gain Control

In speech record mode (compressed or uncompressed), the CT8020 record process can optionally include an Automatic Gain Control (AGC) function. When this feature is enabled, the CT8020 can automatically adjust the record signal level by internal digital scaling of the input speech signal. The control parameters for the AGC, which include max and min gain (amplification), attack and decay times (response time) are programmable by the host. Note that for optimal AEC performance in DSVD mode, use of the AGC feature concurrently with the Acoustic Echo Canceller is not recommended. However, where the user considers simultaneous use of both AEC and AGC to be necessary, the CT8020 does include a mechanism to reduce the echo amplification effect caused when the AGC gain increases.

# 3.10 Record and Playback Volume

The CT8020 supports host programmable record and playback volume controls. This enables internal digital scaling of the input and output speech signal levels. The host can elect to use fixed level settings during record in situations where AGC operation is not desired (for example - high noise environments). Also AGC operation is not appropriate in full duplex speech mode when the Acoustical Echo Cancellor (AEC) is active, since the AGC would interfere with the ability of the AEC to operate correctly. In particular, the AGC would operate to amplify the canceled (attenuated) echo signal.

# 3.11 DSVD

Digital Simultaneous Voice and Data is a protocol used to enable collaborative computing where voice conversation and full duplex data transfers occur simultaneously over a single telephone line via a high speed modem. Since the data transfer rate achievable over a telephone line is limited, speech compression is required to make it possible to send speech simultaneously with data. Applications for DSVD include application sharing, shared whiteboard and interactive games.

# 3.12 Microsoft Windows<sup>®</sup> Sound System

In addition to supporting playback and recording of compressed TrueSpeech data, the CT8020 can also playback and record un-compressed data in 16-bit linear, 8-bit linear, 8-bit mu-law and 8-bit A-law formats. The 8-bit linear format supports data in both signed and unsigned form (with or without most significant data bit inversion). This provides true Windows Sound System (WSS) 8 bit .wav file compatibility. The CT8020 supports 8- and 16-bit 8 KHz, and 11 KHz Microsoft WAVE file mono formats making it an ideal low cost device for speech enabling personal computers and personal digital assistants (PDAs). The Microsoft WAVE file format also includes support for storing of TrueSpeech 8.5 speech data, making it possible to directly exchange TrueSpeech WAVE recordings with WSS compliant PC's. A "software only" TrueSpeech 8.5 encoder/decoder is a standard part of the Sound Recorder application included with Windows<sup>®</sup> 95.

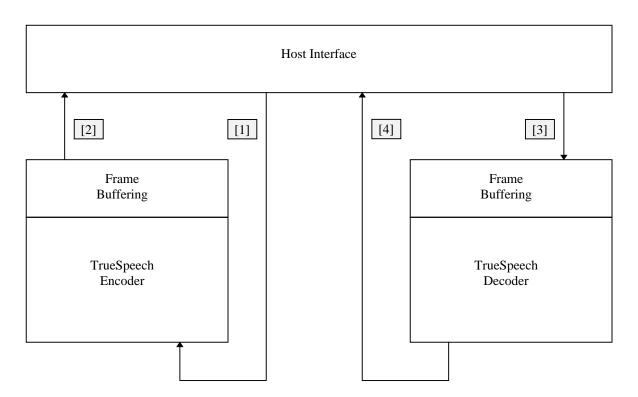

# 3.13 Data Compression/De-Compression Accelerator

The CT8020 can be used a data compression accelerator. In addition to supporting real-time recording and playback via external CODECs, the CT8020 can operate in a codec-less environment where it compresses 16-bit linear speech data from the host, returning the compressed data to the host. Simultaneous compression and decompression is supported. This enables the CT8020 to be used in a sound-card type environment where the speech input and output channels are independent of the CT8020.

# 3.14 DTMF / Tone Generator

The DTMF/Tone generator can generate any single or dual frequency tone in the range 300Hz to 3 KHz. The CT8020 has preset parameters for generating all 16 DTMF digits (0-9, \*, #, and the "hidden" digits A, B, C, D) as well as standard USA dial tone, busy tone, and ringing (ringback) tone. The preset parameters

can be re-programmed by the host controller to generate any single or dual frequency tone combination. The relative level (twist) of dual frequency tones can also be selected.

## 3.15 Tone Detection

The CT8020 contains a set of four independent programmable call progress tone filters which can be used to detect call progress tones such as dial tone, busy tone, ringing (or ringback) tone and fax calling tone (CNG).

# 3.16 DTMF Detection

The CT8020 includes a DTMF detector which can detect all 16 DTMF digits including the digits ABCD.

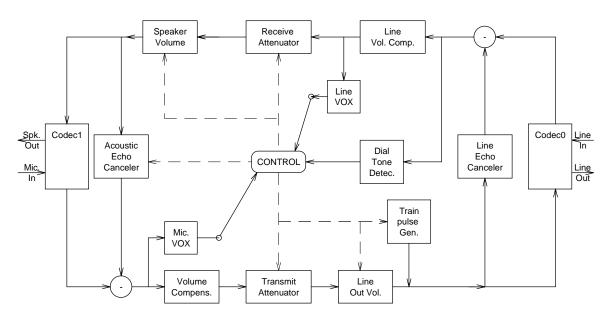

# 3.17 Full Duplex Speakerphone

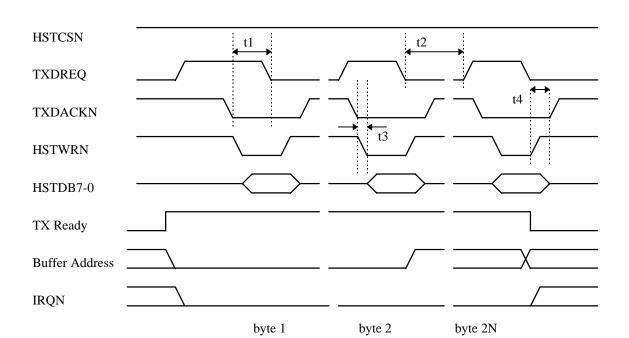

The CT8020 can operate in either **Standalone** Speakerphone or in **DSVD** Speakerphone mode. In DSVD Speakerphone mode, the CT8020 provides Acoustical Echo Cancellation between the speaker and microphone connection concurrent with TrueSpeech operation. In Standalone Full duplex Speakerphone mode, Acoustical Echo Cancellation as well as near-end (Electrical) echo cancellation to the telephone line connection are provided. Standalone Speakerphone mode provides support for creating an analog phone line based speakerphone.