# Spartan-3 FPGA Family: DC and Switching Characteristics

DS099-3 (v1.3) March 4, 2004

**Advance Product Specification**

# **DC Electrical Characteristics**

In this section, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

**Advance:** Initial estimates based on simulation, early characterization, and/or extrapolation from the characteristics of other families. Values are subject to change. Use as estimates, not for production.

**Preliminary:** Based on characterization. Further changes are not expected.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. The following applies unless otherwise noted: The parameter values published in this module apply to all Spartan-3 devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades. All parameters representing voltages are measured with respect to GND.

Some specifications list different values for one or more die revisions. All presently available Spartan-3 devices are classified as revision 0. Future updates to this module will introduce further die revisions as needed.

| Symbol                          | Description                                                               | Conditions                          | Min  | Max                     | Units |

|---------------------------------|---------------------------------------------------------------------------|-------------------------------------|------|-------------------------|-------|

| V <sub>CCINT</sub>              | Internal supply voltage                                                   |                                     | -0.5 | 1.32                    | V     |

| V <sub>CCAUX</sub>              | Auxiliary supply voltage                                                  |                                     | -0.5 | 3.00                    | V     |

| V <sub>CCO</sub>                | Output driver supply voltage                                              |                                     | -0.5 | 3.75                    | V     |

| $V_{REF}^{(2)}$                 | Input reference voltage                                                   |                                     | -0.5 | V <sub>CCO</sub> + 0.5  | V     |

| V <sub>IN</sub> <sup>(2)</sup>  | Voltage applied to all User I/O pins and Dual-Purpose pins <sup>(3)</sup> | Driver in a<br>high-impedance state | -0.5 | V <sub>CCO</sub> +0.5   | V     |

|                                 | Voltage applied to all Dedicated pins <sup>(4)</sup>                      |                                     | -0.5 | V <sub>CCAUX</sub> +0.5 | V     |

| Т <sub>Ј</sub>                  | Junction temperature                                                      | $V_{CCO} \le 3.0V$                  | -    | 125                     | °C    |

|                                 |                                                                           | V <sub>CCO</sub> > 3.0V             | -    | 105                     | °C    |

| T <sub>SOL</sub> <sup>(5)</sup> | Soldering temperature                                                     |                                     | -    | 220                     | °C    |

| T <sub>STG</sub>                | Storage temperature                                                       |                                     | -65  | 150                     | °C    |

# Table 1: Absolute Maximum Ratings

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings will cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time adversely affects device reliability.

2. Table 5 specifies the range of values for  $V_{CCO}$  and  $V_{CCAUX}$ , which are used to determine the limits of this parameter.

3. All User I/O and Dual-Purpose pins (DIN/D0, D1–D7, CS\_B, RDWR\_B, BUSY/DOUT, AND INIT\_B) draw power from the V<sub>CCO</sub> power rail of the associated bank.

All Dedicated pins (M0–M2, CCLK, PROG\_B, DONE, HSWAP\_EN, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). For information concerning the use of 3.3V signals, see the "3.3V-Tolerant Configuration Interface" section in <u>Module 2</u>.

5. For soldering guidelines, see the information on "Packaging and Thermal Characteristics" at www.xilinx.com.

© 2003-2004 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

www.xilinx.com 1-800-255-7778

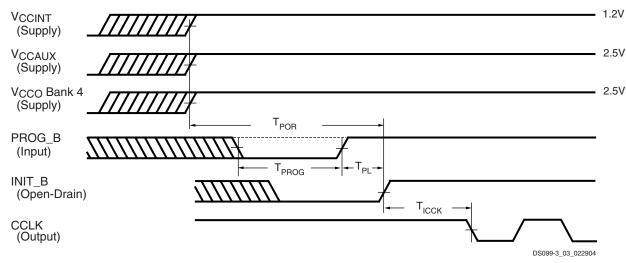

# Table 2: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                 | Min | Max | Units |

|---------------------|---------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply | 0.8 | 2.0 | V     |

| V <sub>CCO4T</sub>  | Threshold for the $V_{CCO}$ Bank 4 supply   | 0.4 | 1.0 | V     |

Notes:

1.

$V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  supplies may be applied in any order. To ensure successful power-on,  $V_{CCINT}$ ,  $V_{CCO}$  Bank 4, and  $V_{CCAUX}$  supplies must rise through their respective threshold-voltage ranges with no dips at any point. 2.

## Table 3: Other Power-On Requirements

| Symbol           | Description                                       | [      | Device Revision                                                               | Min               | Max | Units |

|------------------|---------------------------------------------------|--------|-------------------------------------------------------------------------------|-------------------|-----|-------|

| T <sub>CCO</sub> | CO V <sub>CCO</sub> ramp time for all eight banks |        | XC3S200, XC3S400,<br>and XC3S1500 in the<br>FT and FG packages <sup>(1)</sup> | 600               | -   | μs    |

|                  |                                                   |        | All other devices                                                             | 2.0               | -   | ms    |

|                  |                                                   | Future |                                                                               | To be<br>improved | -   |       |

Notes:

1. This specification is based on characterization.

2. At present, there are no ramp requirements for the V<sub>CCINT</sub> and V<sub>CCAUX</sub> supplies.

## Table 4: Power Voltage Levels Necessary for Preserving RAM Contents

| Symbol             | Description                                          | Min | Units |

|--------------------|------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | V <sub>CCAUX</sub> level required to retain RAM data | 2.0 | V     |

Notes:

RAM contents include configuration data. 1.

The level of the  $V_{CCO}$  supply has no effect on data retention. 2.

| Symbol                          | Descript                     | Min                            | Nom   | Max   | Units |    |

|---------------------------------|------------------------------|--------------------------------|-------|-------|-------|----|

| TJ                              | Junction temperature         | Inction temperature Commercial |       | -     | 85    | °C |

|                                 |                              | Industrial                     | -40   | -     | 100   | °C |

| V <sub>CCINT</sub>              | Internal supply voltage      |                                | 1.140 | 1.200 | 1.260 | V  |

| V <sub>CCO</sub> <sup>(1)</sup> | Output driver supply voltage |                                | 1.140 | -     | 3.450 | V  |

| V <sub>CCAUX</sub>              | Auxiliary supply voltage     | 2.375                          | 2.500 | 2.625 | V     |    |

# Table 5: General Recommended Operating Conditions

Notes:

The V<sub>CCO</sub> range given here spans the lowest and highest operating voltages of all supported I/O standards. The recommended V<sub>CCO</sub> range specific to each of the single-ended I/O standards is given in Table 8, and that specific to the differential standards is given in Table 10.

# Table 6: General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins

| Symbol                          | Description                                                                               | Test Conditions                                                                         | Devi | ce Revision             | Min   | Тур   | Max   | Units |

|---------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|-------------------------|-------|-------|-------|-------|

| ١ <sub>L</sub>                  | Leakage current at User                                                                   | Driver is in a                                                                          | 0    | $V_{CCO} \ge 3.0V$      | -25   | -     | +25   | μA    |

|                                 | I/O, Dual-Purpose, and<br>Dedicated pins                                                  | high-impedance state,<br>V <sub>IN</sub> = 0V or V <sub>CCO</sub> max,<br>sample-tested |      | V <sub>CCO</sub> < 3.0V | -10   | -     | +10   | μA    |

| I <sub>RPU</sub> <sup>(2)</sup> | Current through pull-up                                                                   | V <sub>IN</sub> =0, V <sub>CCO</sub> = 3.3V                                             |      | 0                       | -0.84 | -     | -2.35 | mA    |

|                                 | resistor at User I/O,<br>Dual-Purpose, and                                                | V <sub>IN</sub> =0, V <sub>CCO</sub> = 3.0V                                             |      |                         | -0.69 | -     | -1.99 | mA    |

| Dedicated pins                  | V <sub>IN</sub> =0, V <sub>CCO</sub> = 2.5V                                               |                                                                                         |      | -0.47                   | -     | -1.41 | mA    |       |

|                                 |                                                                                           | V <sub>IN</sub> =0, V <sub>CCO</sub> = 1.8V                                             |      |                         | -0.21 | -     | -0.69 | mA    |

|                                 |                                                                                           | V <sub>IN</sub> =0, V <sub>CCO</sub> = 1.5V                                             |      |                         | -0.13 | -     | -0.43 | mA    |

|                                 |                                                                                           | V <sub>IN</sub> =0, V <sub>CCO</sub> = 1.2V                                             |      |                         | -0.06 | -     | -0.22 | mA    |

| I <sub>RPD</sub> <sup>(2)</sup> | Current through<br>pull-down resistor at<br>User I/O, Dual-Purpose,<br>and Dedicated pins | V <sub>IN</sub> = V <sub>CCO</sub>                                                      |      |                         | 0.37  | -     | 1.67  | mA    |

| I <sub>REF</sub>                | V <sub>REF</sub> current per pin                                                          |                                                                                         | 0    | $V_{CCO} \ge 3.0V$      | -25   | -     | +25   | μA    |

|                                 |                                                                                           |                                                                                         |      | $V_{\rm CCO} < 3.0V$    | -10   | -     | +10   | μA    |

| C <sub>IN</sub>                 | Input capacitance                                                                         |                                                                                         |      | All                     | 3     | -     | 10    | pF    |

Notes:

1. The numbers in this table are based on the conditions set forth in Table 5.

2. This parameter is based on characterization.

# Table 7: Quiescent Supply Current Characteristics

|                           |                                           |          | Comm | nercial | Indu | strial |       |

|---------------------------|-------------------------------------------|----------|------|---------|------|--------|-------|

| Symbol                    | Description                               | Device   | Тур  | Max     | Тур  | Max    | Units |

| I <sub>CCINTQ</sub>       | Quiescent V <sub>CCINT</sub> supply       | XC3S50   | 10.0 |         |      |        | mA    |

|                           | current                                   | XC3S200  | 20.0 |         |      |        | mA    |

|                           |                                           | XC3S400  | 35.0 |         |      |        | mA    |

|                           |                                           | XC3S1000 | 65.0 |         |      |        | mA    |

|                           |                                           | XC3S1500 |      |         |      |        | mA    |

|                           |                                           | XC3S2000 |      |         |      |        | mA    |

|                           |                                           | XC3S4000 |      |         |      |        | mA    |

|                           |                                           | XC3S5000 |      |         |      |        | mA    |

| I <sub>CCOQ</sub> Quiesce | Quiescent V <sub>CCO</sub> supply current | XC3S50   | 1.5  |         |      |        | mA    |

|                           |                                           | XC3S200  | 1.5  |         |      |        | mA    |

|                           |                                           | XC3S400  | 1.5  |         |      |        | mA    |

|                           |                                           | XC3S1000 | 1.5  |         |      |        | mA    |

|                           |                                           | XC3S1500 |      |         |      |        | mA    |

|                           |                                           | XC3S2000 |      |         |      |        | mA    |

|                           |                                           | XC3S4000 |      |         |      |        | mA    |

|                           |                                           | XC3S5000 |      |         |      |        | mA    |

| I <sub>CCAUXQ</sub>       | Quiescent V <sub>CCAUX</sub> supply       | XC3S50   | 7.0  |         |      |        | mA    |

|                           | current                                   | XC3S200  | 15.0 |         |      |        | mA    |

|                           |                                           | XC3S400  | 20.0 |         |      |        | mA    |

|                           |                                           | XC3S1000 | 25.0 |         |      |        | mA    |

|                           |                                           | XC3S1500 |      |         |      |        | mA    |

|                           |                                           | XC3S2000 |      |         |      |        | mA    |

|                           |                                           | XC3S4000 |      |         |      |        | mA    |

|                           |                                           | XC3S5000 |      |         |      |        | mA    |

#### Notes:

The numbers in this table are based on the conditions set forth in Table 5. Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads disabled. For typical values, the ambient temperature (T<sub>A</sub>) is 25 °C with V<sub>CCINT</sub> = 1.2V, V<sub>CCO</sub> = 2.5V, and V<sub>CCAUX</sub> = 2.5V. The FPGA is programmed with a "blank" configuration data file (i.e., a design with no functional elements instantiated).

2. There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The Spartan-3 Web Power Tool at <u>http://www.xilinx.com/ise/power\_tools</u> provides quick, approximate, typical estimates, and does not require a netlist of the design. b) XPower, part of the Xilinx development software, takes a netlist as input to provide more accurate maximum and typical estimates.

# Table 8: Recommended Operating Conditions for User I/Os Using Single-Ended Standards

|                                                                       |         | V <sub>cco</sub> |         |         | V <sub>REF</sub> |         | V <sub>IL</sub>          | V <sub>IH</sub>          |  |

|-----------------------------------------------------------------------|---------|------------------|---------|---------|------------------|---------|--------------------------|--------------------------|--|

| Signal Standard                                                       | Min (V) | Nom (V)          | Max (V) | Min (V) | Nom (V)          | Max (V) | Max (V)                  | Min (V)                  |  |

| GTL <sup>(2)</sup>                                                    | -       | -                | -       | 0.74    | 0.8              | 0.86    | V <sub>REF</sub> - 0.05  | V <sub>REF</sub> + 0.05  |  |

| GTL_DCI                                                               | -       | 1.2              | -       | 0.74    | 0.8              | 0.86    | V <sub>REF</sub> - 0.05  | V <sub>REF</sub> + 0.05  |  |

| GTLP <sup>(2)</sup>                                                   | -       | -                | -       | 0.88    | 1                | 1.12    | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |  |

| GTLP_DCI                                                              | -       | 1.5              | -       | 0.88    | 1                | 1.12    | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |  |

| HSTL_I, HSTL_I_DCI                                                    | 1.4     | 1.5              | 1.6     | 0.68    | 0.75             | 0.9     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |  |

| HSTL_III,<br>HSTL_III_DCI                                             | 1.4     | 1.5              | 1.6     | 0.68    | 0.9              | 0.9     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |  |

| HSTL_I_18,<br>HSTL_I_DCI_18                                           | 1.7     | 1.8              | 1.9     | -       | 0.9              | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |  |

| HSTL_II_18,<br>HSTL_II_DCI_18                                         | 1.7     | 1.8              | 1.9     | -       | 0.9              | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |  |

| HSTL_III_18,<br>HSTL_III_DCI_18                                       | 1.7     | 1.8              | 1.9     | -       | 1.1              | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |  |

| LVCMOS12 <sup>(3)</sup>                                               | 1.14    | 1.2              | 1.3     | -       | -                | -       | 0.20V <sub>CCO</sub>     | 0.70V <sub>CCO</sub>     |  |

| LVCMOS15,<br>LVDCI_15,<br>LVDCI_DV2_15 <sup>(3)</sup>                 | 1.4     | 1.5              | 1.6     | -       | -                | -       | 0.20V <sub>CCO</sub>     | 0.70V <sub>CCO</sub>     |  |

| LVCMOS18,<br>LVDCI_18,<br>LVDCI_DV2_18 <sup>(3)</sup>                 | 1.7     | 1.8              | 1.9     | -       | -                | -       | 0.20V <sub>CCO</sub>     | 0.70V <sub>CCO</sub>     |  |

| LVCMOS25 <sup>(4)</sup> ,<br>LVDCI_25,<br>LVDCI_DV2_25 <sup>(3)</sup> | 2.3     | 2.5              | 2.7     | -       | -                | -       | 0.7                      | 1.7                      |  |

| LVCMOS33,<br>LVDCI_33,<br>LVDCI_DV2_33 <sup>(3)</sup>                 | 3.0     | 3.3              | 3.45    | -       | -                | -       | 0.8                      | 2.0                      |  |

| LVTTL                                                                 | 3.0     | 3.3              | 3.45    | -       | -                | -       | 0.8                      | 2.0                      |  |

| PCI33_3                                                               | -       | 3.0              | -       | -       | -                | -       | 0.30V <sub>CCO</sub>     | 0.50V <sub>CCO</sub>     |  |

| SSTL18_I,<br>SSTL18_I_DCI                                             | 1.65    | 1.8              | 1.95    | 0.825   | 0.9              | 0.975   | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 |  |

| SSTL2_I,<br>SSTL2_I_DCI                                               | 2.3     | 2.5              | 2.7     | 1.15    | 1.25             | 1.35    | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  |  |

| SSTL2_II,<br>SSTL2_II_DCI                                             | 2.3     | 2.5              | 2.7     | 1.15    | 1.25             | 1.35    | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  |  |

#### Notes:

1. Descriptions of the symbols used in this table are as follows:

V<sub>CCO</sub> -- the supply voltage for output drivers as well as LVCMOS, LVTTL, and PCI inputs

$V_{\text{REF}}$  -- the reference voltage for setting the input switching threshold  $V_{\text{IL}}$  -- the input voltage that indicates a Low logic level

VIH -- the input voltage that indicates a High logic level

Because the GTL and GTLP standards employ open-drain output buffers,  $V_{CCO}$  lines do not supply current to the I/O circuit, rather this current is provided using an external pull-up resistor connected from the I/O pin to a termination voltage ( $V_{TT}$ ). Nevertheless, the 2. voltage applied to the associated  $V_{CCO}$  lines must always be at or above  $V_{TT}$  and I/O pad voltages.

There is approximately 100 mV of hysteresis on inputs using any LVCMOS standard. З.

All Dedicated pins (M0-M2, CCLK, PROG\_B, DONE, HSWAP\_EN, TCK, TDI, TDO, and TMS) use the LVCMOS25 standard and draw 4. power from the V<sub>CCAUX</sub> rail (2.5V). The Dual-Purpose configuration pins (DIN/D0, D1-D7, CS\_B, RDWR\_B, BUSY/DOUT, and INIT\_B) use the LVCMOS25 standard before the User mode. For these pins, apply 2.5V to the V<sub>CCO</sub> Bank 4 and V<sub>CCO</sub> Bank 5 rails at power-on as well as throughout configuration. For information concerning the use of 3.3V signals, see the "3.3V-Tolerant Configuration Interface" section in Module 2

The global clock inputs have the following bank associations: GCLK0 and GCLK1 with Bank 4, GCLK2 and GCLK3 with Bank 5, 5. GCLK4 and GCLK5 with Bank 1, and GCLK6 and GCLK7 with Bank 0. The signal standards assigned to the Global Clock Lines (and I/Os) of a given bank determine the V<sub>CCO</sub> voltage for that bank.

# Table 9: DC Characteristics of User I/Os Using Single-Ended Standards

| Signal Standa             | rd and | Test Co         | nditions        | Logic Level (   | Characteristics        |  |

|---------------------------|--------|-----------------|-----------------|-----------------|------------------------|--|

| Current Drive A           |        | I <sub>OL</sub> | I <sub>ОН</sub> | V <sub>OL</sub> | V <sub>OH</sub>        |  |

| (mA)                      |        | (mA)            | (mA)            | Max (V)         | Min (V)                |  |

| GTL                       |        | 32              | -               | 0.4             | -                      |  |

| GTL_DCI                   |        | Note 3          | Note 3          | -               |                        |  |

| GTLP                      |        | 36              | -               | 0.6             | -                      |  |

| GTLP_DCI                  |        | Note 3          | Note 3          | -               |                        |  |

| HSTL_I                    |        | 8               | -8              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| HSTL_I_DCI                |        | Note 3          | Note 3          | -               |                        |  |

| HSTL_III                  |        | 24              | -8              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| HSTL_III_DCI              |        | Note 3          | Note 3          | -               |                        |  |

| HSTL_I_18                 |        | 8               | -8              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| HSTL_I_DCI_18             |        | Note 3          | Note 3          | -               | v <sub>CCO</sub> - 0.4 |  |

| HSTL_II_18                |        | 16              | -16             | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| HSTL_II_DCI_18            |        | Note 3          | Note 3          | 1               |                        |  |

| HSTL_III_18               |        | 24              | -8              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| HSTL_III_DCI_18           |        | Note 3          | Note 3          | ]               |                        |  |

| LVCMOS12 <sup>(4)</sup>   | 2      | 2               | -2              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| -                         | 4      | 4               | -4              | ]               |                        |  |

| -                         | 6      | 6               | -6              | -               |                        |  |

| LVCMOS15 <sup>(4)</sup>   | 2      | 2               | -2              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| _                         | 4      | 4               | -4              | -               |                        |  |

|                           | 6      | 6               | -6              | -               |                        |  |

| -                         | 8      | 8               | -8              | -               |                        |  |

| -                         | 12     | 12              | –12             | -               |                        |  |

| LVDCI_15,<br>LVDCI_DV2_15 |        | Note 3          | Note 3          |                 |                        |  |

| LVCMOS18 <sup>(4)</sup>   | 2      | 2               | -2              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| -                         | 4      | 4               | -4              | -               |                        |  |

|                           | 6      | 6               | -6              |                 |                        |  |

| -                         | 8      | 8               | -8              | ]               |                        |  |

|                           | 12     | 12              | –12             |                 |                        |  |

|                           | 16     | 16              | –16             |                 |                        |  |

| LVDCI_18,<br>LVDCI_DV2_18 |        | Note 3          | Note 3          |                 |                        |  |

| LVCMOS25 <sup>(4,5)</sup> | 2      | 2               | -2              | 0.4             | V <sub>CCO</sub> - 0.4 |  |

| -                         | 4      | 4               | -4              | 1               |                        |  |

| -                         | 6      | 6               | -6              | ]               |                        |  |

| -                         | 8      | 8               | -8              | ]               |                        |  |

|                           | 12     | 12              | -12             |                 |                        |  |

| -                         | 16     | 16              | -16             | 1               |                        |  |

|                           | 24     | 24              | -24             | 1               |                        |  |

| LVDCI_25,<br>LVDCI_DV2_25 |        | Note 3          | Note 3          |                 |                        |  |

| Signal Standa            | ard and | Test Co         | nditions        | Logic Level C           | haracteristics          |

|--------------------------|---------|-----------------|-----------------|-------------------------|-------------------------|

| Current Drive            |         | I <sub>OL</sub> | I <sub>ОН</sub> | V <sub>OL</sub>         | V <sub>OH</sub>         |

| (mA)                     |         | (mA)            | (mA)            | Max (V)                 | Min (V)                 |

| LVCMOS33 <sup>(4)</sup>  | 2       | 2               | -2              | 0.4                     | V <sub>CCO</sub> - 0.4  |

|                          | 4       | 4               | -4              | -                       |                         |

|                          | 6       | 6               | -6              | _                       |                         |

|                          | 8       | 8               | -8              | _                       |                         |

|                          | 12      | 12              | -12             |                         |                         |

|                          | 16      | 16              | -16             |                         |                         |

|                          | 24      | 24              | -24             |                         |                         |

| VDCI_33,<br>.VDCI_DV2_33 |         | Note 3          | Note 3          | _                       |                         |

| LVTTL <sup>(4)</sup>     | 2       | 2               | -2              | 0.4                     | 2.4                     |

|                          | 4       | 4               | -4              | _                       |                         |

|                          | 6       | 6               | -6              |                         |                         |

|                          | 8       | 8               | -8              |                         |                         |

|                          | 12      | 12              | -12             |                         |                         |

|                          | 16      | 16              | -16             |                         |                         |

|                          | 24      | 24              | -24             |                         |                         |

| PCI33_3                  |         | Note 6          | Note 6          | 0.10V <sub>CCO</sub>    | 0.90V <sub>CCO</sub>    |

| SSTL18_I                 |         | 6.7             | -6.7            | V <sub>TT</sub> - 0.475 | V <sub>TT</sub> + 0.475 |

| SSTL18_I_DCI             |         | Note 3          | Note 3          |                         |                         |

| SSTL2_I                  |         | 7.5             | -7.5            | V <sub>TT</sub> - 0.61  | V <sub>TT</sub> + 0.61  |

| SSTL2_I_DCI              |         | Note 3          | Note 3          |                         |                         |

| SSTL2_II                 |         | 15              | -15             | V <sub>TT</sub> - 0.80  | V <sub>TT</sub> + 0.80  |

| SSTL2_II_DCI             |         | Note 3          | Note 3          |                         |                         |

## Table 9: DC Characteristics of User I/Os Using Single-Ended Standards (Continued)

#### Notes:

The numbers in this table are based on the conditions set forth in Table 5 and Table 8. 1.

2.

Descriptions of the symbols used in this table are as follows:  $I_{OL}$  -- the output current condition under which  $V_{OL}$  is tested  $I_{OH}$  -- the output current condition under which  $V_{OH}$  is tested  $V_{OL}$  -- the output voltage that indicates a Low logic level  $V_{OH}$  -- the output voltage that indicates a High logic level  $V_{IL}$  -- the input voltage that indicates a High logic level  $V_{IL}$  -- the input voltage that indicates a High logic level  $V_{OL}$  -- the supply voltage that indicates a Well as LVCM

$V_{CCO}$  -- the supply voltage for output drivers as well as LVCMOS, LVTTL, and PCI inputs  $V_{REF}$  -- the reference voltage for setting the input switching threshold  $V_{TT}$  -- the voltage applied to a resistor termination

Tested according to the standard's relevant specifications. З.

For the LVCMOS and LVTTL standards: the same V<sub>OL</sub> and V<sub>OH</sub> limits apply for both the Fast and Slow slew attributes. 4.

- All Dedicated output pins (CCLK, DONE, and TDO) as well as Dual-Purpose totem-pole output pins (D0-D7 and BUSY/DOUT) 5. exhibit the characteristics of LVCMOS25 with 12 mA drive and Fast slew rate. For information concerning the use of 3.3V signals, see the "3.3V-Tolerant Configuration Interface" section in Module 2.

- Tested according to the relevant PCI specifications. 6.

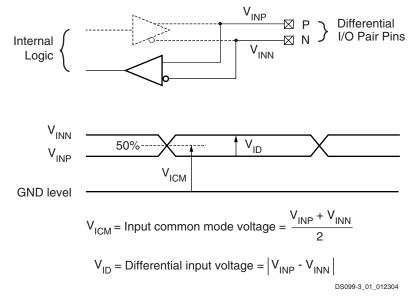

Figure 1: Differential Input Voltages

| Table 10: | Recommended Op   | perating Conditions | for User I/Os Usina  | Differential Signal Standards   |

|-----------|------------------|---------------------|----------------------|---------------------------------|

| 10010 10. | noooninnonaoa op | orading contaitione | ioi ocoi i/oc ociiig | Billorolliai Orginai Otaliaarao |

|                               |            | V <sub>CCO</sub> <sup>(1)</sup> |            |             | V <sub>ID</sub> |             |            | VICM       |            | V <sub>IH</sub> |            | V <sub>IL</sub> |            |

|-------------------------------|------------|---------------------------------|------------|-------------|-----------------|-------------|------------|------------|------------|-----------------|------------|-----------------|------------|

| Signal Standard               | Min<br>(V) | Nom<br>(V)                      | Max<br>(V) | Min<br>(mV) | Nom<br>(mV)     | Max<br>(mV) | Min<br>(V) | Nom<br>(V) | Max<br>(V) | Min<br>(V)      | Max<br>(V) | Min<br>(V)      | Max<br>(V) |

| LDT_25                        | 2.375      | 2.50                            | 2.625      | 200         | 600             | 1000        | 0.44       | 0.60       | 0.78       | -               | -          | -               | -          |

| LVDS_25,<br>LVDS_25_DCI       | 2.375      | 2.50                            | 2.625      | 100         | 350             | 600         | 0.30       | 1.25       | 2.20       | -               | -          | -               | -          |

| BLVDS_25                      | 2.375      | 2.50                            | 2.625      | -           | 350             | -           | -          | 1.25       | -          | -               | -          | -               | -          |

| LVDSEXT_25,<br>LVDSEXT_25_DCI | 2.375      | 2.50                            | 2.625      | 100         | 540             | 1000        | 0.30       | 1.20       | 2.20       | -               | -          | -               | -          |

| ULVDS_25                      | 2.375      | 2.50                            | 2.625      | 200         | 600             | 1000        | 0.44       | 0.60       | 0.78       | -               | -          | -               | -          |

| LVPECL_25                     | 2.375      | 2.50                            | 2.625      | 100         | -               | -           | -          | -          | -          | 0.8             | 2.0        | 0.5             | 1.7        |

| RSDS_25                       | 2.375      | 2.50                            | 2.625      | 100         | 200             | -           | -          | 1.20       | -          | -               | -          | -               | -          |

#### Notes:

1.

$V_{CCO}$  only supplies differential output drivers, not input circuits.  $V_{REF}$  inputs are not used for any of the differential I/O standards.  $V_{ID}$  is a differential measurement. 2.

З.

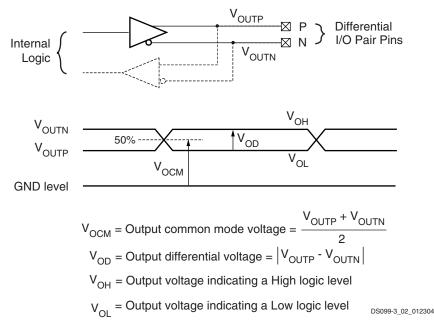

Figure 2: Differential Output Voltages

Table 11: DC Characteristics of User I/Os Using Differential Signal Standards

|                          |                    |                    | VOD         |             | ΔV          | ор          |            | V <sub>OCM</sub> |            | ΔV <sub>C</sub> | ОСМ         | v          | он         | ٧ <sub>c</sub> | DL         |

|--------------------------|--------------------|--------------------|-------------|-------------|-------------|-------------|------------|------------------|------------|-----------------|-------------|------------|------------|----------------|------------|

| Signal Standard          | Device<br>Revision | Min<br>(mV)        | Typ<br>(mV) | Max<br>(mV) | Min<br>(mV) | Max<br>(mV) | Min<br>(V) | Тур<br>(V)       | Max<br>(V) | Min<br>(mV)     | Max<br>(mV) | Min<br>(V) | Max<br>(V) | Min<br>(V)     | Max<br>(V) |

| LDT_25                   | All <sup>(3)</sup> | 430 <sup>(4)</sup> | 600         | 670         | -15         | 15          | 0.495      | 0.600            | 0.715      | -15             | 15          | -          | -          | -              | -          |

| LVDS_25                  | 0 <sup>(3)</sup>   | 100                | -           | 600         | -           | -           | 0.80       | -                | 1.6        | -               | -           | -          | -          | -              | -          |

|                          | Future             | 250                | -           | 400         | -           | -           | 1.125      | -                | 1.375      | -               | -           | 1.00       | 1.475      | 0.925          | 1.38       |

| BLVDS_25                 | All                | 250                | 350         | 450         | -           | -           | -          | 1.20             | -          | -               | -           | -          | -          | -              | -          |

| LVDSEXT_25               | 0(3)               | 100                | -           | 600         | -           | -           | 0.80       | -                | 1.6        | -               | -           | -          | -          | -              | -          |

|                          | Future             | 330                | -           | 700         | -           | -           | 1.125      | -                | 1.375      | -               | -           | -          | 1.700      | 0.705          | -          |

| ULVDS_25                 | All <sup>(3)</sup> | 430                | 600         | 670         | -           | -           | 0.495      | 0.600            | 0.715      | -               | -           | -          | -          | -              | -          |

| LVPECL_25 <sup>(7)</sup> | All                | -                  | -           | -           | -           | -           | -          | -                | -          | -               | -           | 1.35       | 1.745      | 0.565          | 1.005      |

| RSDS_25                  | 0 <sup>(3)</sup>   | 100                | -           | 600         | -           | -           | 0.80       | -                | 1.6        | -               | -           | -          | -          | -              | -          |

|                          | Future             | 100                | -           | 400         | -           | -           | 1.1        | -                | 1.4        | -               | -           | -          | -          | -              | -          |

#### Notes:

1. The numbers in this table are based on the conditions set forth in Table 5 and Table 10.

2.  $V_{OD}$ ,  $\Delta V_{OD}$ , and  $\Delta V_{OCM}$  are differential measurements.

For this standard, to ensure that the FPGA's output pair meets specifications, it is necessary to set the LVDSBIAS option in the BitGen utility, part of the Xilinx development software. See <u>XAPP751</u>. The option settings for LVDS\_25, LVDSEXT\_25, and RSDS\_25 are different from those for LDT\_25 and ULVDS\_25.

4. This value must be compatible with the receiver to which the FPGA's output pair is connected.

5. Output voltage measurements for all differential standards are made with a termination resistor (R<sub>T</sub>) of 100Ω across the N and P pins of the differential signal pair.

6. At any given time, only one differential standard may be assigned to each bank.

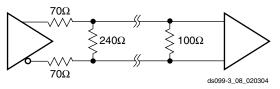

Each LVPECL output-pair requires three external resistors: a 70Ω resistor in series with each output followed by a 240Ω shunt resistor. These are in addition to the external 100Ω termination resistor at the receiver side. See Figure 3.

Figure 3: External Terminations for LVPECL

# **Switching Characteristics**

All Spartan-3 devices are available in two speed grades: -4 and the higher performance -5. Switching characteristics in this document may be designated as Advance, Preliminary, or Production. Each category is defined as follows:

**Advance**: These specifications are based on simulations only and are typically available soon after establishing FPGA specifications. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur. *All –5 grade numbers are engineering targets: characterization is still in progress.*

**Preliminary**: These specifications are based on complete early silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting preliminary delays is greatly reduced compared to Advance data.

**Production**: These specifications are approved once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

All specified limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the following applies: Parameter values apply to all Spartan-3 devices. All parameters representing voltages are measured with respect to GND.

Timing parameters and their representative values are selected for inclusion below either because they are important as general design requirements or they indicate fundamental device performance characteristics. The Spartan-3 speed files (V1.29), part of the Xilinx Development Software, are the original source for many but not all of the values. For more complete, more precise, and worst-case data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotated to the simulation netlist.

# I/O Timing

| Table | 12: | Pin-to-Pin | Clock-to-Output | Times for the | <b>IOB Output Path</b> |

|-------|-----|------------|-----------------|---------------|------------------------|

|-------|-----|------------|-----------------|---------------|------------------------|

|                       |                                                                                                                                                                                     |                                                       | Speed    |     | Grade |       |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------|-----|-------|-------|

|                       |                                                                                                                                                                                     |                                                       |          | -5  | -4    | 1     |

| Symbol                | Description                                                                                                                                                                         | Conditions                                            | Device   | Max | Max   | Units |

| Clock-to-Outpu        | it Times                                                                                                                                                                            | ·                                                     |          |     |       |       |

| T <sub>ICKOFDCM</sub> | When reading from the<br>Output Flip-Flop (OFF), the<br>time from the active<br>transition on the Global<br>Clock pin to data appearing<br>at the Output pin. The DCM<br>is in use. | LVCMOS25 <sup>(2)</sup> , 12mA                        | XC3S50   |     | 2.59  | ns    |

|                       |                                                                                                                                                                                     | output drive, Fast slew rate, with DCM <sup>(3)</sup> | XC3S200  |     | 2.59  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S400  |     | 2.59  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S1000 |     | 2.59  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S1500 |     | 2.60  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S2000 |     | 2.60  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S4000 |     | 2.60  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S5000 |     | 2.60  | ns    |

| T <sub>ICKOF</sub>    | When reading from OFF, the                                                                                                                                                          | LVCMOS25 <sup>(2)</sup> , 12mA                        | XC3S50   |     | 5.37  | ns    |

|                       | time from the active                                                                                                                                                                | output drive, Fast slew                               | XC3S200  |     | 5.39  | ns    |

|                       | transition on the Global<br>Clock pin to data appearing                                                                                                                             | rate, without DCM                                     | XC3S400  |     | 5.42  | ns    |

|                       | at the Output pin. The DCM                                                                                                                                                          |                                                       | XC3S1000 |     | 5.51  | ns    |

|                       | is not in use.                                                                                                                                                                      |                                                       | XC3S1500 |     | 5.65  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S2000 |     | 5.83  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S4000 |     | 5.95  | ns    |

|                       |                                                                                                                                                                                     |                                                       | XC3S5000 |     | 6.19  | ns    |

Notes:

1. The numbers in this table are tested using the methodology presented in Table 20 and are based on the operating conditions set forth in Table 5 and Table 8.

This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true, add the appropriate Input adjustment from Table 16. If the latter is true, add the appropriate Output adjustment from Table 19.

DCM output it inter is included in all measurements.

3. DCM output jitter is included in all measurements.

|                    |                                                                                                            |                                                                                    |          | Speed | Grade |       |  |

|--------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------|-------|-------|-------|--|

|                    |                                                                                                            |                                                                                    |          | -5    | -4    |       |  |

| Symbol             | Description                                                                                                | Conditions                                                                         | Device   | Min   | Min   | Units |  |

| Setup Times        |                                                                                                            |                                                                                    |          |       |       |       |  |

| T <sub>PSDCM</sub> | When writing to the Input                                                                                  | $LVCMOS25^{(2)},$                                                                  | XC3S50   |       | 2.72  | ns    |  |

|                    | Flip-Flop (IFF), the time from the setup of data at                                                        | IOBDELAY = NONE <sup><math>(4)</math></sup> , with DCM <sup><math>(5)</math></sup> | XC3S200  |       | 2.72  | ns    |  |

|                    | the Input pin to the active                                                                                |                                                                                    | XC3S400  |       | 2.74  | ns    |  |

|                    | transition at a Global                                                                                     |                                                                                    | XC3S1000 |       | 2.76  | ns    |  |

|                    | Clock pin. The DCM is in                                                                                   |                                                                                    | XC3S1500 |       | 2.86  | ns    |  |

|                    | use.                                                                                                       |                                                                                    | XC3S2000 |       | 2.98  | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S4000 |       | 3.06  | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S5000 |       | 3.23  | ns    |  |

| T <sub>PSFD</sub>  | When writing to IFF, the                                                                                   | LVCMOS25 <sup>(2)</sup> ,                                                          | XC3S50   |       | 2.43  | ns    |  |

|                    | time from the setup of<br>data at the Input pin to<br>an active transition at the<br>Global Clock pin. The | IOBDELAY = $NONE^{(4)}$ , without DCM                                              | XC3S200  |       | 3.53  | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S400  |       | 3.52  | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S1000 |       | 3.77  | ns    |  |

|                    | DCM is not in use.                                                                                         |                                                                                    | XC3S1500 |       | 4.15  | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S2000 |       | 4.34  | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S4000 |       | 4.53  | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S5000 |       | 4.90  | ns    |  |

| Hold Times         |                                                                                                            | +                                                                                  |          | •     | +     | -     |  |

| T <sub>PHDCM</sub> | When writing to IFF, the                                                                                   | LVCMOS25 <sup>(3)</sup> ,                                                          | XC3S50   |       | -1.81 | ns    |  |

|                    | time from the active                                                                                       | IOBDELAY = NONE <sup>(4)</sup> ,                                                   | XC3S200  |       | -1.81 | ns    |  |

|                    | transition at the Global<br>Clock pin to the point                                                         | with DCM <sup>(5)</sup>                                                            | XC3S400  |       | -1.81 | ns    |  |

|                    | when data must be held                                                                                     |                                                                                    | XC3S1000 |       | -1.81 | ns    |  |

|                    | at the Input pin. The                                                                                      |                                                                                    | XC3S1500 |       | -1.81 | ns    |  |

|                    | DCM is in use.                                                                                             |                                                                                    | XC3S2000 |       | -1.81 | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S4000 |       | -1.80 | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S5000 |       | -1.80 | ns    |  |

| T <sub>PHFD</sub>  | When writing to IFF, the                                                                                   | LVCMOS25 <sup>(3)</sup> ,                                                          | XC3S50   |       | -1.03 | ns    |  |

|                    | time from the active                                                                                       | $IOBDELAY = NONE^{(4)},$                                                           | XC3S200  |       | -1.89 | ns    |  |

|                    | transition at the Global<br>Clock pin to the point                                                         | without DCM                                                                        | XC3S400  |       | -1.87 | ns    |  |

|                    | when data must be held                                                                                     |                                                                                    | XC3S1000 |       | -2.01 | ns    |  |

|                    | at the Input pin. The                                                                                      |                                                                                    | XC3S1500 |       | -2.20 | ns    |  |

|                    | DCM is not in use.                                                                                         |                                                                                    | XC3S2000 |       | -2.20 | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S4000 |       | -2.24 | ns    |  |

|                    |                                                                                                            |                                                                                    | XC3S5000 |       | -2.32 | ns    |  |

# Table 13: Pin-to-Pin Setup and Hold Times for the IOB Input Path

Notes:

1. The numbers in this table are tested using the methodology presented in Table 20 and are based on the operating conditions set forth in Table 5 and Table 8.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, *subtract* the appropriate adjustment from Table 16. If this is true of the data Input, *add* the appropriate input adjustment from the same table.

3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, *add* the appropriate Input adjustment from Table 16. If this is true of the data Input, *subtract* the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

4. All numbers measured with no programmed input delay.

5. DCM output jitter is included in all measurements.

| Table 14: | Setup and Hold Times for the IOB Input Path |

|-----------|---------------------------------------------|

|-----------|---------------------------------------------|

|                      |                                                                                                                                                                    |                                              |          | Speed    | Grade    |       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------|----------|----------|-------|

|                      |                                                                                                                                                                    |                                              |          | -5       | -4       |       |

| Symbol               | Description                                                                                                                                                        | Conditions                                   | Device   | Min      | Min      | Units |

| Setup Times          |                                                                                                                                                                    |                                              |          | <u>.</u> | <u>.</u> |       |

| T <sub>IOPICK</sub>  | Time from the setup of data<br>at the Input pin to the active<br>transition at the ICLK input<br>of the Input Flip-Flop (IFF).<br>No input delay is<br>programmed. | LVCMOS25 <sup>(2)</sup> ,<br>IOBDELAY = NONE | All      | 1.15     | 1.32     | ns    |

| T <sub>IOPICKD</sub> | Time from the setup of data                                                                                                                                        |                                              | XC3S50   | 3.26     | 3.75     | ns    |

|                      | at the Input pin to the active transition at the IFF's ICLK                                                                                                        | IOBDELAY = IFD                               | XC3S200  | 3.89     | 4.47     | ns    |

|                      | input. The input delay is programmed.                                                                                                                              |                                              | XC3S400  | 3.89     | 4.47     | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S1000 | 4.15     | 4.77     | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S1500 | 4.32     | 4.97     | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S2000 | 4.50     | 5.17     | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S4000 | 4.67     | 5.37     | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S5000 | 5.02     | 5.77     | ns    |

| lold Times           |                                                                                                                                                                    | 1                                            |          | 1        |          | -1    |

| Т <sub>ЮІСКР</sub>   | Time from the active<br>transition at the IFF's ICLK<br>input to the point where<br>data must be held at the<br>Input pin. No input delay is<br>programmed.        | LVCMOS25 <sup>(3)</sup> ,<br>IOBDELAY = NONE | All      |          | -0.66    | ns    |

| T <sub>IOICKPD</sub> | Time from the active                                                                                                                                               | LVCMOS25 <sup>(3)</sup> ,                    | XC3S50   |          | -2.36    | ns    |

|                      | transition at the IFF's ICLK input to the point where                                                                                                              | IOBDELAY = IFD                               | XC3S200  |          | -2.87    | ns    |

|                      | data must be held at the                                                                                                                                           |                                              | XC3S400  |          | -2.87    | ns    |

|                      | Input pin. The input delay is programmed.                                                                                                                          |                                              | XC3S1000 |          | -3.08    | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S1500 |          | -3.22    | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S2000 |          | -3.36    | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S4000 |          | -3.50    | ns    |

|                      |                                                                                                                                                                    |                                              | XC3S5000 |          | -3.78    | ns    |

Notes:

1. The numbers in this table are tested using the methodology presented in Table 20 and are based on the operating conditions set forth in Table 5 and Table 8.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, *add* the appropriate Input adjustment from Table 16.

3. These hold times require adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, *subtract* the appropriate Input adjustment from Table 16. When the hold time is negative, it is possible to change the data before the clock's active edge.

|                     |                                                                                                                                          |                                              |          | Speed |      |       |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------|-------|------|-------|

|                     |                                                                                                                                          |                                              |          | -5    | -4   |       |

| Symbol              | Description                                                                                                                              | Conditions                                   | Device   | Max   | Max  | Units |

| Propagation T       | imes                                                                                                                                     |                                              |          |       |      |       |

| T <sub>IOPI</sub>   | The time it takes for data<br>to travel from the Input<br>pin to the IOB's I output<br>with no input delay<br>programmed                 | LVCMOS25 <sup>(2)</sup> ,<br>IOBDELAY = NONE | All      | 1.05  | 1.20 | ns    |

| T <sub>IOPID</sub>  | The time it takes for data                                                                                                               | IOBDELAY = IFD                               | XC3S50   | 3.16  | 3.63 | ns    |

|                     | to travel from the Input<br>pin to the I output with the                                                                                 |                                              | XC3S200  | 3.79  | 4.35 | ns    |

|                     | Input delay programmed                                                                                                                   |                                              | XC3S400  | 3.79  | 4.35 | ns    |

|                     |                                                                                                                                          |                                              | XC3S1000 | 4.05  | 4.65 | ns    |

|                     |                                                                                                                                          |                                              | XC3S1500 | 4.22  | 4.85 | ns    |

|                     |                                                                                                                                          |                                              | XC3S2000 | 4.40  | 5.05 | ns    |

|                     |                                                                                                                                          |                                              | XC3S4000 | 4.57  | 5.25 | ns    |

|                     |                                                                                                                                          |                                              | XC3S5000 | 4.92  | 5.65 | ns    |

| T <sub>IOPLI</sub>  | The time it takes for data<br>to travel from the Input<br>pin through the IFF latch<br>to the I output with no<br>input delay programmed | LVCMOS25 <sup>(2)</sup> ,<br>IOBDELAY = NONE | All      | 1.55  | 1.78 | ns    |

| T <sub>IOPLID</sub> | The time it takes for data                                                                                                               | LVCMOS25 <sup>(2)</sup> ,                    | XC3S50   | 3.66  | 4.21 | ns    |

|                     | to travel from the Input<br>pin through the IFF latch                                                                                    | IOBDELAY = IFD                               | XC3S200  | 4.29  | 4.93 | ns    |

|                     | to the I output with the                                                                                                                 |                                              | XC3S400  | 4.29  | 4.93 | ns    |

|                     | input delay programmed                                                                                                                   |                                              | XC3S1000 | 4.55  | 5.23 | ns    |

|                     |                                                                                                                                          |                                              | XC3S1500 | 4.73  | 5.43 | ns    |

|                     |                                                                                                                                          |                                              | XC3S2000 | 4.90  | 5.63 | ns    |

|                     |                                                                                                                                          |                                              | XC3S4000 | 5.07  | 5.83 | ns    |

|                     |                                                                                                                                          |                                              | XC3S5000 | 5.42  | 6.23 | ns    |

# Table 15: Propagation Times for the IOB Input Path

Notes:

1. The numbers in this table are tested using the methodology presented in Table 20 and are based on the operating conditions set forth in Table 5 and Table 8.

2. This propagation time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. When this is true, *add* the appropriate Input adjustment from Table 16.

# Table 16: Input Timing Adjustments for IOB

|                                            |       | l the<br>ent Below |       |

|--------------------------------------------|-------|--------------------|-------|

| Convert Input Time from<br>LVCMOS25 to the | Speed |                    |       |

| Following Signal Standard                  | -5    | -4                 | Units |

| Single-Ended Standards                     |       |                    |       |

| GTL, GTL_DCI                               | -0.37 | -0.37              | ns    |

| GTLP, GTLP_DCI                             | -0.37 | -0.37              | ns    |

| HSTL_I, HSTL_I_DCI                         | -0.18 | -0.18              | ns    |

| HSTL_III, HSTL_III_DCI                     | -0.19 | -0.19              | ns    |

| HSTL_I_18,<br>HSTL_I_DCI_18                | -0.26 | -0.26              | ns    |

| HSTL_II_18,<br>HSTL_II_DCI_18              | -0.26 | -0.26              | ns    |

| HSTL_III_18,<br>HSTL_III_DCI_18            | -0.20 | -0.20              | ns    |

| LVCMOS12                                   | 0.40  | 0.40               | ns    |

| LVCMOS15, LVDCI_15,<br>LVDCI_DV2_15        | 0.47  | 0.47               | ns    |

| LVCMOS18, LVDCI_18,<br>LVDCI_DV2_18        | 0.30  | 0.30               | ns    |

| LVCMOS25, LVDCI_25,<br>LVDCI_DV2_25        | 0     | 0                  | ns    |

| LVCMOS33, LVDCI_33,<br>LVDCI_DV2_33        | 0.09  | 0.09               | ns    |

| LVTTL                                      | -0.31 | -0.31              | ns    |

## Table 16: Input Timing Adjustments for IOB (Continued)

|                                            | ,     | the<br>ent Below |       |

|--------------------------------------------|-------|------------------|-------|

| Convert Input Time from<br>LVCMOS25 to the | Speed | Grade            |       |

| Following Signal Standard                  | -5    | -4               | Units |

| PCI33_3                                    | 0.32  | 0.32             | ns    |

| SSTL18_I, SSTL18_I_DCI                     | -0.17 | -0.17            | ns    |

| SSTL2_I, SSTL2_I_DCI                       | -0.19 | -0.19            | ns    |

| SSTL2_II, SSTL2_II_DCI                     | -0.21 | -0.21            | ns    |