## Spansion<sup>®</sup> Analog and Microcontroller Products

The following document contains information on Spansion analog and microcontroller products. Although the document is marked with the name "Fujitsu", the company that originally developed the specification, Spansion will continue to offer these products to new and existing customers.

#### **Continuity of Specifications**

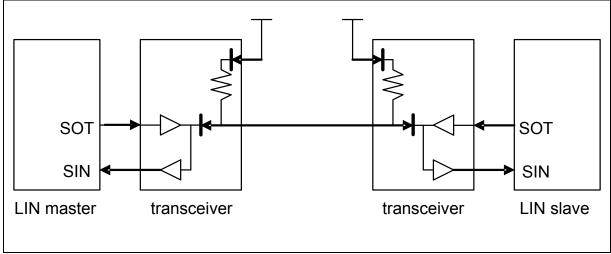

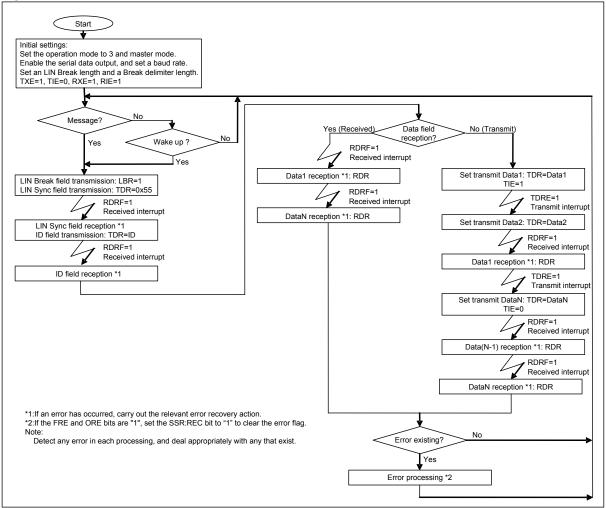

There is no change to this document as a result of offering the device as a Spansion product. Any changes that have been made are the result of normal document improvements and are noted in the document revision summary, where supported. Future routine revisions will occur when appropriate, and changes will be noted in a revision summary.

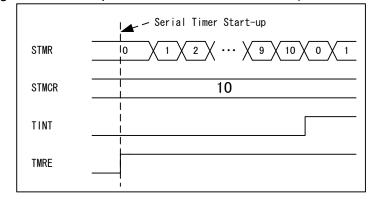

#### **Continuity of Ordering Part Numbers**

Spansion continues to support existing part numbers beginning with "MB". To order these products, please use only the Ordering Part Numbers listed in this document.

#### **For More Information**

Please contact your local sales office for additional information about Spansion memory, analog, and microcontroller products and solutions.

MN709-00004-1v0-E

FUJITSU SEMICONDUCTOR CONTROLLER MANUAL

# 32-BIT MICROCONTROLLER FM4 Family PERIPHERAL MANUAL Communication Macro Part

For the latest information for microcontroller supports, see the following web site.

http://edevice.fujitsu.com/micom/en-support/

FUJITSU SEMICONDUCTOR LIMITED

## Preface

Thank you for your continued use of Fujitsu semiconductor products.

Read this manual and "Data Sheet" thoroughly before using products in this family. In addition, this manual is defined as separate volume which is extracted the Communication Macro

part from the peripheral manual.

#### Purpose of this manual and intended readers

This manual explains the functions and operations of this family and describes how it is used. The manual is intended for engineers engaged in the actual development of products using this family.

\* This manual explains the configuration and operation of the peripheral functions, but does not cover the specifics of each device in the series. Users should refer to the respective data sheets of devices for device-specific details.

#### Trademark

ARM and Cortex are the trademarks of ARM Limited in the EU and other countries.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

#### Sample programs and development environment

Fujitsu Semiconductor offers sample programs free of charge for using the peripheral functions of the FM4 family. Fujitsu Semiconductor also makes available descriptions of the development environment required for this series. Feel free to use them to verify the operational specifications and usage of this Fujitsu Semiconductor microcontroller.

Microcontroller support information: http://edevice.fujitsu.com/micom/en-support/

\* : Note that the sample programs are subject to change without notice. Since they are offered as a way to demonstrate standard operations and usage, evaluate them sufficiently before running them on your system.

Fujitsu Semiconductor assumes no responsibility for any damage that may occur as a result of using a sample program.

#### Overall Organization of This Manual

Peripheral Manual Timer Part has 4 chapters and APPENDIXES as shown below.

CHAPTER 1-1 : Multi-function Serial Interface

CHAPTER 1-2 : UART (Asynchronous Serial Interface)

CHAPTER 1-3 : CSIO (Clock Synchronous Serial Interface)

CHAPTER 1-4 : LIN Interface (Ver. 2.1) (LIN Communication Control Interface Ver. 2.1)

CHAPTER 1-5 : I<sup>2</sup>C Interface (I<sup>2</sup>C Communications Control Interface)

CHAPTER 2-1 : USB/Ethernet Clock Generation Block

CHAPTER 2-2 : USB Clock Generation

CHAPTER 2-3 : USB/Ethernet Clock Generation

CHAPTER 3-1 : USB Function

CHAPTER 3-2 : USB Host CHAPTER 4-1 : Can Prescaler CHAPTER 4-2 : CAN Controller

APPENDIXES

- FUJITSU SEMICONDUCTOR LIMITED, its subsidiaries and affiliates (collectively, "FUJITSU SEMICONDUCTOR") reserves the right to make changes to the information contained in this document without notice. Please contact your FUJITSU SEMICONDUCTOR sales representatives before order of FUJITSU SEMICONDUCTOR device.

- Information contained in this document, such as descriptions of function and application circuit examples is presented solely for reference to examples of operations and uses of FUJITSU SEMICONDUCTOR device. FUJITSU SEMICONDUCTOR disclaims any and all warranties of any kind, whether express or implied, related to such information, including, without limitation, quality, accuracy, performance, proper operation of the device or non-infringement. If you develop equipment or product incorporating the FUJITSU SEMICONDUCTOR device based on such information, you must assume any responsibility or liability arising out of or in connection with such information or any use thereof. FUJITSU SEMICONDUCTOR assumes no responsibility or liability for any damages whatsoever arising out of or in connection with such information or any use thereof.

- Nothing contained in this document shall be construed as granting or conferring any right under any patents, copyrights, or any other intellectual property rights of FUJITSU SEMICONDUCTOR or any third party by license or otherwise, express or implied. FUJITSU SEMICONDUCTOR assumes no responsibility or liability for any infringement of any intellectual property rights or other rights of third parties resulting from or in connection with the information contained herein or use thereof.

- The products described in this document are designed, developed and manufactured as contemplated for general use including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high levels of safety is secured, could lead directly to death, personal injury, severe physical damage or other loss (including, without limitation, use in nuclear facility, aircraft flight control system, air traffic control system, mass transport control system, medical life support system and military application), or (2) for use requiring extremely high level of reliability (including, without limitation, submersible repeater and artificial satellite). FUJITSU SEMICONDUCTOR shall not be liable for you and/or any third party for any claims or damages arising out of or in connection with above-mentioned uses of the products.

- Any semiconductor devices fail or malfunction with some probability. You are responsible for providing adequate designs and safeguards against injury, damage or loss from such failures or malfunctions, by incorporating safety design measures into your facility, equipments and products such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

- The products and technical information described in this document are subject to the Foreign Exchange and Foreign Trade Control Law of Japan, and may be subject to export or import laws or regulations in U.S. or other countries. You are responsible for ensuring compliance with such laws and regulations relating to export or re-export of the products and technical information described herein.

- All company names, brand names and trademarks herein are property of their respective owners.

Copyright ©2013 FUJITSU SEMICONDUCTOR LIMITED All rights reserved.

## **Related Manuals**

The manuals related to this family are listed below. See the manual appropriate to the applicable conditions.

The contents of these manuals are subject to change without notice. Contact us to check the latest versions available.

#### Peripheral Manual

- FM4 Family PERIPHERAL MANUAL

- (Called "PERIPHERAL MANUAL" hereafter)

- FM4 Family PERIPHERAL MANUAL Timer Part (Called "Timer Part" hereafter)

- FM4 Family PERIPHERAL MANUAL Analog Macro Part (Called "Analog Macro Part" hereafter)

- FM4 Family PERIPHERAL MANUAL Communication Macro Part (this manual) (Called "Communication Macro Part" hereafter)

#### Data sheet

For details about device-specific, electrical characteristics, package dimensions, ordering information etc., see the following document.

#### · 32-bit Microcontroller FM4 Family DATA SHEET

\* The data sheets for each series are provided. See the appropriate data sheet for the series that you are using.

#### ■ CPU Programming manual

For details about ARM Cortex-M4F core, see the following documents that can be obtained from http://www.arm.com/.

- · Cortex-M4 Technical Reference Manual

- · ARMv7-M Architecture Application Level Reference Manual

#### Flash Programming manual

For details about the functions and operations of the built-in flash memory, see the following document.

#### · FM4 Family FLASH PROGRAMMING MANUAL

\* The Flash Programming manuals for each series are provided. See the appropriate Flash Programming manual for the series that you are using.

## How to Use This Manual

#### Finding a function

The following methods can be used to search for the explanation of a desired function in this manual:

- Search from the table of the contents The table of the contents lists the manual contents in the order of description.

- Search from the register

The address where each register is located is not described in the text. To verify the address of a register, see "A. Register Map" in "APPENDIXES".

#### About the chapters

Basically, this manual explains Communication Macro Part.

#### Terminology

This manual uses the following terminology.

| Term      | Explanation                           |

|-----------|---------------------------------------|

| Word      | Indicates access in units of 32 bits. |

| Half word | Indicates access in units of 16 bits. |

| Byte      | Indicates access in units of 8 bits.  |

#### Notations

- · The notations in bit configuration of the register explanation of this manual are written as follows.

- bit : bit number

- · Field : bit field name

- · Attribute : Attributes for read and write of each bit

- $\cdot$  R : Read only

- $\cdot$  W : Write only

- · R/W : Readable/Writable

- · : Undefined

- · Initial value : Initial value of the register after reset

- 0 : Initial value is "0"

- 1 : Initial value is "1"

- X : Initial value is undefined

- The multiple bits are written as follows in this manual. Example : bit7:0 indicates the bits from bit7 to bit0

- The values such as for addresses are written as follows in this manual.

- Hexadecimal number : "0x" is attached in the beginning of a value as a prefix (example : 0xFFFF)

- Binary number : "0b" is attached in the beginning of a value as a prefix (example: 0b1111)

- Decimal number : Written using numbers only (example : 1000)

## CONTENTS

| CHAPTER 1-1: Multi-function Serial Interface                                                                           | 1   |

|------------------------------------------------------------------------------------------------------------------------|-----|

| 1. Overview of the Multi-function Serial Interface                                                                     | 2   |

| CHAPTER 1-2: UART (Asynchronous Serial Interface)                                                                      | 5   |

| 1. Overview of UART (Asynchronous Serial Interface)                                                                    | 6   |

| 2. UART Interrupt                                                                                                      | 7   |

| 2.1. Received interrupt and flag set timing                                                                            | 8   |

| 2.2. Interrupt and flag set timing when received FIFO is used                                                          | 10  |

| 2.3. Transmit interrupt and flag set timing                                                                            |     |

| 2.4. Interrupt and flag set timing when transmit FIFO is used                                                          | 13  |

| 3. UART Operation                                                                                                      | 14  |

| 4. Dedicated Baud Rate Generator                                                                                       | 22  |

| 4.1. Baud rate settings                                                                                                | 23  |

| 5. Setting Procedure and Program Flow in Operation Mode 0<br>(Asynchronous Normal Mode)                                | .28 |

| 6. Setting Procedure and Program Flow in Operation Mode 1                                                              |     |

| (Asynchronous Multiprocessor Mode)                                                                                     | 31  |

| 7. UART (Asynchronous Serial Interface) Registers                                                                      | 35  |

| 7.1. Serial Control Register (SCR)                                                                                     | 36  |

| 7.2. Serial Mode Register (SMR)                                                                                        |     |

| 7.3. Serial Status Register (SSR)                                                                                      |     |

| 7.4. Extended Communication Control Register (ESCR)                                                                    |     |

| 7.5. Received Data Register/Transmit Data Register (RDR/TDR)                                                           |     |

| 7.6. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)                                                             |     |

| 7.7. FIFO Control Register 1 (FCR1)                                                                                    |     |

| 7.8. FIFO Control Register 0 (FCR0)                                                                                    |     |

| 7.9. FIFO Byte Register (FBYTE)                                                                                        | 57  |

| CHAPTER 1-3: CSIO (Clock Synchronous Serial Interface)                                                                 |     |

| 1. Overview of CSIO (Clock Synchronous Serial Interface)                                                               |     |

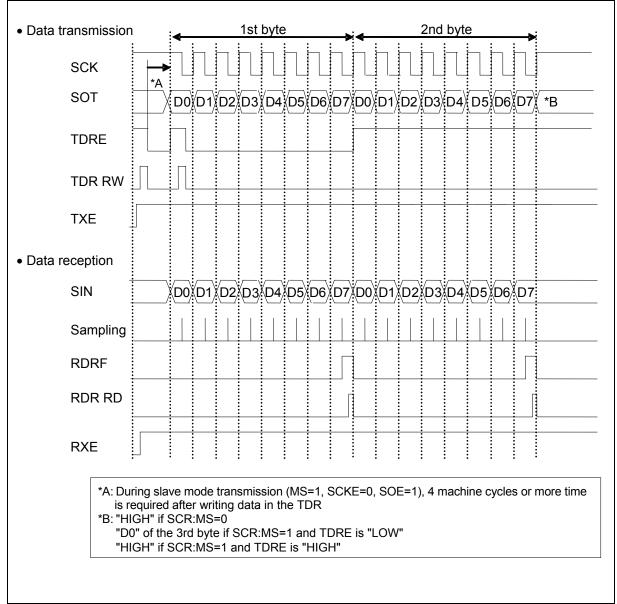

| 2. CSIO (Clock Synchronous Serial Interface) interrupts                                                                |     |

| 2.1. Received interrupt and flag set timing                                                                            |     |

| 2.2. Interrupt and flag set timing when received FIFO is used                                                          |     |

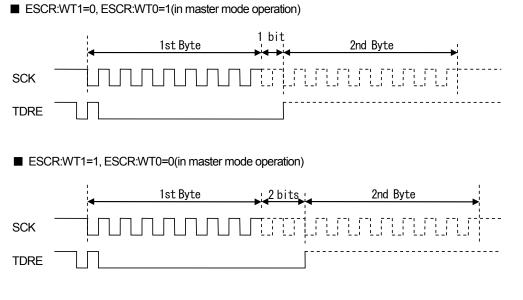

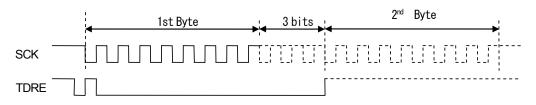

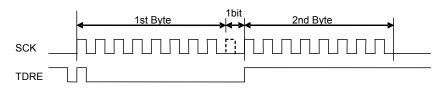

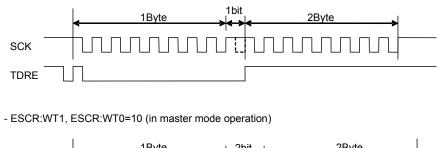

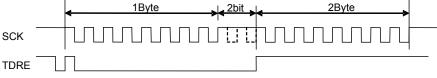

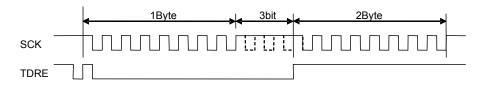

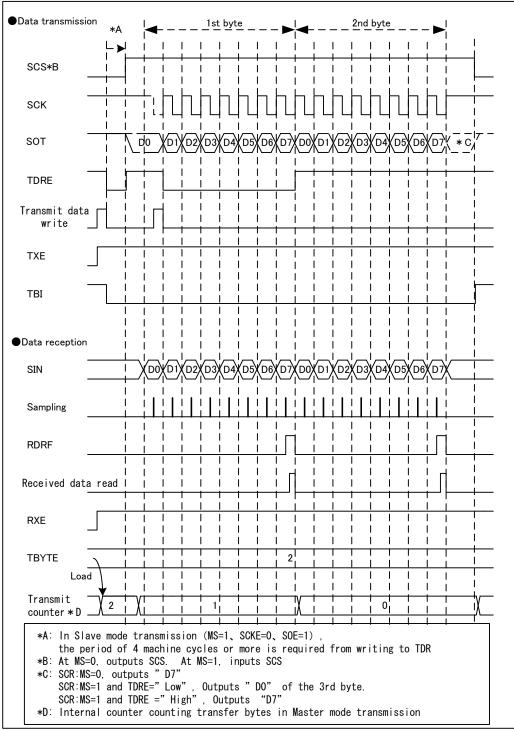

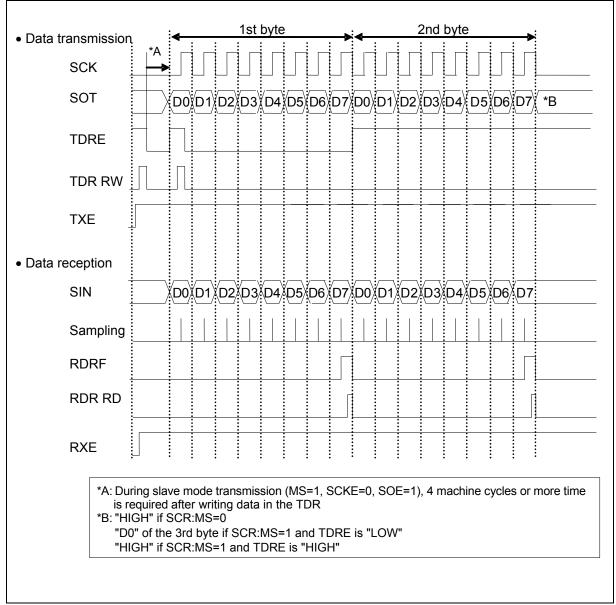

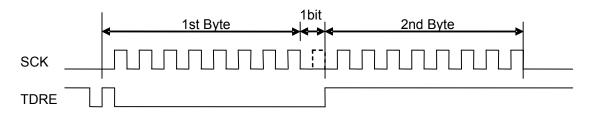

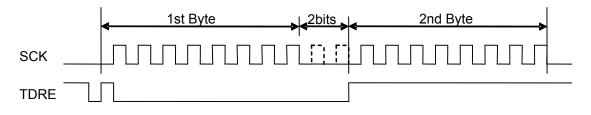

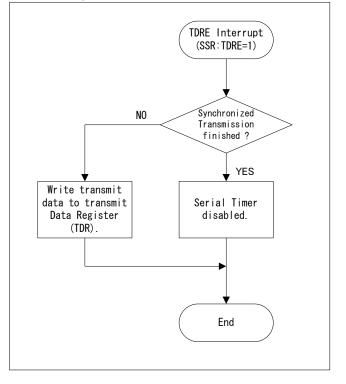

| 2.3. Transmit interrupt and flag set timing                                                                            |     |

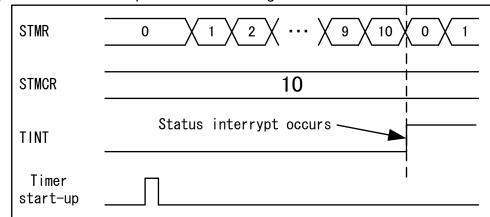

| 2.4. Interrupt and flag set timing when transmit FIFO is used<br>2.5. Timer Interrupt Occurene and Flag Setting Timing |     |

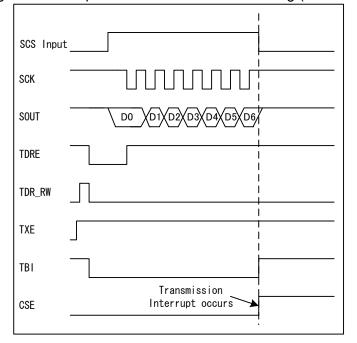

| 2.6. Chip Select Error Occurrence and Flag Setting Timing                                                              |     |

| 3. CSIO (Clock Synchronous Serial Interface) operations                                                                |     |

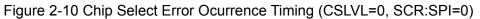

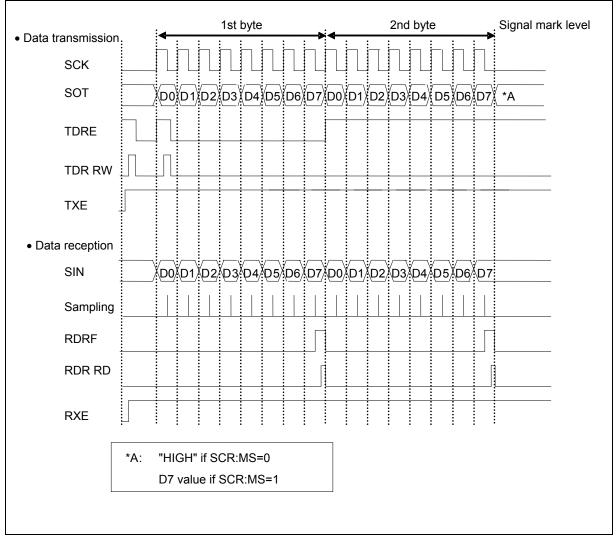

| 3.1. Normal transfer (I)                                                                                               |     |

| 3.2. Normal transfer (II)                                                                                              |     |

| 3.3. SPI transfer (I)                                                                                                  |     |

| 3.4. SPI transfer (II)                                                                                                 |     |

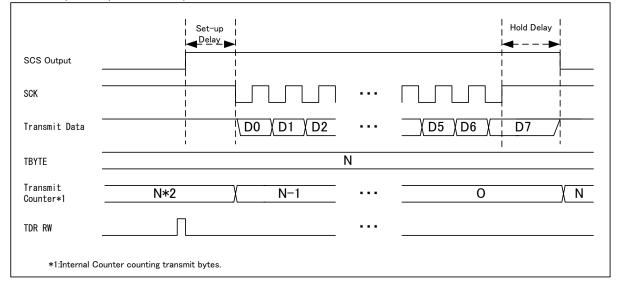

| 4. Serial Timer Operation                                                                                              |     |

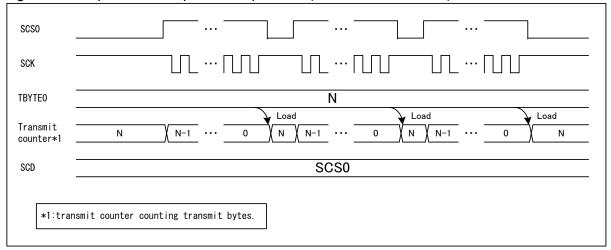

| 5. Serial Chip Select Operation1                                                                                       |     |

| 6. Dedicated baud rate generator1                                                                                      |     |

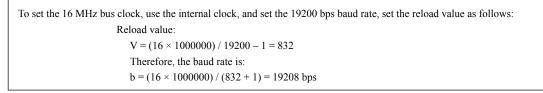

| 6.1. Baud rate settings                                                                                                |     |

| 6.2. CSIO (Clock Synchronous Serial Interface) setup procedure<br>and program flow            | 128 |

|-----------------------------------------------------------------------------------------------|-----|

| 7. CSIO (Clock Synchronous Serial Interface) registers                                        |     |

| 7.1. Serial Control Register (SCR)                                                            |     |

| 7.2. Serial Mode Register (SMR)                                                               |     |

| 7.3. Serial Status Register (SSR)                                                             |     |

| 7.4. Extended Communication Control Register (ESCR)                                           |     |

| 7.5. Received Data Register/Transmit Data Register (RDR/TDR)                                  |     |

| 7.6. Serial Support Control Register (SACSR)                                                  |     |

| 7.7. Serial Timer Register (STMR)                                                             |     |

| 7.8. Serial Timer Comparison Register (STMCR)                                                 | 150 |

| 7.9. Serial Chip Select Control Status Register (SCSCR)                                       | 151 |

| 7.10. Serial Chip Select Timing Register (SCSTR3:0)                                           |     |

| 7.11. Transfer Byte Register (TBYTE0)                                                         | 157 |

| 7.12. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)                                   | 158 |

| 7.13. FIFO Control Register 1 (FCR1)                                                          | 159 |

| 7.14. FIFO Control Register 0 (FCR0)                                                          | 161 |

| 7.15. FIFO Byte Register (FBYTE)                                                              | 165 |

| 8. Restrictions on CSIO (Clock Synchronous Serial Interface)                                  | 167 |

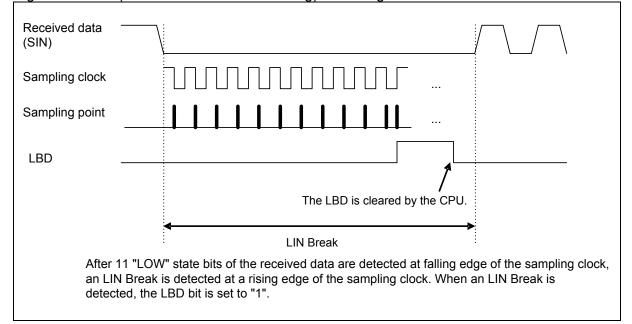

| CHAPTER 1-4: LIN Interface (Ver. 2.1)<br>(LIN Communication Control Interface Ver. 2.1)       | 169 |

| 1. Overview of LIN Interface (Ver. 2.1)<br>(LIN Communication Control Interface Ver. 2.1)     | 170 |

| 2. LIN Interface (Ver. 2.1) Interrupts                                                        | 171 |

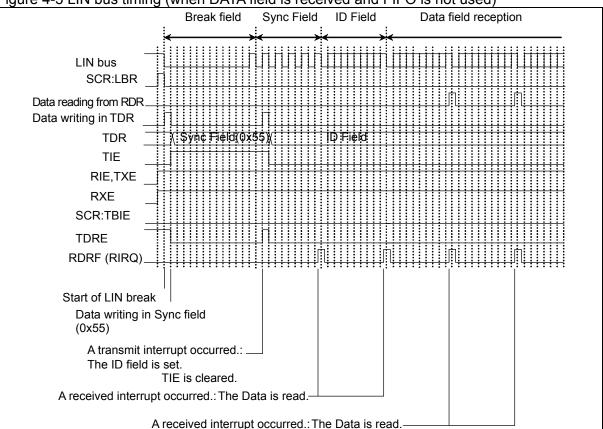

| 2.1. Received interrupt and flag set timing                                                   | 172 |

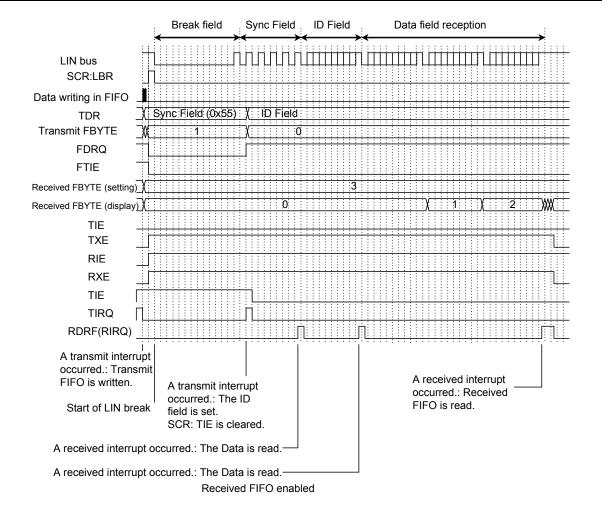

| 2.2. Interrupt and flag set timing when received FIFO is used                                 | 174 |

| 2.3. Transmit interrupt and flag set timing                                                   |     |

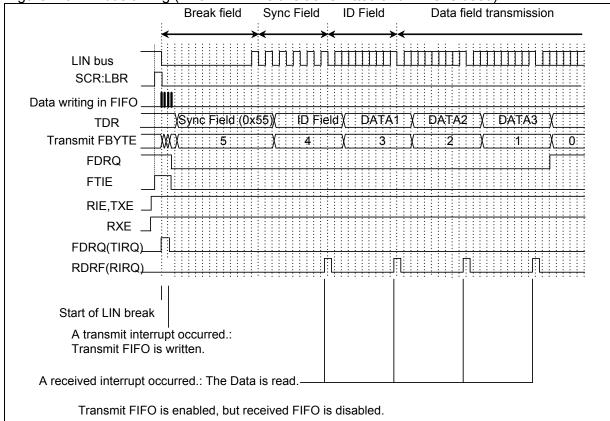

| 2.4. Interrupt and flag set timing when transmit FIFO is used                                 | 177 |

| 3. Dedicated Baud Rate Generator                                                              | 178 |

| 3.1. Baud rate settings                                                                       | 179 |

| 4. LIN Interface (Ver. 2.1) Operations                                                        | 184 |

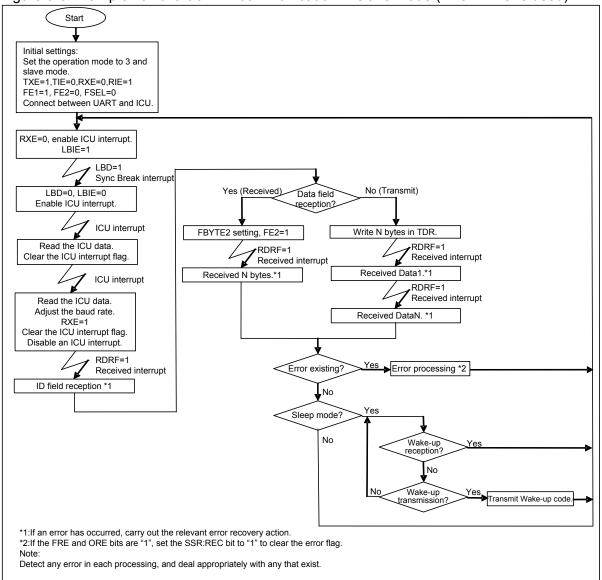

| 5. Operation Mode 3 (LIN Communication Mode) Setting Procedure                                |     |

| and Program Flow                                                                              | 194 |

| 6. LIN Interface (ver. 2.1) Registers                                                         |     |

| 6.1. Serial Control Register (SCR)                                                            |     |

| 6.2. Serial Mode Register (SMR)                                                               |     |

| 6.3. Serial Status Register (SSR)                                                             |     |

| 6.4. Extended Communication Control Register (ESCR)                                           |     |

| 6.5. Received Data Register/Transmit Data Register (RDR/TDR)                                  | 210 |

| 6.6. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)                                    | 212 |

| 6.7. FIFO Control Register 1 (FCR1)                                                           | 214 |

| 6.8. FIFO Control Register 0 (FCR0)                                                           | 216 |

| 6.9. FIFO Byte Register (FBYTE)                                                               | 220 |

| CHAPTER 1-5: I <sup>2</sup> C Interface (I <sup>2</sup> C Communications Control Interface)   |     |

| 1. Overview of I <sup>2</sup> C Interface (I <sup>2</sup> C Communications Control Interface) | 224 |

| 2. I <sup>2</sup> C Interface interrupt                                                       | 225 |

| 2.1. I <sup>2</sup> C interface operation                                                     |     |

| 2.2. Master mode                                                                              | 228 |

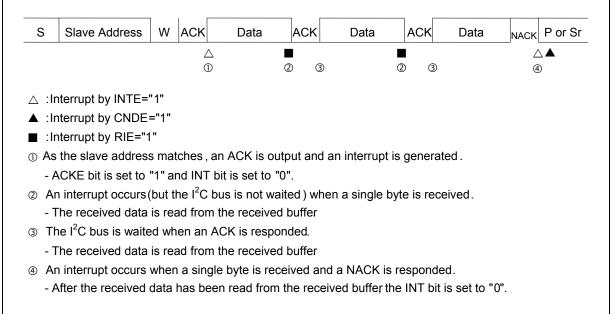

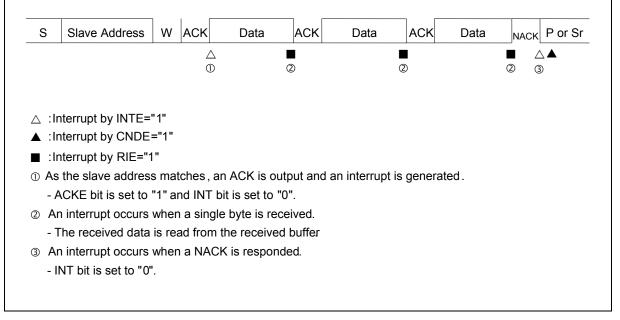

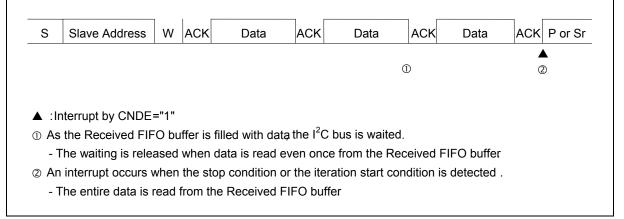

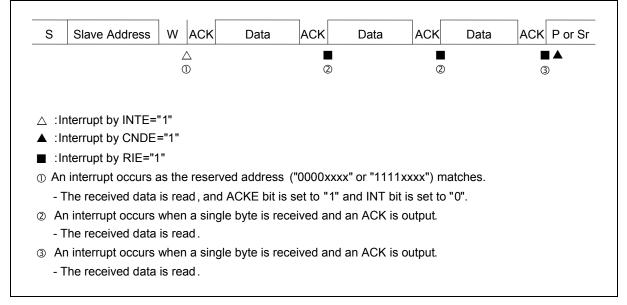

| 2.3. Slave mode                                                                                   |     |

|---------------------------------------------------------------------------------------------------|-----|

| 2.4. Bus error                                                                                    |     |

| 3. Dedicated Baud Rate Generator                                                                  |     |

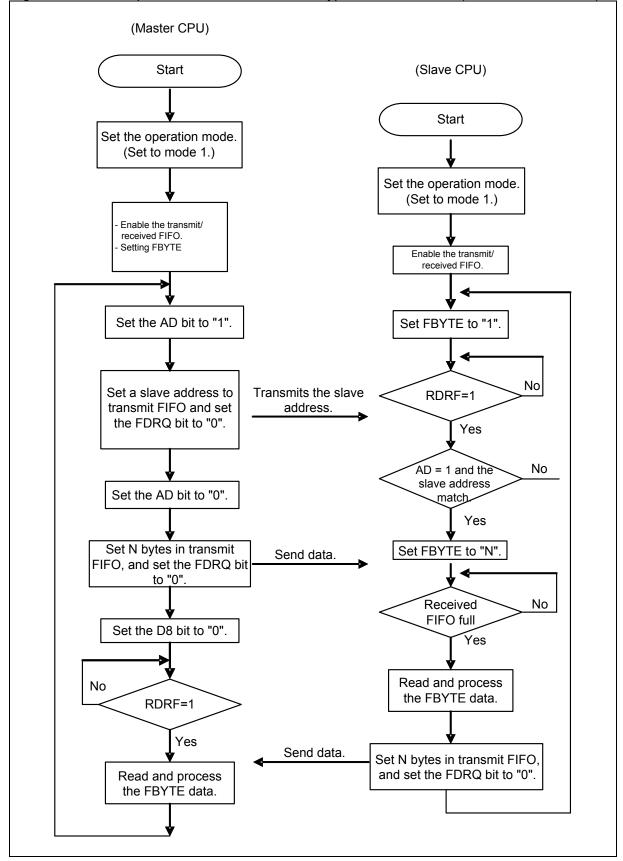

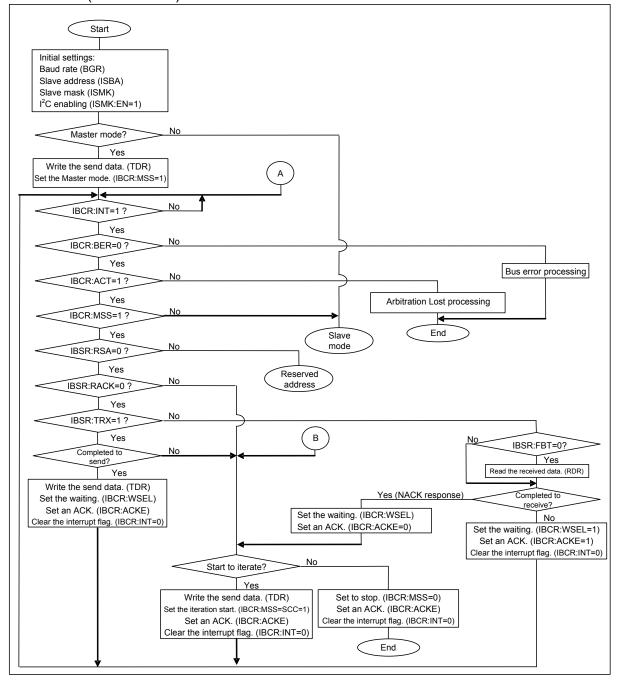

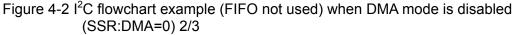

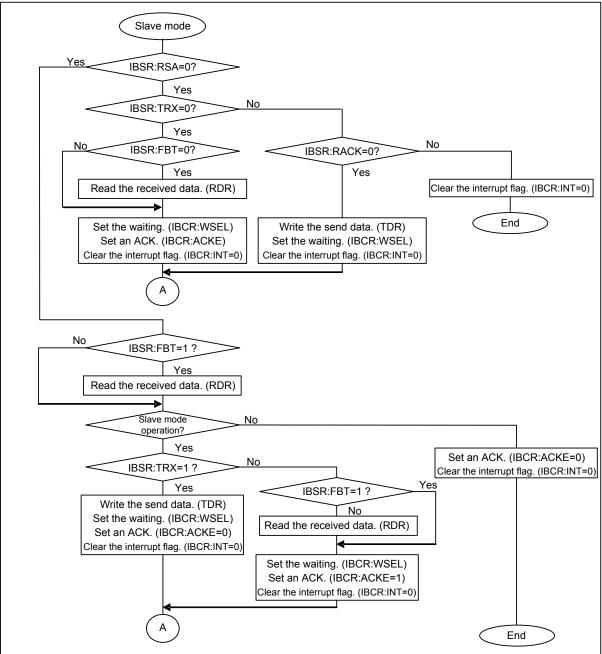

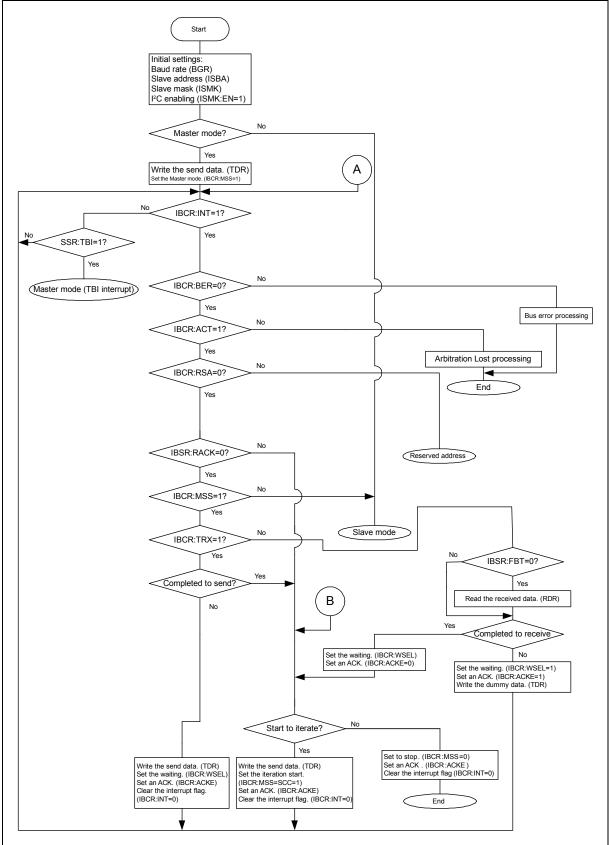

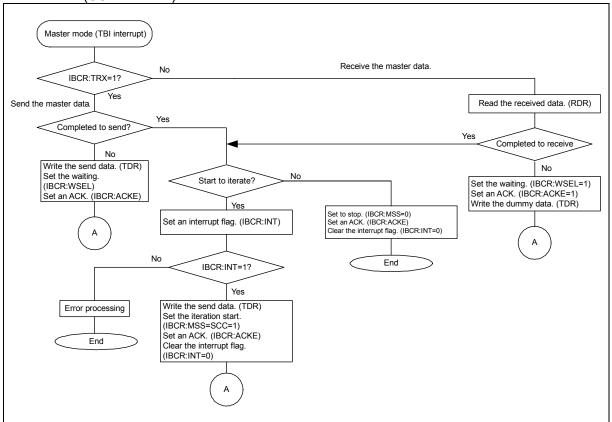

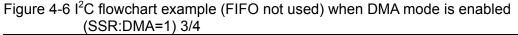

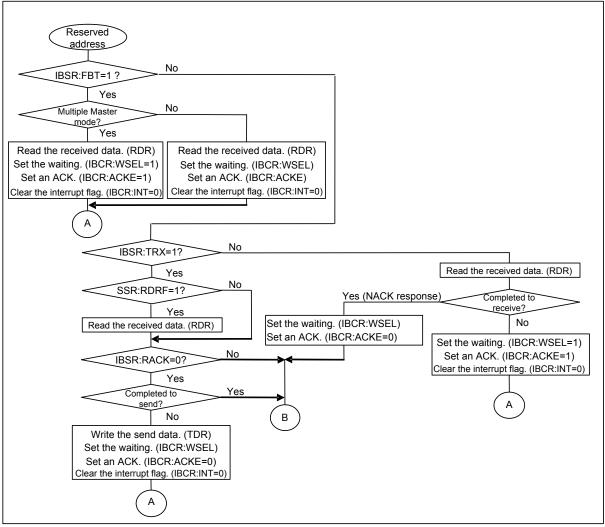

| 4. I <sup>2</sup> C communication operation flowchart examples                                    |     |

| 5. I <sup>2</sup> C Interface Registers                                                           |     |

| 5.1. I <sup>2</sup> C Bus Control Register (IBCR)                                                 |     |

| 5.2. Serial Mode Register (SMR)                                                                   |     |

| 5.3. I <sup>2</sup> C Bus Status Register (IBSR)                                                  |     |

| 5.4. Serial Status Register (SSR)<br>5.5. Received Data Register/Transmit Data Register (RDR/TDR) |     |

| 5.6. Noise Filter Control Register (NFCR)                                                         |     |

| 5.7. Extension I <sup>2</sup> C Bus Control Register (EIBCR)                                      |     |

| 5.8. 7-bit Slave Address Mask Register (ISMK)                                                     |     |

| 5.9. 7-bit Slave Address Register (ISBA)                                                          |     |

| 5.10. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)                                       |     |

| 5.11. FIFO Control Register 1 (FCR1)                                                              |     |

| 5.12. FIFO Control Register 0 (FCR0)                                                              |     |

| 5.13. FIFO Byte Register (FBYTE)                                                                  |     |

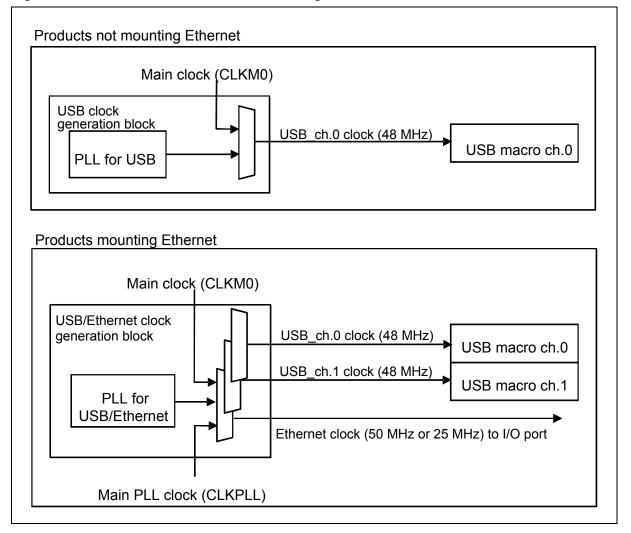

| CHAPTER 2-1: USB/Ethernet Clock Generation Block                                                  |     |

| 1. Overview and Configuration                                                                     |     |

|                                                                                                   |     |

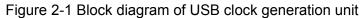

| CHAPTER 2-2: USB Clock Generation                                                                 |     |

| 1. Overview                                                                                       |     |

| 2. Configuration and Block Diagram                                                                |     |

| 3. Explanation of Operation                                                                       | 320 |

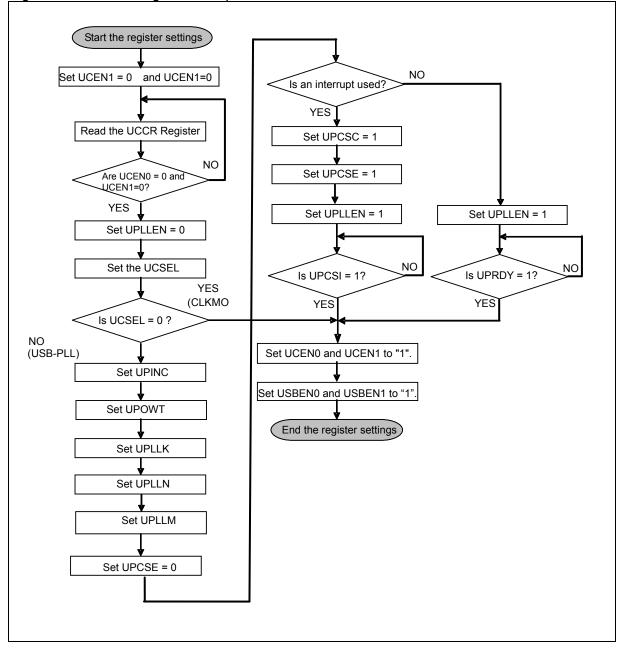

| 4. Setup Procedure Example                                                                        |     |

| 5. Register List                                                                                  |     |

| 5.1. USB Clock Control Register (UCCR)                                                            |     |

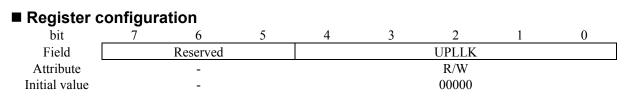

| 5.2. USB-PLL Control Register1 (UPCR1)                                                            |     |

| 5.3. USB-PLL Control Register 2 (UPCR2)                                                           |     |

| 5.4. USB-PLL Control Register 3 (UPCR3)                                                           |     |

| 5.5. USB-PLL Control Register 4 (UPCR4)                                                           |     |

| 5.6. USB-PLL Control Register 5 (UPCR5)                                                           |     |

| 5.7. USB-PLL Status Register (UP_STR)                                                             |     |

| 5.8. USB-PLL Interrupt Factor Enable Register (UPINT_ENR)                                         |     |

| 5.9. USB-PLL Interrupt Factor Status Register (UPINT_STR)                                         |     |

| 5.10. USB-PLL Interrupt Factor Clear Register (UPINT_CLR)                                         |     |

| 5.11. USB(ch.0) Enable Register (USBEN0)                                                          |     |

| 5.12. USB (ch.1) Enable Register (USBEN1)                                                         |     |

| 6. Usage Precautions                                                                              |     |

| CHAPTER 2-3: USB/Ethernet Clock Generation                                                        |     |

| 1. Overview                                                                                       |     |

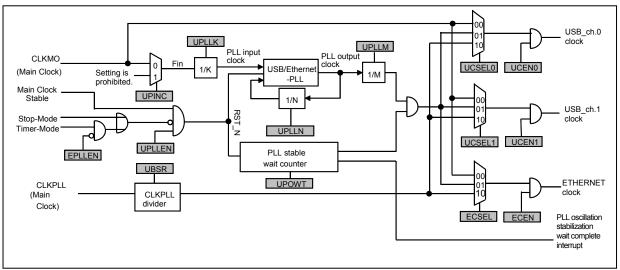

| 2. Configuration and Block Diagram                                                                |     |

| 3. Description of operation                                                                       |     |

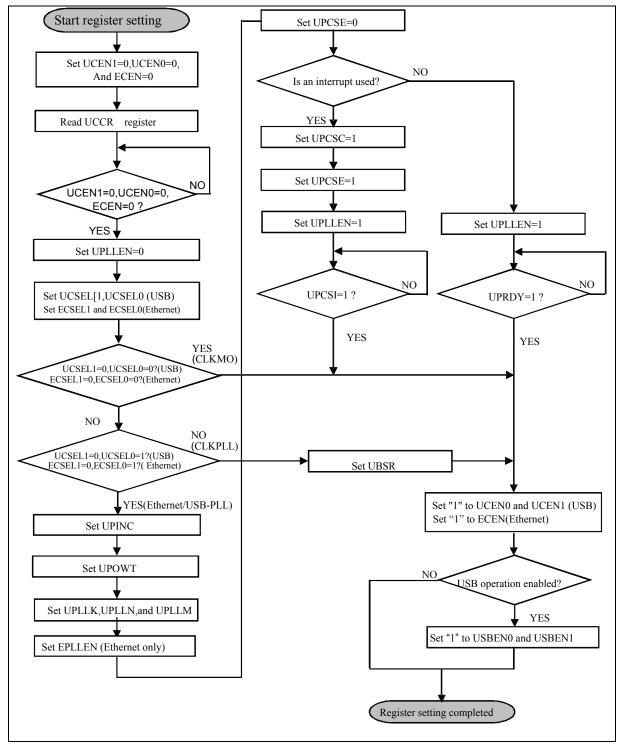

| 4. Example of setting procedure                                                                   | 040 |

|                                                                                                   |     |

| 5. List of Registers                                                                              |     |

| 5.2. USB/Ethernet-PLL Control Register1 (UPCR1)                                                                                          |     |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3. USB/Ethernet-PLL Control Register2 (UPCR2)                                                                                          |     |

| 5.4. USB/Ethernet-PLL Control Register3 (UPCR3)                                                                                          |     |

| 5.5. USB/Ethernet-PLL Control Register4 (UPCR4)                                                                                          |     |

| 5.6. USB/Ethernet-PLL Control Register5 (UPCR5)                                                                                          |     |

| 5.7. USB/Ethernet-PLL Control Register6 (UPCR6)                                                                                          |     |

| 5.8. USB/Ethernet-PLL Control Register7 (UPCR7)                                                                                          |     |

| 5.9. USB/Ethernet-PLL State Register (UP_STR)                                                                                            |     |

| 5.10. USB/Ethernet-PLL Interrupt Factor Enable Register (UPINT_ENR)                                                                      |     |

| 5.11. USB/Ethernet-PLL Interrupt Factor State Register (UPINT_STR)<br>5.12. USB/Ethernet-PLL Interrupt Factor Clear Register (UPINT_CLR) |     |

| 5.13. USB (ch.0) Enable Register (USBEN0)                                                                                                |     |

| 5.14. USB (ch.1) Enable Register (USBEN0)                                                                                                |     |

| 6. Usage Precautions                                                                                                                     |     |

| C C C C C C C C C C C C C C C C C C C                                                                                                    |     |

| CHAPTER 3-1: USB Function                                                                                                                | 361 |

| 1. Overview of USB Function                                                                                                              |     |

| 1.1. Features of USB function                                                                                                            | 362 |

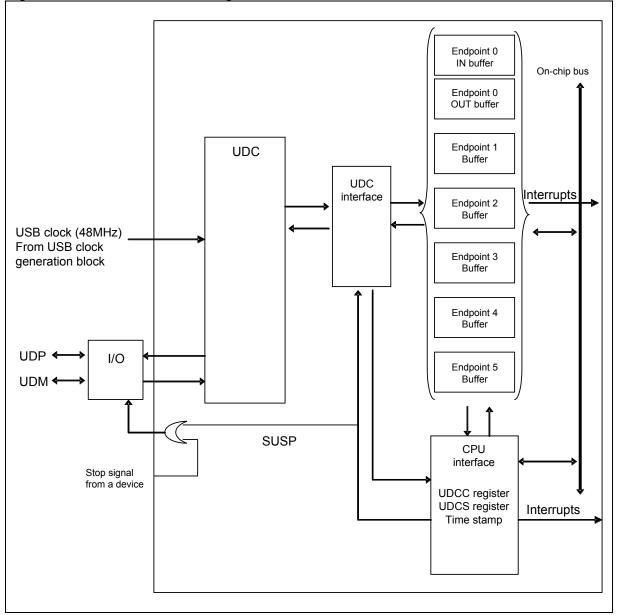

| 2. Configuration of USB Function                                                                                                         | 363 |

| 3. Operations of USB Function                                                                                                            | 365 |

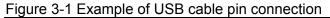

| 3.1. USB function operation                                                                                                              | 366 |

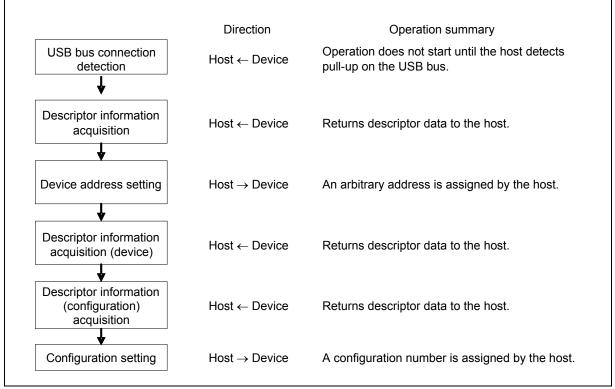

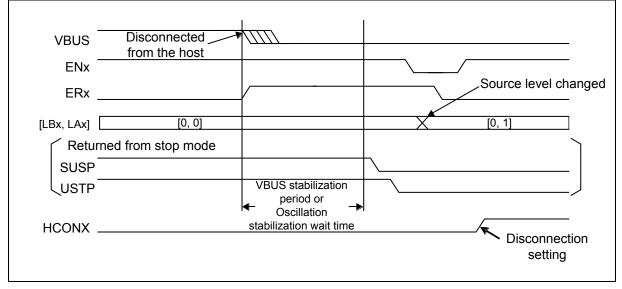

| 3.2. Detection of connection and disconnection                                                                                           | 369 |

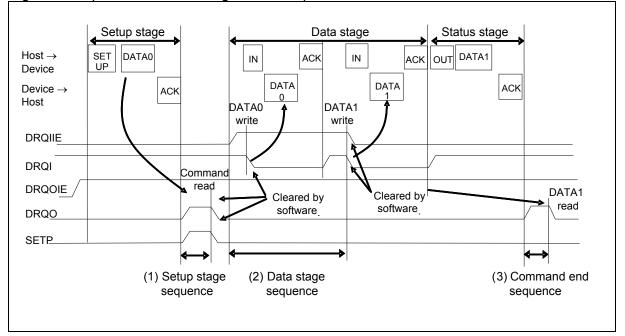

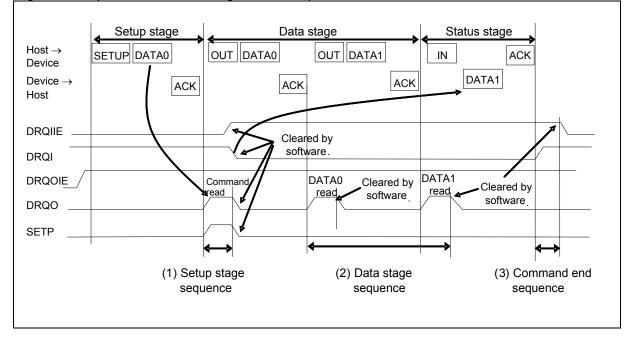

| 3.3. Operation of each register in response to a command                                                                                 | 372 |

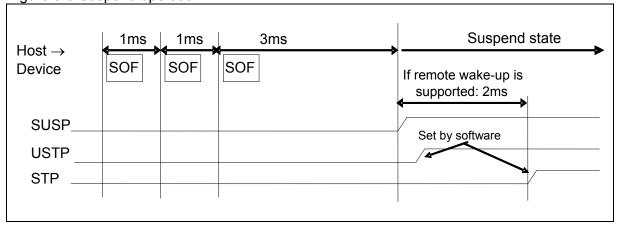

| 3.4. Suspend function                                                                                                                    | 374 |

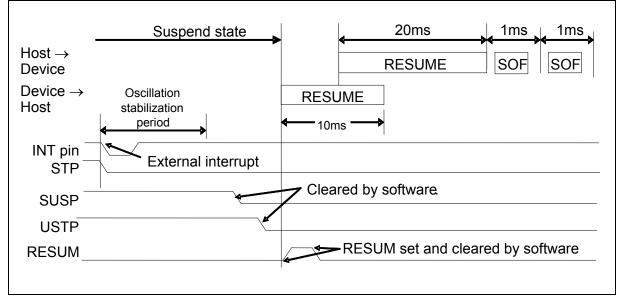

| 3.5. Wake-up function                                                                                                                    | 375 |

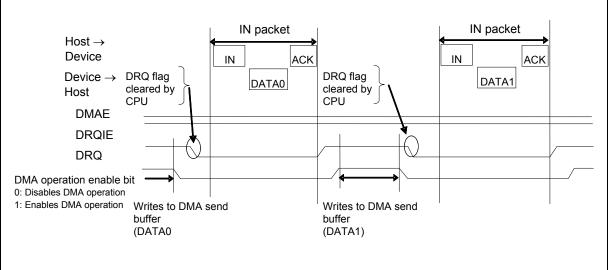

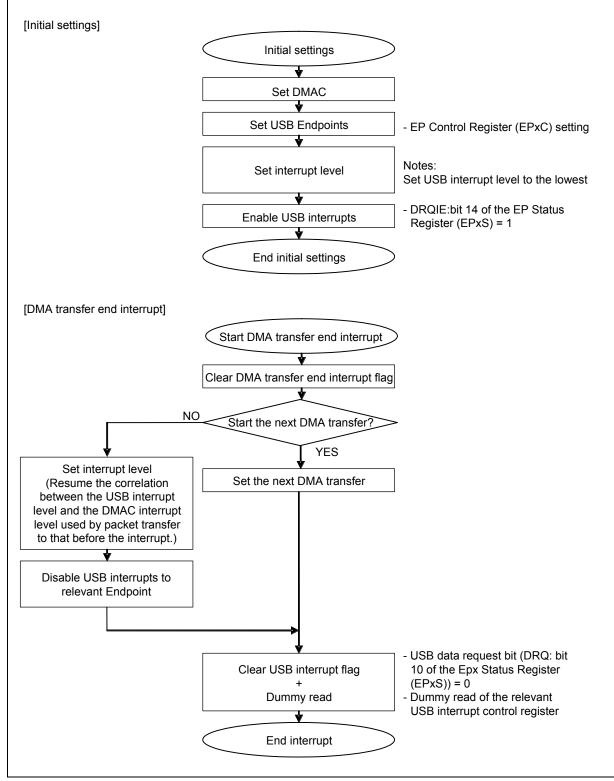

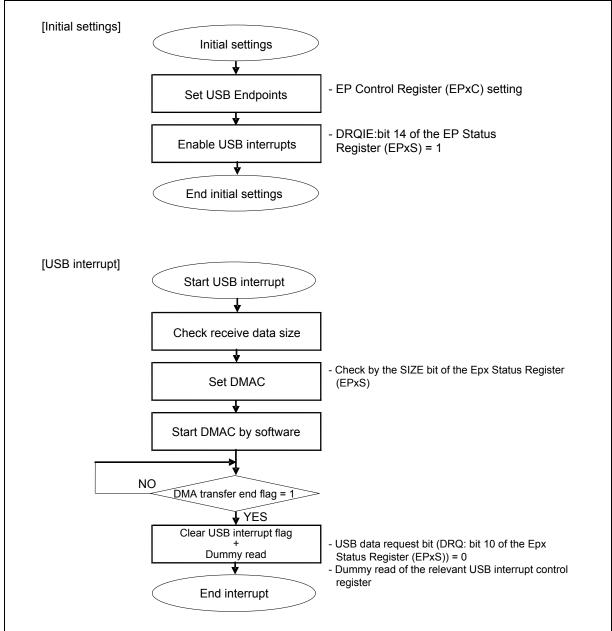

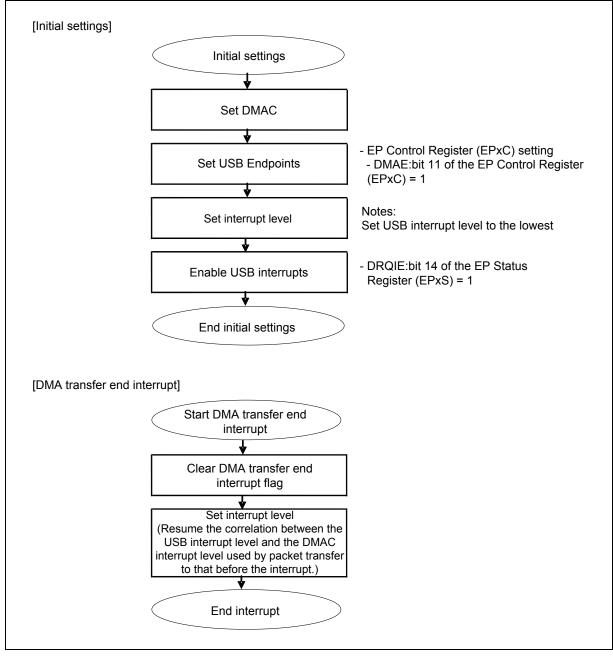

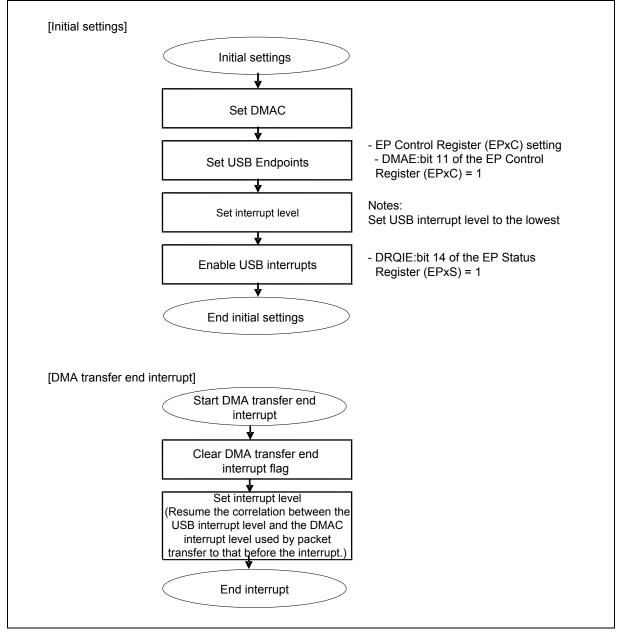

| 3.6. DMA transfer function                                                                                                               | 377 |

| 3.7. NULL transfer function                                                                                                              | 381 |

| 3.8. STALL response/release of Endpoint 0                                                                                                |     |

| 3.9. STALL response/release of Endpoint 1 to Endpoint 5                                                                                  | 384 |

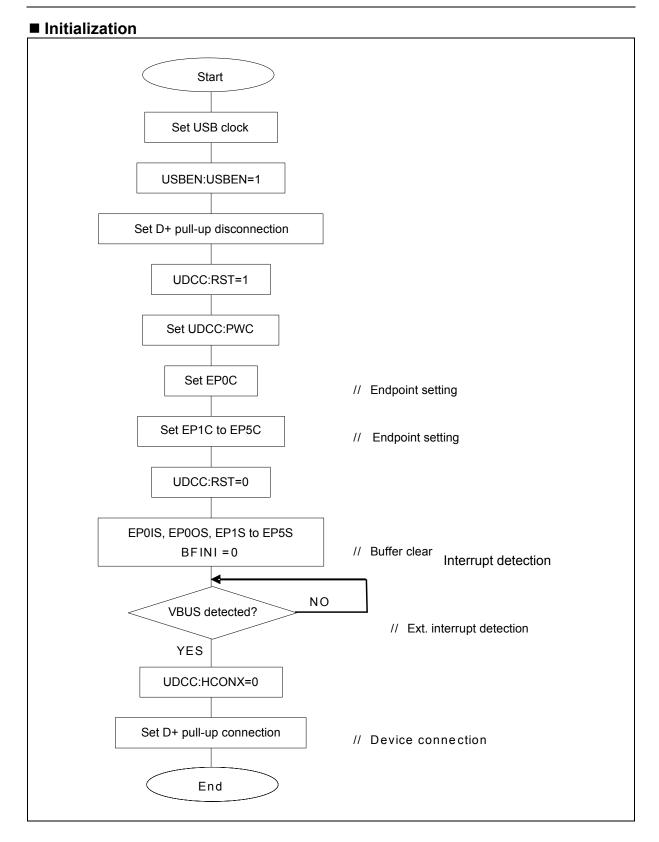

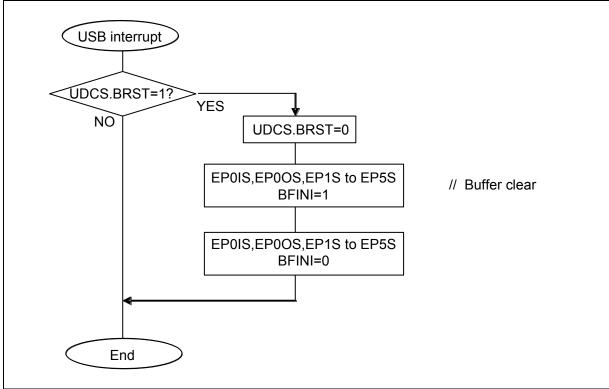

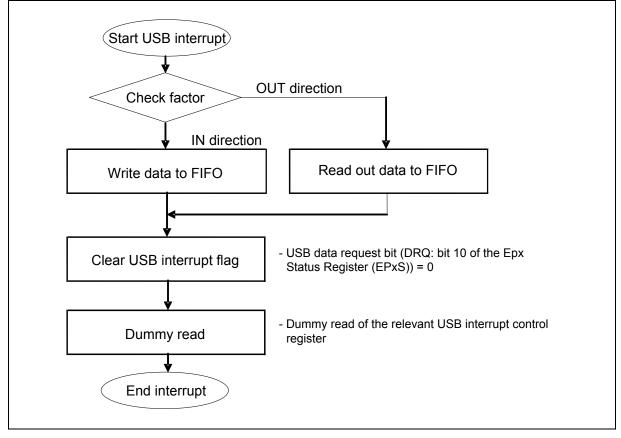

| 4. Examples of USB Function Setting Procedures                                                                                           | 388 |

| 5. USB Function Registers                                                                                                                | 395 |

| 5.1. UDC Control Register (UDCC)                                                                                                         | 397 |

| 5.2. EP0 Control Register (EP0C)                                                                                                         |     |

| 5.3. EP1 to EP5 Control Registers (EP1C to EP5C)                                                                                         | 402 |

| 5.4. Time Stamp Register (TMSP)                                                                                                          | 406 |

| 5.5. UDC Status Register (UDCS)                                                                                                          | 407 |

| 5.6. UDC Interrupt Enable Register (UDCIE)                                                                                               | 410 |

| 5.7. EP0I Status Register (EP0IS)                                                                                                        |     |

| 5.8. EP0O Status Register (EP0OS)                                                                                                        |     |

| 5.9. EP1 to EP5 Status Registers (EP1S to EP5S)                                                                                          |     |

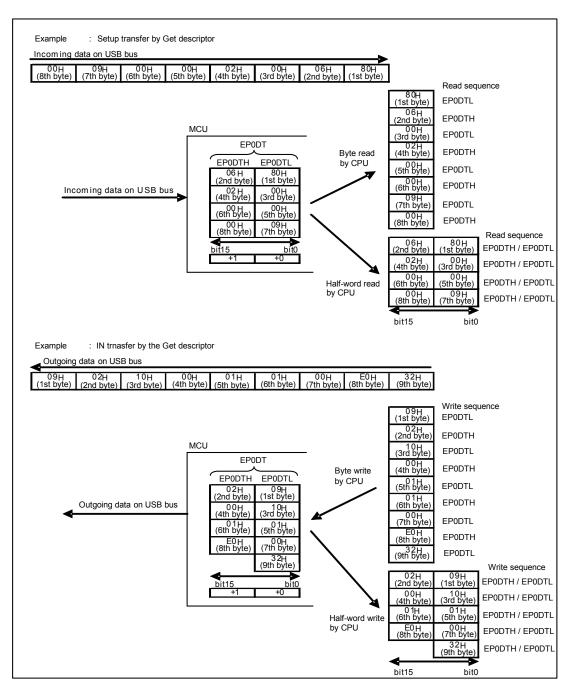

| 5.10. EP0 to EP5 Data Registers (EP0DTH to EP5DTH/EP0DTL to EP5DTL)                                                                      | 420 |

| CHAPTER 3-2: USB Host                                                                                                                    | 423 |

| 1. Overview of USB host                                                                                                                  | 424 |

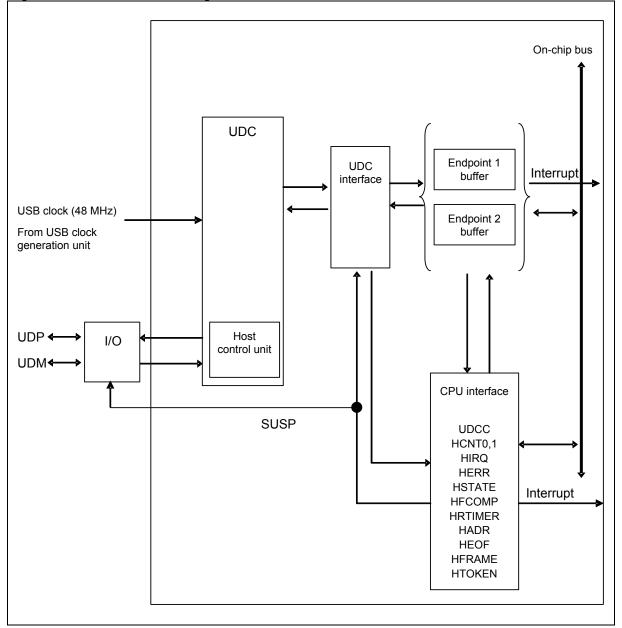

| 2. USB host configuration                                                                                                                | 426 |

| 3. USB host operations                                                                                                                   | 427 |

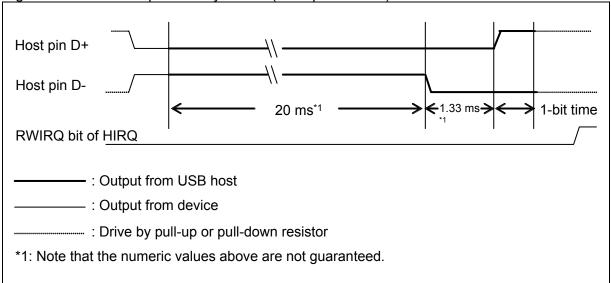

| 3.1. Device connection                                                                                                                   |     |

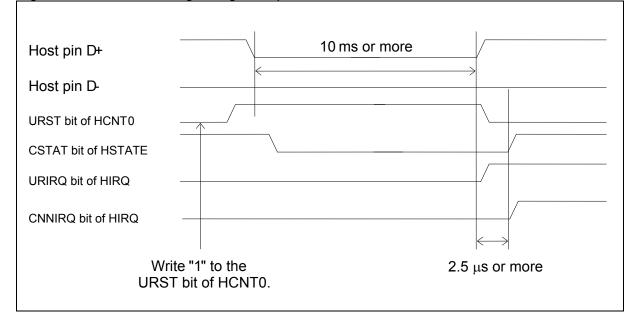

| 3.2. USB bus resetting                                                                                                                   | 430 |

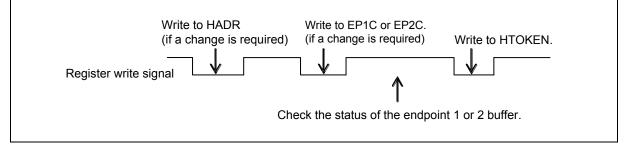

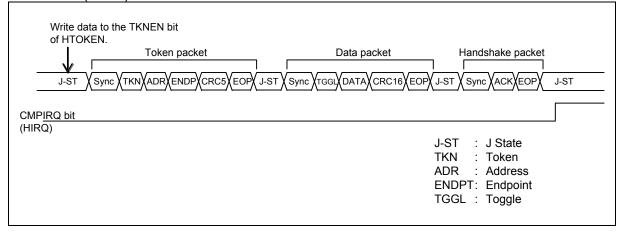

| 3.3. Token packet                                                                                                                        |     |

| 3.4. Data packet                                                                                                                         | 433 |

|                                                                                                                                          |     |

| 3.5. Handshake packet                                 | 434 |

|-------------------------------------------------------|-----|

| 3.6. Retry function                                   |     |

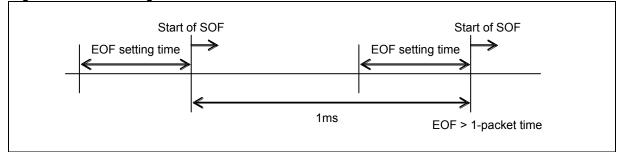

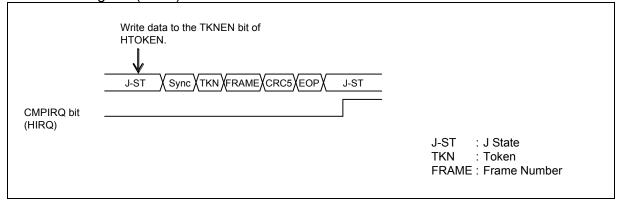

| 3.7. SOF interrupt                                    |     |

| 3.8. Error status                                     | 438 |

| 3.9. End of packet                                    | 439 |

| 3.10. Suspend and resume operations                   | 440 |

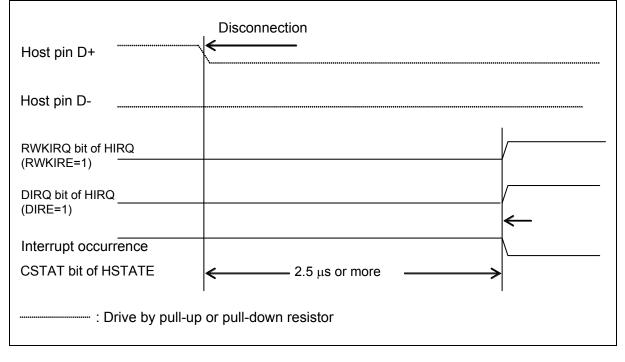

| 3.11. Device disconnection                            | 443 |

| 4. USB host setting procedure examples                | 444 |

| 5. USB host registers                                 |     |

| 5.1. Host Control Registers 0 and 1 (HCNT0 and HCNT1) |     |

| 5.2. Host Interrupt Register (HIRQ)                   |     |

| 5.3. Host Error Status Register (HERR)                |     |

| 5.4. Host Status Register (HSTATE)                    |     |

| 5.5. SOF Interrupt Frame Compare Register (HFCOMP)    |     |

| 5.6. Retry Timer Setup Register (HRTIMER)             |     |

| 5.7. Host Address Register (HADR)                     |     |

| 5.8. EOF Setup Register (HEOF)                        |     |

| 5.9. Frame Setup Register (HFRAME)                    |     |

| 5.10. Host Token Endpoint Register (HTOKEN)           |     |

|                                                       |     |

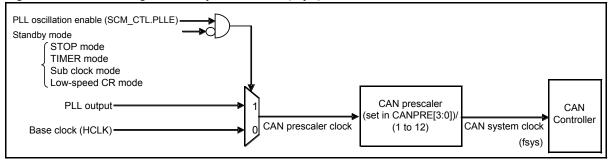

| CHAPTER 4-1: CAN Prescaler                            | 473 |

| 1. Overview and configuration                         | 474 |

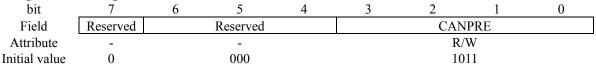

| 2. CAN Prescaler Register                             | 475 |

| 2.1. CAN Prescaler Register (CANPRE)                  | 476 |

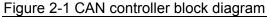

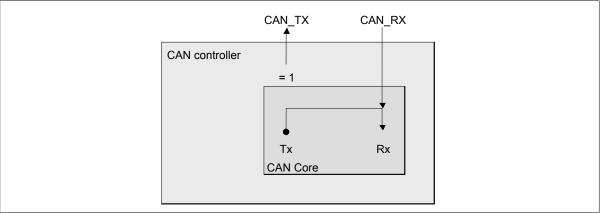

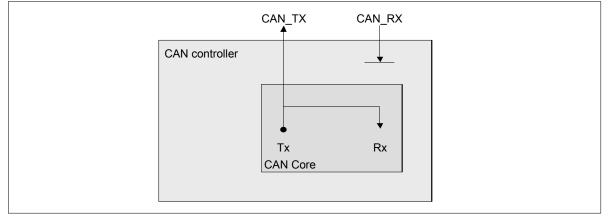

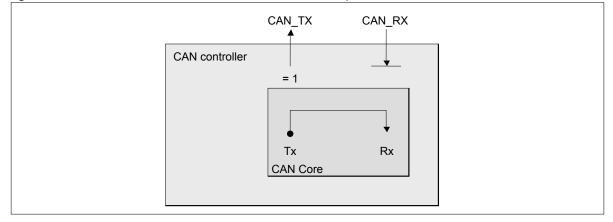

| CHAPTER 4-2: CAN Controller                           | 477 |

| 1. Overview                                           |     |

|                                                       |     |

| 2. Configuration                                      |     |

| 3. CAN Controller Operations                          |     |

| 3.1. Message objects                                  |     |

| 3.2. Message transmission                             |     |

| 3.3. Message reception                                |     |

| 3.4. FIFO buffer function                             |     |

| 3.5. Interrupt function                               |     |

| 3.6. Bit timing                                       |     |

| 3.7. Test mode                                        |     |

| 3.8. Software initialization                          | 498 |

| 4. CAN Registers                                      | 499 |

| 4.1. CAN register functions                           | 502 |

| 4.2. Total control registers                          | 503 |

| 4.2.1. CAN Control Register (CTRLR)                   | 504 |

| 4.2.2. CAN Status Register (STATR)                    |     |

| 4.2.3. CAN Error Counter (ERRCNT)                     | 511 |

| 4.2.4. CAN Bit Timing Register (BTR)                  | 512 |

| 4.2.5. CAN Interrupt Register (INTR)                  |     |

| 4.2.6. CAN Test Register (TESTR)                      |     |

| 4.2.7. CAN Prescaler Extension Register (BRPER)       |     |

| 4.3. Message interface registers                      |     |

| 4.3.1. IFx Command Request Register (IFxCREQ)         |     |

| 4.3.2. IFx Command Mask Register (IFxCMSK)            | 520 |

| 4.3.3. IFx Mask Registers 1, 2 (IFxMSK1, IFxMSK2)              |     |

|----------------------------------------------------------------|-----|

| 4.3.4. IFx Arbitration Registers 1, 2 (IFxARB1, IFxARB2)       |     |

| 4.3.5. IFx Message Control Register (IFxMCTR)                  |     |

| 4.3.6. IFx Data Registers A1, A2, B1, and B2                   |     |

| (IFxDTA1, IFxDTA2, IFxDTB1, and IFxDTB2)                       | 528 |

| 4.4. Message objects                                           |     |

| 4.5. Message handler registers                                 |     |

| 4.5.1. CAN Transmit Request Registers 1, 2 (TREQR1, TREQR2)    | 536 |

| 4.5.2. CAN New Data Registers 1, 2 (NEWDT1, NEWDT2)            | 538 |

| 4.5.3. CAN Interrupt Pending Registers 1, 2 (INTPND1, INTPND2) | 540 |

| 4.5.4. CAN Message Valid Registers 1, 2 (MSGVAL1, MSGVAL2)     | 542 |

| 5. Notes                                                       |     |

| APPENDIXES                                                     |     |

| A. Register Map                                                |     |

| 1. Register Map                                                |     |

| B List of Notes                                                | 600 |

| 1. Notes when high-speed CR is used for the master clock       |     |

|                                                                |     |

## **MAJOR CHANGES IN THIS EDITION**

| Page | Section | Change Results |

|------|---------|----------------|

| -    | -       | First edition  |

## **CHAPTER: Multi-function Serial Interface**

This chapter describes the overview of the multi-function serial interface.

1. Overview of the Multi-function Serial Interface

CODE: 9BFMFS FM4-E01.0

### 1. Overview of the Multi-function Serial Interface

This multi-function serial interface has the following characteristics.

#### ■ Interface Mode

The following interface modes are selectable for the multi-function serial interface depending on the operation mode settings.

- UART0 (Asynchronous normal serial interface)

- · UART1 (Asynchronous multi-processor serial interface)

- · CSIO (Clock synchronous serial interface) (SPI can be supported)

- · LIN(LIN bus interface)

- $I^2C$  ( $I^2C$  bus interface)

#### <Note>

See Chapters "UART(Asynchronous normal serial interface)", "CSIO (Clock synchronous serial interface) (SPI can be supported)", "LIN(LIN bus interface)" and "I<sup>2</sup>C (I<sup>2</sup>C bus interface)" for details about each interface.

#### Switching the Interface Mode

To communicate through each serial interface, the serial mode register (SMR) shown in Table 1-1 should be used to set the operation mode before starting the communication.

| MD2                         | MD1 | MD0      | Interface mode                                                       |  |  |  |

|-----------------------------|-----|----------|----------------------------------------------------------------------|--|--|--|

| 0                           | 0   | 0        | UART0 (Asynchronous normal serial interface)                         |  |  |  |

| 0                           | 0   | 1        | UART1 (Asynchronous multi-processor serial interface)                |  |  |  |

| 0                           | 1   | 0        | CSIO (Clock synchronization serial interface) (SPI can be supported) |  |  |  |

| 0                           | 1   | 1        | LIN(LIN bus interface)                                               |  |  |  |

| 1                           | 0   | 0        | I <sup>2</sup> C (I <sup>2</sup> C bus interface)                    |  |  |  |

| Values other than the above |     | he above | Setting is prohibited.                                               |  |  |  |

#### Table 1-1 Switching Interface Mode

#### <Notes>

- Transmission and reception cannot be guaranteed when the operation mode is switched while one of the serial interfaces is still in use for transmission or reception operation.

- To switch the current operation mode, issue a programmable clear (SCR:UPCL=1) or disable the I<sup>2</sup>C (ISMK:EN=0), and switch the operation mode continuously. After the operation mode is set, set each register.

- The settings not listed in Table 1-1 are prohibited.

#### Transmission/Reception FIFO

This function has a 64-BYTE transmission FIFO and 64-BYTE reception FIFO. The FIFO capacity should be converted to 64 bytes when reading through this text.

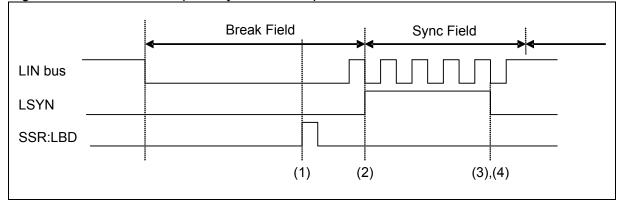

#### LIN Sync field Detection: LSYN

To use an ICU in the LIN bus interface mode, use the ICU of the multifunction timer. For switching an input to an ICU, see the section for Extended Function Pin Setting Register in the chapter "I/O PORT" in "PERIPHERAL MANUAL".

## CHAPTER: UART (Asynchronous Serial Interface)

This chapter explains the UART (asynchronous serial interface) function supported in operation mode 0 and 1 of the multifunction serial interface.

- 1. Overview of UART (Asynchronous Serial Interface)

- 2. UART Interrupt

- 3. UART Operation

- 4. Dedicated Baud Rate Generator

- 5. Setting Procedure and Program Flow in Operation Mode 0 (Asynchronous Normal Mode)

- 6. Setting Procedure and Program Flow in Operation Mode 1 (Asynchronous Multiprocessor Mode)

- 7. UART (Asynchronous Serial Interface) Registers

CODE: 9BFUART\_FM4-E01.0\_FM15U-J05.4

## 1. Overview of UART (Asynchronous Serial Interface)

UART (asynchronous serial interface) is a general-purpose serial data communications interface for asynchronous communications (start/stop synchronization) with external devices. It supports a bi-directional communications function (normal mode) and a master/slave type communications function (multi-processor mode: both master and slave modes supported). It also has transmit /received FIFO installed.

#### Functions of UART (Asynchronous Serial Interface)

| $\setminus$ |                          | Function                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1           | Data                     | <ul> <li>Full duplex double buffer (when FIFO is not used)</li> <li>Transmit /received FIFO (size: max 128 bytes each)<sup>*1</sup> (when FIFO is used)</li> </ul>                                                                                                                                                                                                          |  |  |  |

| 2           | Serial input             | Run oversampling three times with the bus clock and determine the value of received data based on the majority sampling value.                                                                                                                                                                                                                                              |  |  |  |

| 3           | Transfer system          | Asynchronous                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4           | Baud rate                | <ul> <li>A dedicated baud rate generator (constructed with a 15-bit reload counter)</li> <li>The external clock input can be adjusted with the reload counter.</li> </ul>                                                                                                                                                                                                   |  |  |  |

| 5           | Data length              | • 5 to 9 bits (in normal mode)/7 bits or 8 bits (in multiprocessor mode)                                                                                                                                                                                                                                                                                                    |  |  |  |

| 6           | Signaling system         | NRZ (Non Return to Zero), inverted NRZ                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 7           | Start bit detection      | <ul> <li>In synch with the falling edge of the start bit (in the NRZ system)</li> <li>In synch with the rising edge of the start bit (in the inverted NRZ system)</li> </ul>                                                                                                                                                                                                |  |  |  |

| 8           | Received error detection | <ul> <li>Framing error</li> <li>Overrun error</li> <li>Parity error<sup>*2</sup></li> </ul>                                                                                                                                                                                                                                                                                 |  |  |  |

| 9           | Hardware flow control    | CTS/RTS-based automatic transmit /received control                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 10          | Interrupt request        | <ul> <li>Received interrupt         <ul> <li>(upon reception completed, framing error, overrun error or parity error*<sup>2</sup>)</li> <li>Transmit interrupts (transmit data empty, transmit bus idle)</li> <li>Transmit FIFO interrupt (when transmit FIFO is empty)</li> <li>DMA(Transmit /Received) transferring support function is available.</li> </ul> </li> </ul> |  |  |  |

| Tinctions   |                          | One (master)-to-n (slaves) communication is enabled.<br>(Both master and slave systems are supported.)                                                                                                                                                                                                                                                                      |  |  |  |

| 12          | FIFO options             | <ul> <li>Transmit /received FIFO installed (maximum capacity: 128 bytes for transmit FIFO, 128 bytes for received FIFO)<sup>*1</sup></li> <li>Transmit FIFO or received FIFO can be selected.</li> <li>Transmit data can be resent.</li> <li>Received FIFO interrupt timing can be changed via software.</li> <li>FIFO resetting is supported independently.</li> </ul>     |  |  |  |

\*1: The FIFO capacity size varies depending on the product type.

\*2: Parity errors are only generated in normal mode.

## 2. UART Interrupt

UART generates transmit or received interrupts. These interrupt requests can be generated if:

- Received data is set in the Received Data Register (RDR) or a data received error occurs.

Transmit data is transferred from the Transmit Data Register (TDR) to the transmit shift register and the data transmission is started.

- The transmit bus is idle (No data transmission occurs).

- Transmit FIFO data is requested.

#### ■ UART Interrupt

Table 2-1 shows the relationships between the UART interrupt control bits and the interrupt factors.

| Interrupt<br>type | Interrupt<br>request<br>flag | Flag<br>register | Operation<br>mode |   | Interrupt factor                                                                                                                                  | Interrupt<br>factor | Operation to clear interrupt request flag                                                                                                                                                                                                                         |

|-------------------|------------------------------|------------------|-------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | bit                          | register         | 0                 | 1 |                                                                                                                                                   | enable bit          | interrupt request hay                                                                                                                                                                                                                                             |

|                   |                              |                  |                   | 0 | A single-byte received                                                                                                                            | SCR:RIE             | Reading from the received data register (RDR)                                                                                                                                                                                                                     |

|                   |                              |                  | 0                 |   | Received of a data<br>volume matching the<br>value set for FBYTE.                                                                                 |                     | Reading from the Received Data<br>Register (RDR) until received FIFO<br>is emptied                                                                                                                                                                                |

| Received          | RDRF                         | SSR              |                   |   | While the FRIIE bit is<br>"1" and the received<br>FIFO contains valid<br>data, a received idle<br>state continues for 8<br>bits or longer period. |                     |                                                                                                                                                                                                                                                                   |

|                   | ORE                          | SSR              | 0                 | 0 | Overrun error                                                                                                                                     |                     | Setting the received error flag clear<br>bit (SSR:REC) to "1"                                                                                                                                                                                                     |

|                   | FRE                          | SSR              | 0                 | 0 | Framing error                                                                                                                                     |                     |                                                                                                                                                                                                                                                                   |

|                   | PE                           | SSR              | 0                 | х | Parity error                                                                                                                                      |                     |                                                                                                                                                                                                                                                                   |

| Transmit          | TDRE                         | SSR              | 0                 | 0 | The Transmit Data<br>Register is empty                                                                                                            | SCR:TIE             | Writing to the Transmit Data<br>Register (TDR) or setting the<br>transmit FIFO operation enable bit<br>to "1" when the transmit FIFO<br>operation enable bit is set to "0" and<br>valid data are present in transmit<br>FIFO (re-transmitting data) <sup>*1</sup> |

|                   | TBI                          | SSR              | 0                 | 0 | No data transmission                                                                                                                              | SCR:TBIE            | Writing to the Transmit Data<br>Register (TDR) or setting the<br>transmit FIFO operation enable bit<br>to "1" when the transmit FIFO<br>operation enable bit is set to "0" and<br>valid data are present in transmit<br>FIFO (re-transmitting data) <sup>*1</sup> |

|                   | FDRQ                         | FCR1             | 0                 | 0 | Transmit FIFO is empty.                                                                                                                           | FCR1:FTIE           | The FIFO transmit data request bit<br>(FCR1:FDRQ) is set to "0" or<br>transmit FIFO is full.                                                                                                                                                                      |

Table 2-1 UART interrupt control bits and interrupt factors

\*1: Set the TIE bit to "1" only after the TDRE bit has been set to "0".

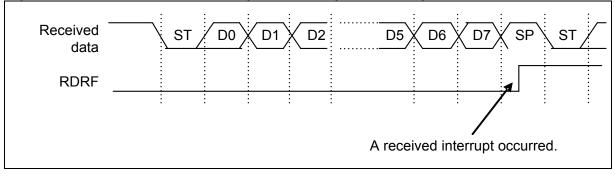

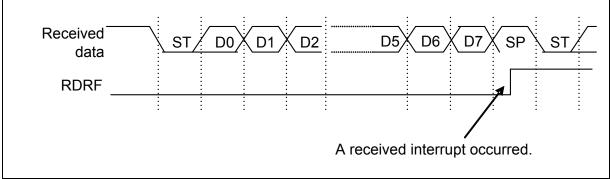

## 2.1. Received interrupt and flag set timing

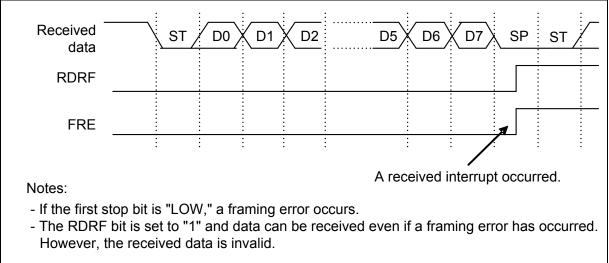

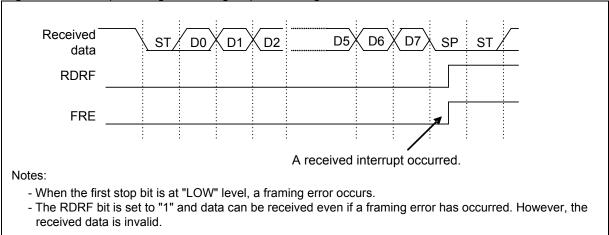

Data reception can be interrupted by a Received Completion (SSR:RDRF=1) or a Received Error Occurrence (SSR:PE,ORE,FRE=1).

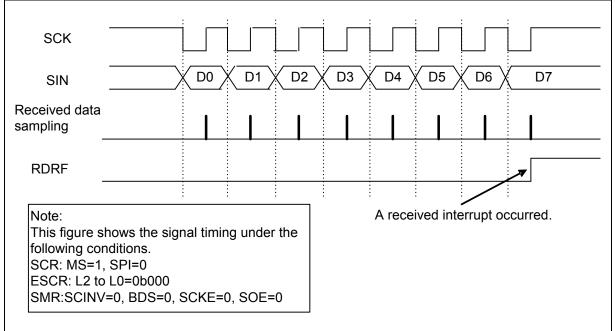

#### Received interrupt and flag set timing

Upon detection of the first stop bit, received data are stored in the Received Data Register (RDR). When the data received is completed (SSR:RDRF=1) or when a data received error occurs (SSR:PE, ORE, FRE=1), each flag is set. If received interrupts are enabled (SSR:RIE=1) then, a received interrupt occurs.

#### <Note>

If a received error occurs, data in the Received Data Register (RDR) becomes invalid.

#### Figure 2-1 RDRF (Received Data Register Full) flag bit set timing

#### Figure 2-2 FRE (Framing Error) flag bit set timing

#### <Note>

During reception, if the following is detected at the same time as the stop bit sampling point or before the 1 to 2 bus clocks, the relevant edge becomes invalid, which may disable normal received of the next data. To output frames continuously, adequate intervals are required between frames.

- The falling edge of serial data (When ESCR:INV=0)

- The rising edge of serial data (When ESCR:INV=1)

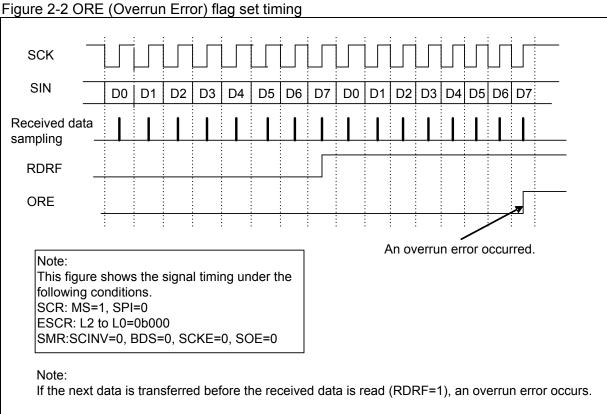

| Figure 2-3 ORE (Overrun Error) flag bit set timing |                                                                                        |  |  |  |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| Received<br>data                                   | ST/D0/D1/D2/D3/D4/D5/D6/D7/SP\ST/D0/D1/D2/D3/D4/D5/D6/D7/SP                            |  |  |  |  |

| RDRF                                               |                                                                                        |  |  |  |  |

| ORE                                                |                                                                                        |  |  |  |  |

| Note:<br>If the next d                             | ata is transferred before the received data is read (RDRF=1), an overrun error occurs. |  |  |  |  |

## 2.2. Interrupt and flag set timing when received FIFO is used

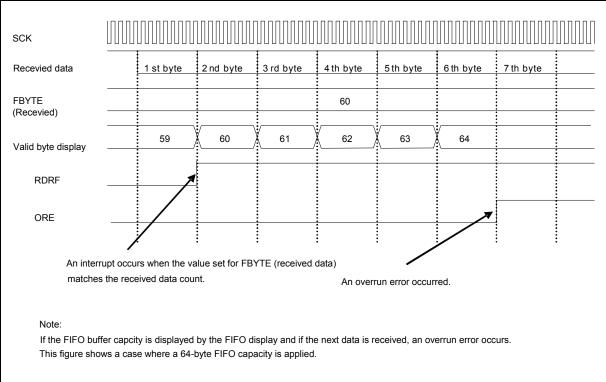

If the received FIFO is used, an interrupt occurs when the FBYTE data (preset for the FBYTE register) is received.

#### ■ Interrupt and flag set timing when received FIFO is used

If the received FIFO is used, an interrupt occurs depending on the value set for the FBYTE register.

- When full FBYTE data is received, the received data full flag (SSR:RDRF) of the Serial Status register is set to "1". If received interrupts are enabled (SCR:RIE) during this time, a received interrupt occurs.

- If the following two conditions are satisfied and if the received idle state continues for more than 8 baud rate clocks, the receive data full flag (SSR:RDRF) is set to "1".

- The received FIFO idle detection enable bit (FCR:FRIIE) is "1".

- The number of data sets stored in the received FIFO does not reach the transfer count. If the RDR data is read during counting of 8 clocks, this counter is reset to "0", and counting for 8 clocks is restarted. If received FIFO is disabled, this counter is reset to zero (0). If data remains in the received FIFO and if received FIFO is enabled, the data counting is restarted.

- When data is read from the Received Data Register (RDR) until received FIFO is emptied, the received data full flag (SSR:RDRF) is cleared.

- If the valid received data amount is the same as the FIFO capacity and if the next data is received, an overrun error (SSR:ORE=1) occurs.

| Received data                                        | ST 1st byte SP ST 2nd byte SP ST 3rd byte SP ST 4th byte SP ST 5th byte SP                           |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| FBYTE setting 〔 (with the transfer count)            | 3                                                                                                    |

| Reading of FBYTE -<br>(Effective byte count display) |                                                                                                      |

| RDRF                                                 | <b>A</b>                                                                                             |

| Data reading from RDR                                | ,лл                                                                                                  |

|                                                      | ppt occurs when the FBYTE (transmit data) All received data are read. tches the received data count. |

#### Figure 2-4 Received interrupt timing when Received FIFO is used

## Figure 2-5 ORE (Overrun Error) flag bit set timing

| Received data                                   | ST 62nd byteSP                              | ST 63rd byteSP | ST64th byteSF   | ST 65th byte SP    | ST 66th byte SP |

|-------------------------------------------------|---------------------------------------------|----------------|-----------------|--------------------|-----------------|

| FBYTE setting (with the transfer count)         |                                             |                | 62              |                    |                 |

| Reading of FBYTE (Effective byte count display) | X                                           | 62             | 63 X            | 64                 |                 |

| RDRF                                            |                                             |                |                 |                    |                 |

| ORE                                             |                                             |                |                 |                    |                 |

|                                                 |                                             | ·              | An c            | overrun error occu | rred.           |

| Note:                                           |                                             |                |                 |                    |                 |

|                                                 | xt data set is received<br>un error occurs. | when the FB    | TE reading is   | indicating the FIF | O capacity,     |

| This figu                                       | ire shows a case where                      | e a 64-byte F  | IFO capacity is | applied.           |                 |

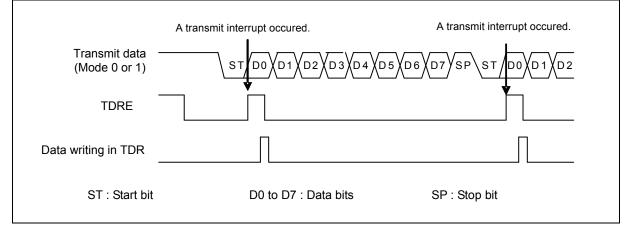

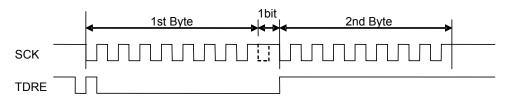

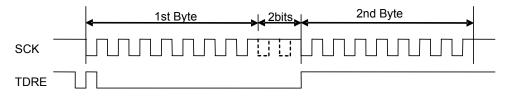

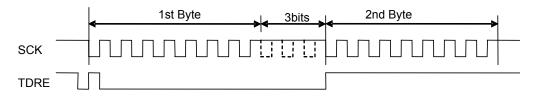

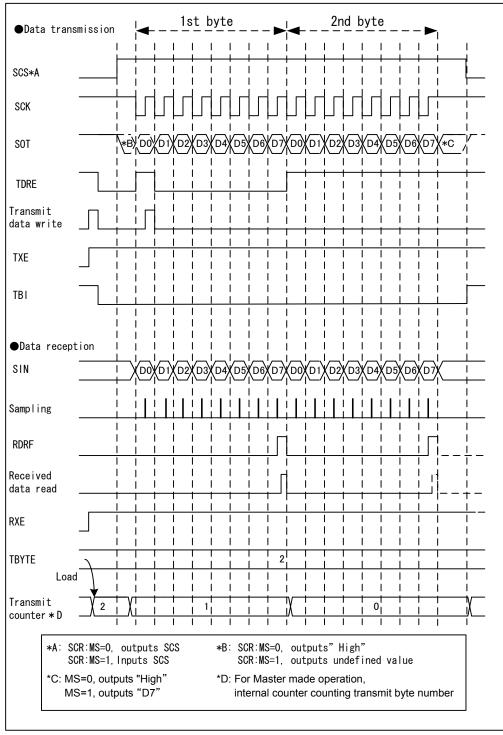

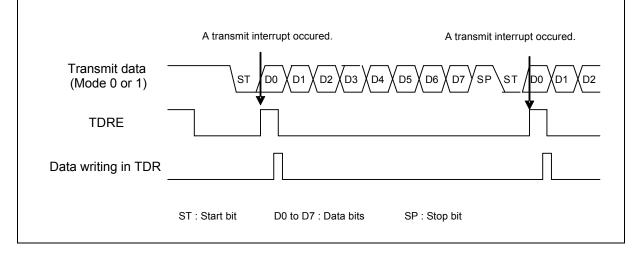

## 2.3. Transmit interrupt and flag set timing

A transmit interrupt occurs when transmit data is transferred from the Transmit Data Register (TDR) to the transmit shift register (SSR:TDRE = 1) and transmission starts and when no transmission is performed (SSR:TBI = 1).

#### Transmit interrupt and flag set timing

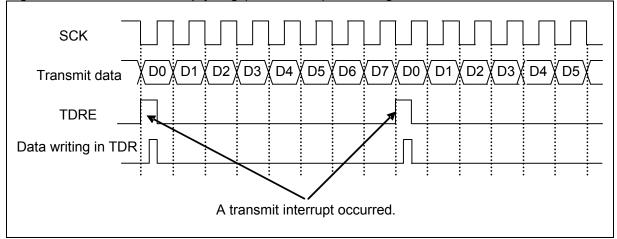

#### • Transmit data empty flag (SSR:TDRE) set timing

After data has been transferred from the Transmit Data Register (TDR) to the transmit shift register, the next data can be written in the TDR (SSR:TDRE = 1). If transmit interrupts are enabled (SCR:TIE = 1) during this time, a transmit interrupt occurs. As the SSR:TDRE bit is read only, the SSR:TDRE bit is cleared to "0" when data is written to the Transmit Data Register (TDR).

#### Figure 2-6 Transmit data empty flag (SSR:TDRE) set timing

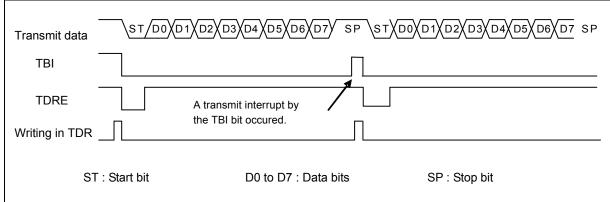

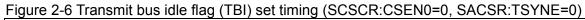

#### Transmit bus idle flag (SSR:TBI) set timing

If the Transmit Data Register is empty (SSR:TDRE=1) and no data is transmitted, the SSR:TBI bit is set to "1". If transmit bus idle interrupts are enabled (SCR:TBIE = 1) during this time, a transmit interrupt occurs. When transmit data is written to the Transmit Data Register (TDR), both the SSR:TBI bit and the transmit interrupt request are cleared.

Figure 2-7 Transmit bus idle flag (TBI) set timing

## 2.4. Interrupt and flag set timing when transmit FIFO is used

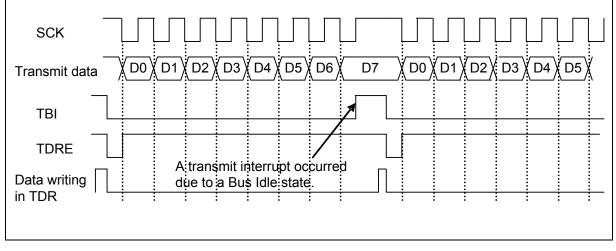

When the transmit FIFO is used, an interrupt occurs if the FIFO contains no data.

#### Transmit interrupt and flag set timing when transmit FIFO is used

- If the Transmit FIFO contains no data, the FIFO transmit data request bit (FCR1:FDRQ) is set to "1". If FIFO transmit interrupts are enabled (FCR1:FTIE=1), a transmit interrupt occurs.

- If a transmit interrupt has occurred and you have written the required data in transmit FIFO, clear the interrupt request by setting the FIFO transmit data request bit (FCR1:FDRQ) to "0".

- · The FIFO transmit data request bit (FCR1:FDRQ) is set to "0" when transmit FIFO becomes full.

- To check to see if transmit FIFO contains any data, read from the FIFO Byte Register (FBYTE). If FBYTE=0x00, no data exists in the transmit FIFO.

#### Figure 2-8 Transmit interrupt timing when transmit FIFO is used

| Transmit data ST 1st byte SP ST 2nd byte SP ST 3rd byte ST SP 4th byte SP SP 5th byte                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBYTE    0    1    2    1 $\sqrt{0}\sqrt{1}\sqrt{2}$ 1 $\sqrt{0}$                                                                                                                                      |

| FDRQ                                                                                                                                                                                                   |

| TDRE Cleared if A transmit interrupt Cleared if A transmit interrupt set to "0". occurred.*1 occurred.*1                                                                                               |

| Data writing in transmit FIFO (TDR)                                                                                                                                                                    |

| <ul> <li>*1) The FDRQ bit is set to "1" as Transmit FIFO is empty.</li> <li>*2) The TDRE bit is set to "1" as the Transmit Shift Register and the Transmit Buffer Register contain no data.</li> </ul> |

## 3. UART Operation

UART operates in bi-directional serial asynchronous communications in mode 0 and master/slave multiprocessor communications in mode 1.

#### UART operation

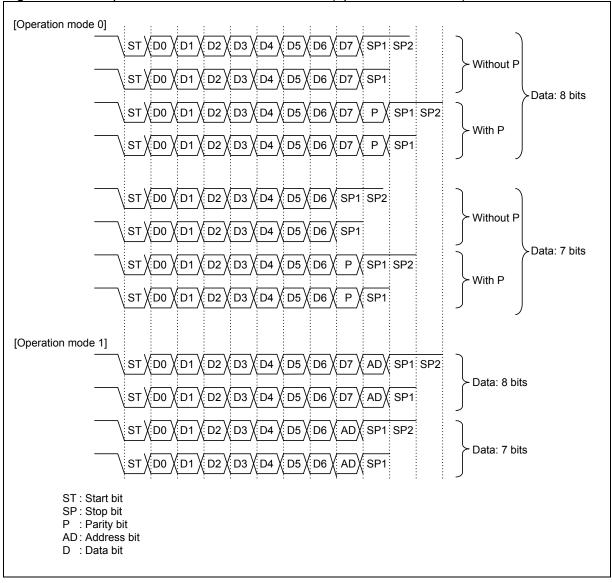

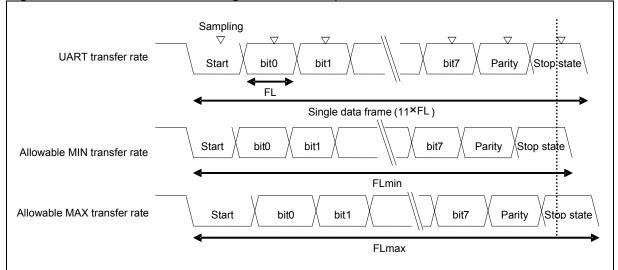

#### • Transmit/received data format

- Transmit/received data always starts with a start bit, followed by transmit/received of data with the specified data bit length, and ends with at least one-bit long stop bit.

- The BDS bit of the Serial Mode Register (SMR) determines the data transmission direction (LSB first or MSB first). If parity is used, the parity bit is always placed between the last data bit and the first stop bit.

- In operation mode 0 (normal mode), selection is possible to use or not to use parity.

- · In operation mode 1 (multiprocessor mode), no parity is added, and instead, the AD bit is added.

Figure 3-1 shows the transmit/received data formats for operation mode 0 and 1.

#### <Notes>

- The above figure shows formats when the data length is set to 7 or 8 bits. (In operation mode 0, the data length can be set between 5 and 9 bits.)

- If the BDS bit of the Serial Mode Register (SMR) is set to "1" (MSB first), the bits are processed from D7, and then D6, D5, ... D1, and D0 (P), in that order.

- If the data length is set to X bits, the lower X bit of the Transmit/Received Data Register (TDR/RDR) is enabled.

#### Data transmission

- If the transmit data empty flag bit (TDRE) of the Serial Status Register (SSR) is "1", the transmit data can be written in the Transmit Data Register (TDR). (When transmit FIFO is enabled, transmit data can be written even if TDRE=0.)

- If transmit data is written in the Transmit Data Register (TDR), the transmit data empty flag bit (SSR:TDRE) is set to "0".

- Setting the transmission enable bit of the serial control register (SCR:TXE) to "1" causes transmit data to be loaded to the transmit shift register, followed by sequential transmission starting with the start bit.

- When transmission starts, the transmit data empty flag bit (SSR:TDRE) is set to "1" again. If transmit interrupts are then enabled (SCR:TIE=1), a transmit interrupt is generated. In the interrupt processing, the next transmit data set can be written in the Transmit Data Register,

#### <Notes>

- As the transmit data empty flag bit (SSR:TDRE) is initially set to "1", a transmit interrupt occurs as soon as transmit interrupts are enabled (SCR:TIE).

- As the FIFO transmit data request bit (FCR1:FDRQ) is initially set to "1", a transmit interrupt occurs as soon as FIFO transmit interrupts are enabled (FCR1:FTIE=1).

#### • Data reception

- When reception is enabled (SCR:RXE=1), the interface performs reception.

- Upon detection of the start bit, one-frame data reception takes place according to the data format set in the extended communications control register (ESCR:PEN, P, L2, L1, L0) and serial mode register (SMR:BDS). A start bit is detected when falling (ESCR:INV=0) is detected after passing the noise filter (with the majority value applied after sampling serial data input three times with the bus clock) or if rising (ESCR:INV=1) is detected and "LOW" is detected for the data passing the sampling point.

- When one-frame reception is completed, the received data full flag bit (SSR:RDRF) is set to "1". If received interrupts are then enabled (SCR:RIE=1), a received interrupt is generated.

- To read received data, perform reading of the received data after one-frame data received is completed and check the state of the error flag of the Serial Status Register (SSR). Handle the received error if it is occurring.

- · Reading of the received data causes the received data full flag bit (SSR:RDRF) to be cleared to "0".

- If received FIFO is enabled, the received data full flag bit (SSR:RDRF) is set to "1" when the number of received frames has reached the value set for received FBYTE.

- If the following two conditions are satisfied and if the received idle state continues for more than 8 baud rate clocks, the interrupt flag (RDRF) is set to "1".

- The received FIFO idle detection enable bit (FRIIE) is "1".

- The number of data sets stored in the received FIFO does not reach the transfer count. If the RDR data is read during counting of 8 clocks, this counter is reset to "0", and counting for 8 clocks is restarted. If received FIFO is disabled, this counter is reset to zero (0). If data remains in the received FIFO and if received FIFO is enabled, the data counting is restarted.

- If received FIFO is enabled, received FIFO does not store data in which an error has occurred when the error flag of the Serial Status Register (SSR) is set to "1". Also note that the received data full flag bit (SSR:RDRF) is not set to "1". (However, the RDRF flag is set to "1" in an overrun error.) What the received FBYTE indicates is the number of data sets received normally before the error occurred. Unless the error flag of the Serial Status Register (SSR) is cleared to "0", received FIFO is not enabled.

- If received FIFO is enabled, the received data full flag bit (SSR:RDRF) is cleared to "0" when all data in received FIFO is out.

#### <Notes>

- Data in the Received Data Register (RDR) becomes valid when the received data register full flag bit (SSR:RDRF) is set to "1" and no received error occurs (SSR:PE, ORE, FRE=0).

- Although a noise filter is built in (with the majority value applied after sampling serial data input three times with the bus clock), wrong data may be received if any noise passes through the filter. As a countermeasure, you can design the board so as not to allow noise to pass through this filter or perform communications so that noise that has passed may not cause any problem (by adding check sum of data at the end and resending the data if any error occurs, for example).

- During reception, if the following is detected at the same time as the stop bit sampling point or before the 1 to 2 bus clocks, the relevant edge becomes invalid, which may disable normal reception of the next data. To output frames continuously, adequate intervals are required between frames.

- The falling edge of serial data (When ESCR:INV=0)

- The rising edge of serial data (When ESCR:INV=1)

#### Clock selection

- You can use either an internal or external clock.

- To use the external clock, set SMR:EXT to "1". IN this case, the external clock is subject to frequency division by the baud rate generator.

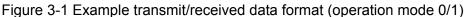

#### Start bit detection

- In asynchronous mode, the start bit is recognized based on detection of the falling edge of the SIN signal. For that reason, reception is not started unless the falling edge of the SIN signal is input even if reception is enabled (SCR:RXE=1).

- Upon detection of the start bit's falling edge, the received reload counter of the baud rate generator is reset and reloaded to start countdown. Thus, sampling always takes place in the middle of data.

#### • Stop bit

- You can select the bit length to be between one and four.

- The received data full flag bit (SSR:RDRF) is set to "1" upon detection of the first stop bit.

#### • Error detection

- In operation mode 0, parity, overrun and framing errors can be detected.

- · In operation mode 1, overrun and framing errors can be detected but parity errors cannot be detected.

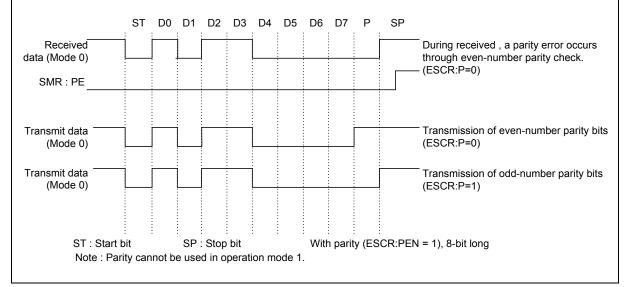

#### • Parity bit

- The parity bit can only be added in operation mode 0. The parity enable bit (ESCR:PEN) can be used to specify use or non-use of parity and the parity selection bit (ESCR:P) to set even-number parity or odd-number parity.

- Parity cannot be used in operation mode 1.

Figure 3-2 shows transmit/received data when parity is enabled.

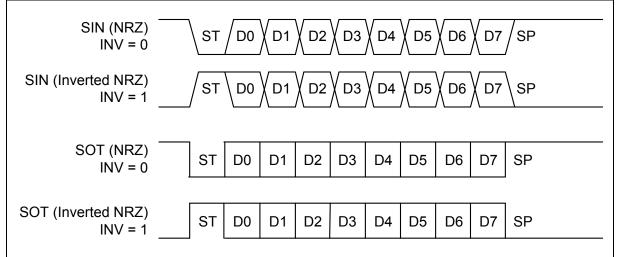

#### • Data signaling system

By setting up the INV bit of the extended communications control register, you can select either the NRZ (Non Return to Zero) signaling system (ESCR:INV=0) or inverted NRZ signaling system (ESCR:INV=1).

Figure 3-3 shows the NRZ and inverted NRZ signaling systems.

Figure 3-3 NRZ (Non Return to Zero) signaling system and inverted NRZ signaling system

#### • Data transfer system

As for the data bit transfer method, either LSB first or MSB first can be selected.

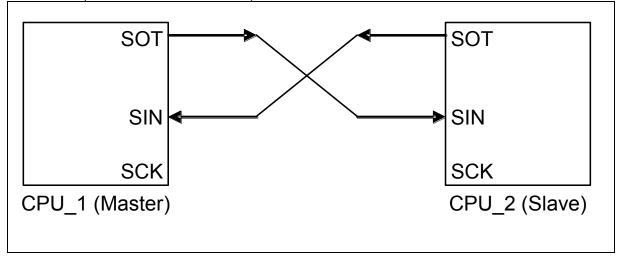

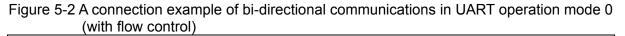

# • Hardware flow control

When flow control is enabled (ESCR:FLWEN=1), UART performs hardware flow control.

· During data transmission

If  $\overline{\text{CTS}}$  is "HIGH" after data is transmitted, the next data is not transmitted even if the transmit buffer contains data (TDRE=0) and the process waits until  $\overline{\text{CTS}}$  is set to "LOW". To have transmission wait, input "HIGH" in  $\overline{\text{CTS}}$  before the stop bit transmission is completed. Transmission continues up to the stop bit even if "HIGH" is input in  $\overline{\text{CTS}}$  during transmission.

#### Figure 3-4 Hardware flow control during data transmission (SMR'SBI =0 FSCR'FSBI =INV=PEN=I 2=I 1=I 0=0)

|                                                               | ,                                               |

|---------------------------------------------------------------|-------------------------------------------------|

| Transmit data ST ∠ D0 ∴ D1 ∴ D2 ∴ D3 ∴ D4 ∴ D5 ∴ D6 ∴ D7 ∠ SP | . ST → D0 → D1 → D2 → D3 → D4 → D5 → D6 → D7 SP |

| <i>CTS</i>                                                    |                                                 |

| Data writing in TDR                                           |                                                 |

|                                                               | Transmit in<br>wait state                       |

- · During data reception

- If FIFO is not used

Upon reception of data one bit before the stop bit, "HIGH" is output to RTS. After received data is read, "LOW" is output to  $\overline{\text{RTS}}$ .

Figure 3-5 Hardware flow control during data reception (with FIFO is unused.) (SMR:SBL=0, ESCR:ESBL=INV=PEN=L2=L1=L0=0)

| Received data    | ST D0 D1 D2 D3 D4 D5 D6 D7 SP | ST / D0 / D1 / D2 / D3 / D4 / D5 / D6 / D7 / SP |

|------------------|-------------------------------|-------------------------------------------------|

| RTS              |                               |                                                 |

| RDRF             |                               |                                                 |

| Reading from RDR |                               | Γ                                               |

|                  |                               |                                                 |

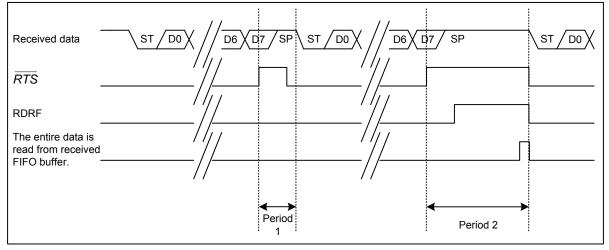

## · If FIFO is used

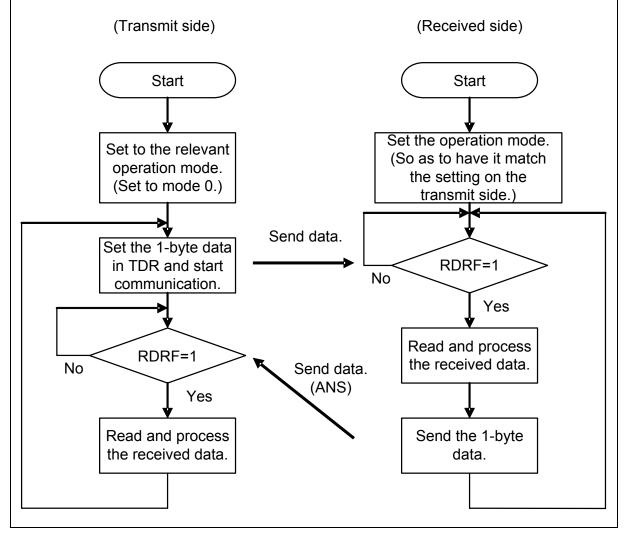

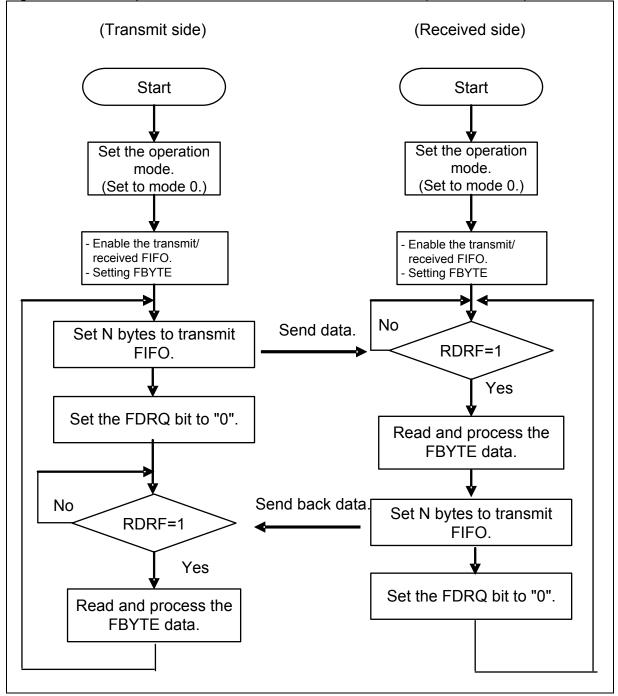

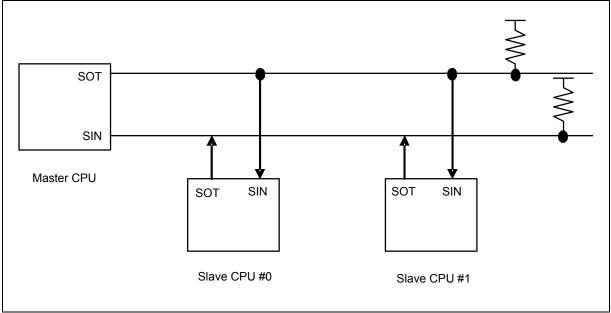

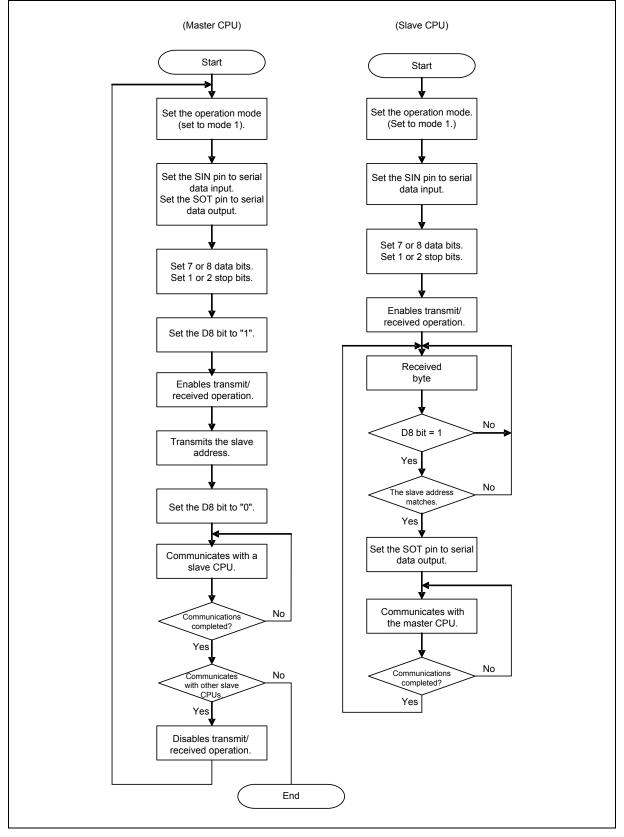

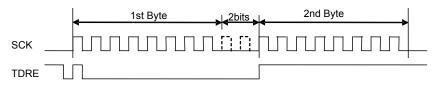

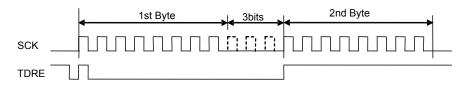

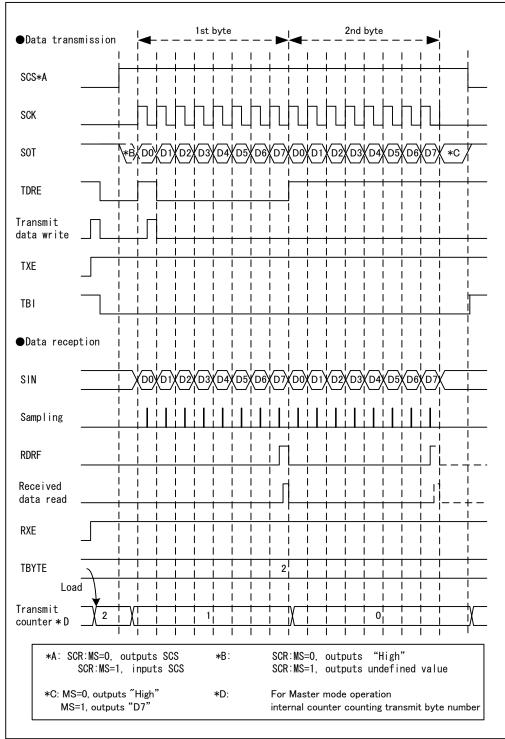

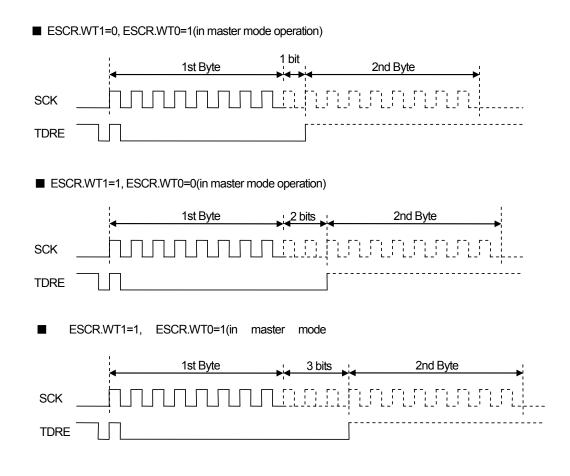

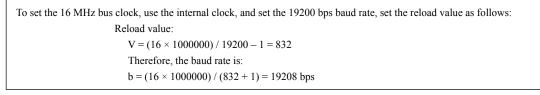

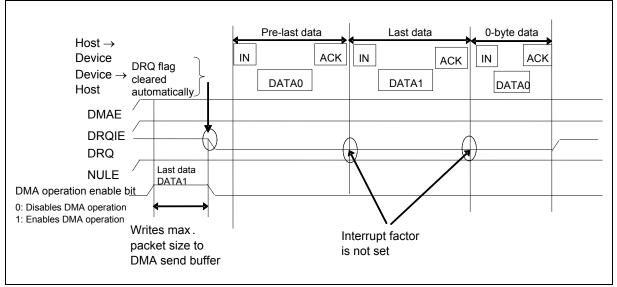

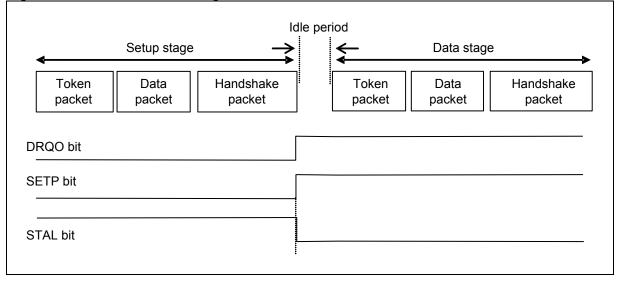

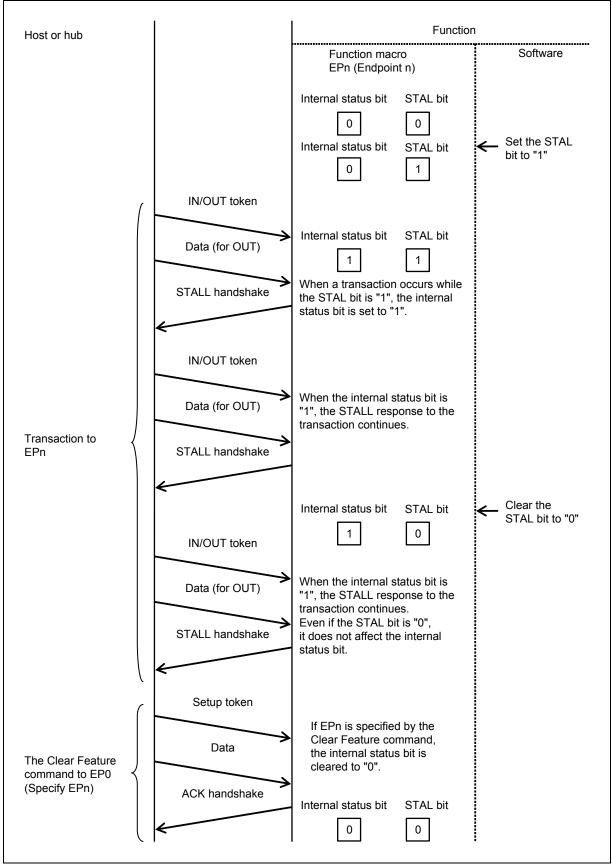

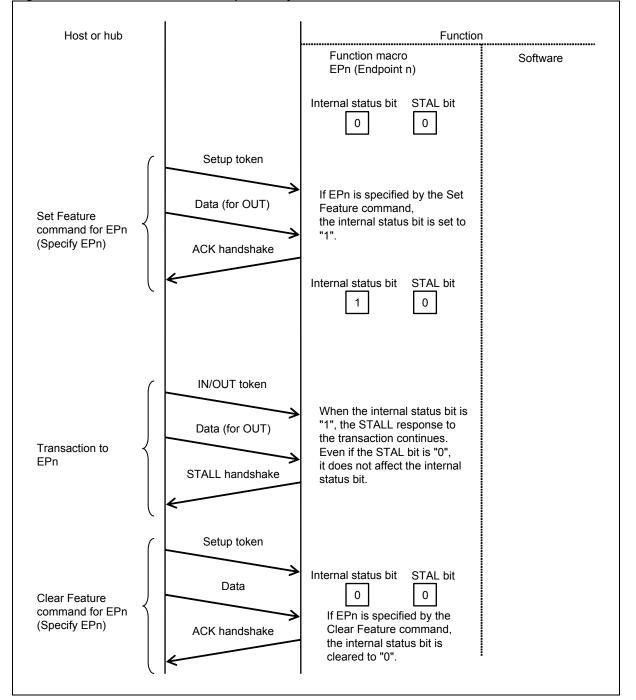

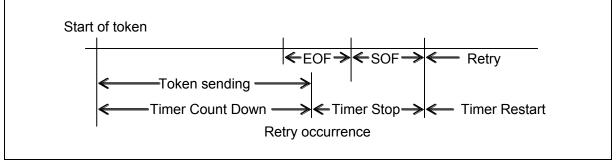

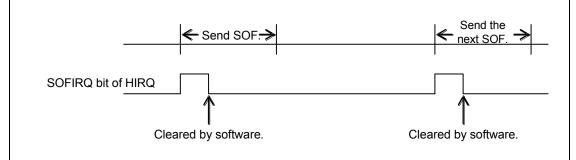

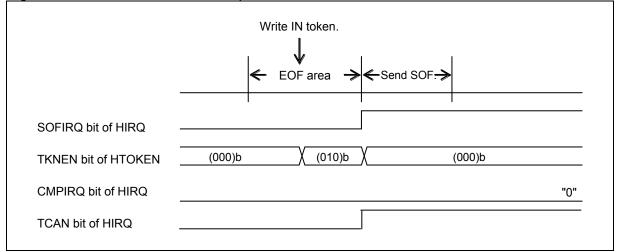

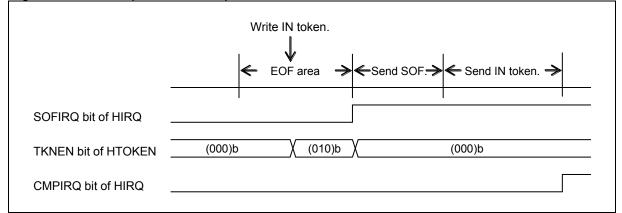

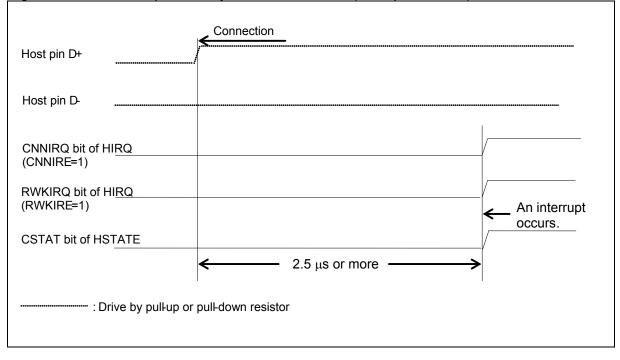

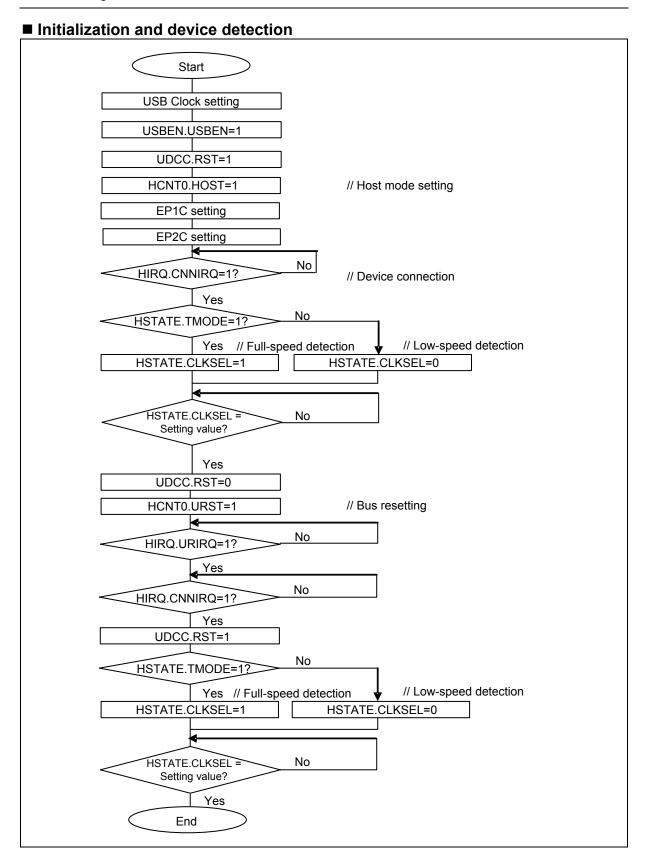

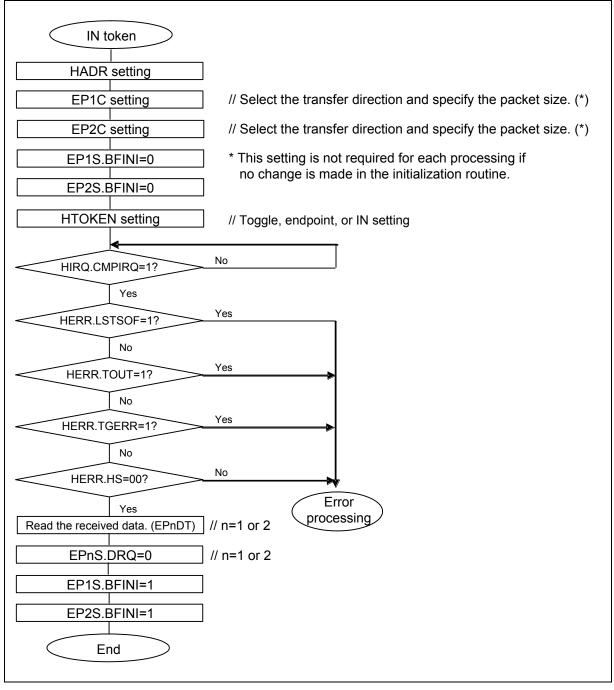

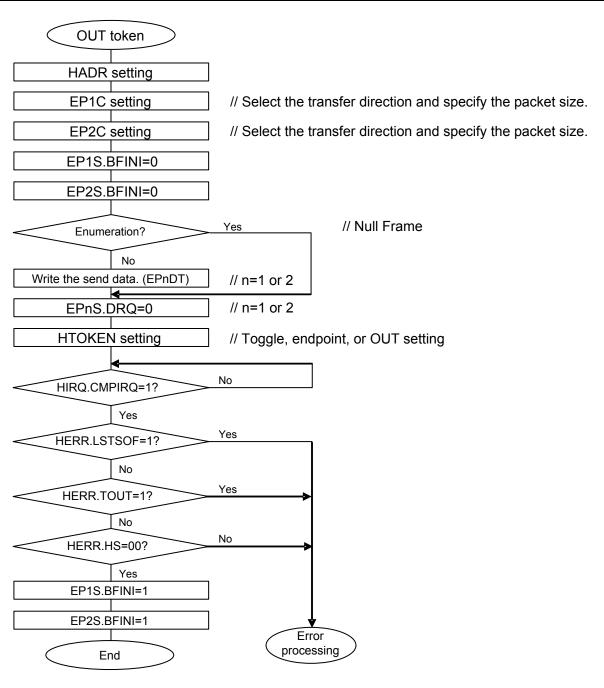

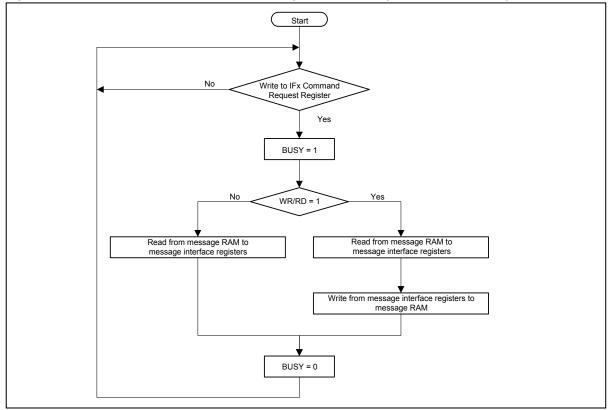

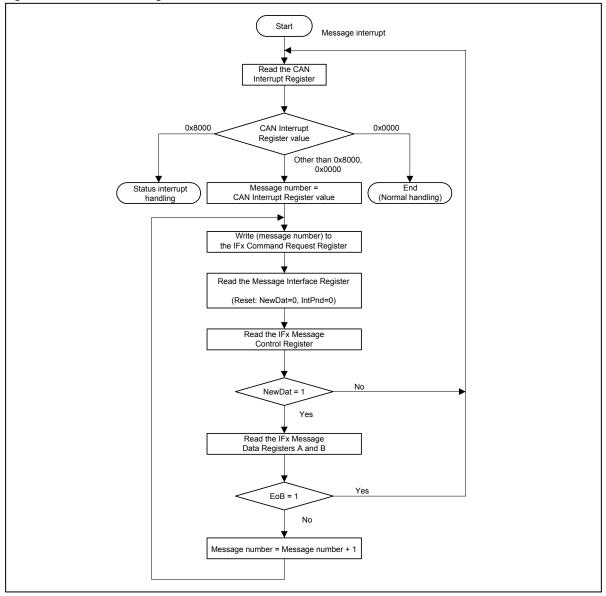

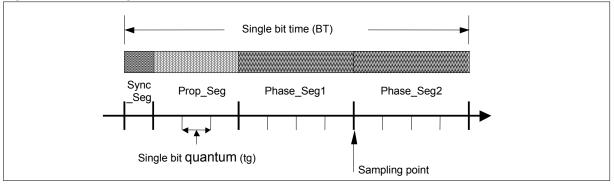

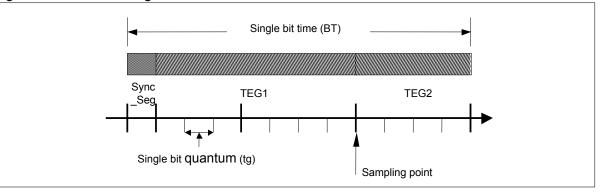

If SSR:RDRF is not set (the specified number of data sets are not received in received FIFO), RTS outputs "HIGH" upon reception of data one bit before the stop bit, but  $\overline{\text{RTS}}$  outputs "LOW" upon detection of the stop bit. (For period 1)