### 32-Bit Microcontroller FM3 Peripheral Manual Communication Macro Part

Doc. No. 002-04843 Rev. \*A

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

### How to Use This Manual

#### **Finding a Function**

The following methods can be used to search for the explanation of a desired function in this manual:

Search from the table of the contents

The table of the contents lists the manual contents in the order of description.

Search from the register

The address where each register is located is not described in the text. To verify the address of a register, see "A. Register Map" in "Appendixes".

#### About the Chapters

Basically, this manual explains Timer Part..

#### Terminology

This manual uses the following terminology.

| Term      | Explanation                           |

|-----------|---------------------------------------|

| Word      | Indicates access in units of 32 bits. |

| Half word | Indicates access in units of 16 bits. |

| Byte      | Indicates access in units of 8 bits.  |

#### Notations

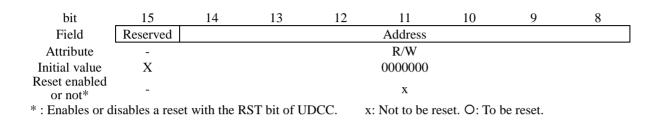

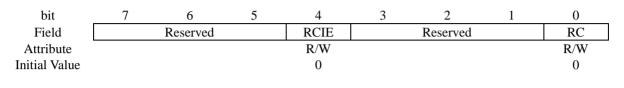

The notations in bit configuration of the register explanation of this manual are written as follows.

| bit:           | bit number                                |

|----------------|-------------------------------------------|

| Field:         | bit field name                            |

| Attribute:     | Attributes for read and write of each bit |

| R:             | Read only                                 |

| W:             | Write only                                |

| R/W:           | Readable/Writable                         |

| -:             | Undefined                                 |

| Initial value: | Initial value of the register after reset |

| 0:             | Initial value is 0                        |

| 1:             | Initial value is 1                        |

| X:             | Initial value is undefined                |

|                |                                           |

The multiple bits are written as follows in this manual. Example: bit7:0 indicates the bits from bit7 to bit0

The values such as for addresses are written as follows in this manual.

| Hexadecimal number: | "0x" is attached in the beginning of a value as a prefix (example: |

|---------------------|--------------------------------------------------------------------|

| 0xFFFF)             |                                                                    |

| Binary number:      | "0b" is attached in the beginning of a value as a prefix (example: |

| 0b1111)             |                                                                    |

| Decimal number:     | Written using numbers only (example: 1000)                         |

The target products in this manual In this manual, the products are classified into the following groups and are described as follows. For the descriptions such as "TYPEO", see the relevant items of the target product in the list below.

| Description in |            | Flash memory size |            |            |  |

|----------------|------------|-------------------|------------|------------|--|

| this manual    | 512 Kbytes | 384 Kbytes        | 256 Kbytes | 128 Kbytes |  |

|                | MB9BF506N  | MB9BF505N         | MB9BF504N  |            |  |

|                | MB9BF506R  | MB9BF505R         | MB9BF504R  |            |  |

|                | MB9BF506NA | MB9BF505NA        | MB9BF504NA |            |  |

|                | MB9BF506RA | MB9BF505RA        | MB9BF504RA | -          |  |

|                | MB9BF506NB | MB9BF505NB        | MB9BF504NB |            |  |

|                | MB9BF506RB | MB9BF505RB        | MB9BF504RB |            |  |

|                | MB9BF406N  | MB9BF405N         | MB9BF404N  |            |  |

|                | MB9BF406R  | MB9BF405R         | MB9BF404R  |            |  |

|                | MB9BF406NA | MB9BF405NA        | MB9BF404NA | -          |  |

|                | MB9BF406RA | MB9BF405RA        | MB9BF404RA |            |  |

|                | MB9BF306N  | MB9BF305N         | MB9BF304N  |            |  |

| TYPE0          | MB9BF306R  | MB9BF305R         | MB9BF304R  |            |  |

| TYPEU          | MB9BF306NA | MB9BF305NA        | MB9BF304NA |            |  |

|                | MB9BF306RA | MB9BF305RA        | MB9BF304RA | -          |  |

|                | MB9BF306NB | MB9BF305NB        | MB9BF304NB |            |  |

|                | MB9BF306RB | MB9BF305RB        | MB9BF304RB |            |  |

|                | MB9BF106N  | MB9BF105N         | MB9BF104N  | MB9BF102N  |  |

|                | MB9BF106R  | MB9BF105R         | MB9BF104R  | MB9BF102R  |  |

|                | MB9BF106NA | MB9BF105NA        | MB9BF104NA | MB9BF102NA |  |

|                | MB9BF106RA | MB9BF105RA        | MB9BF104RA | MB9BF102RA |  |

|                |            | MB9AF105N         | MB9AF104N  | MB9AF102N  |  |

|                |            | MB9AF105R         | MB9AF104R  | MB9AF102R  |  |

|                | -          | MB9AF105NA        | MB9AF104NA | MB9AF102NA |  |

|                |            | MB9AF105RA        | MB9AF104RA | MB9AF102RA |  |

#### Table 1 TYPE0 Product list

| Table | 2 | TYPE1 | Product | list |

|-------|---|-------|---------|------|

|-------|---|-------|---------|------|

| Description in this | Flash memory size |            |            |            |            |

|---------------------|-------------------|------------|------------|------------|------------|

| manual              | 512 Kbytes        | 384 Kbytes | 256 Kbytes | 128 Kbytes | 64 Kbytes  |

|                     |                   |            | MB9AF314L  | MB9AF312L  | MB9AF311L  |

|                     | MB9AF316M         | MB9AF315M  | MB9AF314M  | MB9AF312M  | MB9AF311M  |

|                     | MB9AF316N         | MB9AF315N  | MB9AF314N  | MB9AF312N  | MB9AF311N  |

|                     | MB9AF316MA        | MB9AF315MA | MB9AF314L  | MB9AF312LA | MB9AF311LA |

|                     | MB9AF316NA        | MB9AF315NA | MB9AF314M  | MB9AF312MA | MB9AF311MA |

| TYPF1               |                   |            | MB9AF314N  | MB9AF312NA | MB9AF311NA |

| ITPEI               |                   |            | MB9AF114L  | MB9AF112L  | MB9AF111L  |

|                     | MB9AF116M         | MB9AF115M  | MB9AF114M  | MB9AF112M  | MB9AF111M  |

|                     | MB9AF116N         | MB9AF115N  | MB9AF114N  | MB9AF112N  | MB9AF111N  |

|                     | MB9AF116MA        | MB9AF115MA | MB9AF114LA | MB9AF112LA | MB9AF111LA |

|                     | MB9AF116NA        | MB9AF115NA | MB9AF114MA | MB9AF112MA | MB9AF111MA |

|                     |                   |            | MB9AF114NA | MB9AF112NA | MB9AF111NA |

#### Table 3 TYPE2 Product list

| Description in |                        | Flash memory size      |                        |  |

|----------------|------------------------|------------------------|------------------------|--|

| this manual    | 1 Mbytes               | 768 Kbytes             | 512 Kbytes             |  |

|                | MB9BFD18S              | MB9BFD17S              | MB9BFD16S              |  |

|                | MB9BFD18T              | MB9BFD17T              | MB9BFD16T              |  |

|                | MB9BF618S              | MB9BF617S              | MB9BF616S              |  |

|                | MB9BF618T              | MB9BF617T              | MB9BF616T              |  |

|                | MB9BF518S              | MB9BF517S              | MB9BF516S              |  |

|                | MB9BF518T              | MB9BF517T              | MB9BF516T              |  |

| TYPE2          | MB9BF418S              | MB9BF417S              | MB9BF416S              |  |

|                | MB9BF418T              | MB9BF417T              | MB9BF416T              |  |

|                | MB9BF318S<br>MB9BF318T | MB9BF317S<br>MB9BF317T | MB9BF316S<br>MB9BF316T |  |

|                | MB9BF218S<br>MB9BF218T | MB9BF217S<br>MB9BF217T | MB9BF216S<br>MB9BF216T |  |

|                | MB9BF118S              | MB9BF117S              | MB9BF116S              |  |

|                | MB9BF118T              | MB9BF117T              | MB9BF116T              |  |

#### Table 4 TYPE3 Product list

| Description in | Flash me                 | mory size                |

|----------------|--------------------------|--------------------------|

| this manual    | 128 Kbytes               | 64 Kbytes                |

|                | MB9AF132K<br>MB9AF132L   | MB9AF131K<br>MB9AF131L   |

| TYPE3          | MB9AF132KA<br>MB9AF132LA | MB9AF131KA<br>MB9AF131LA |

|                | MB9AF132KB<br>MB9AF132LB | MB9AF131KB<br>MB9AF131LB |

#### Table 5 TYPE4 Product list

| Description in | Flash memory size |            |            |            |

|----------------|-------------------|------------|------------|------------|

| this manual    | 512 Kbytes        | 384 Kbytes | 256 Kbytes | 128 Kbytes |

|                | MB9BF516N         | MB9BF515N  | MB9BF514N  | MB9BF512N  |

|                | MB9BF516R         | MB9BF515R  | MB9BF514R  | MB9BF512R  |

| TYPF4          | MB9BF416N         | MB9BF415N  | MB9BF414N  | MB9BF412N  |

|                | MB9BF416R         | MB9BF415R  | MB9BF414R  | MB9BF412R  |

| TTPE4          | MB9BF316N         | MB9BF315N  | MB9BF314N  | MB9BF312N  |

|                | MB9BF316R         | MB9BF315R  | MB9BF314R  | MB9BF312R  |

|                | MB9BF116N         | MB9BF115N  | MB9BF114N  | MB9BF112N  |

|                | MB9BF116R         | MB9BF115R  | MB9BF114R  | MB9BF112R  |

#### Table 6 TYPE5 Product list

| Description in this | Flash me   | mory size |

|---------------------|------------|-----------|

| manual              | 128 Kbytes | 64 Kbytes |

| TYPE5               | MB9AF312K  | MB9AF311K |

|                     | MB9AF112K  | MB9AF111K |

|                     | •          |           |

| Description in |            | Flash memory size |            |

|----------------|------------|-------------------|------------|

| this manual    | 256 Kbytes | 128 Kbytes        | 64 Kbytes  |

|                | MB9AFB44L  | MB9AFB42L         | MB9AFB41L  |

|                | MB9AFB44M  | MB9AFB42M         | MB9AFB41M  |

|                | MB9AFB44N  | MB9AFB42N         | MB9AFB41N  |

|                | MB9AFB44LA | MB9AFB42LA        | MB9AFB41LA |

|                | MB9AFB44MA | MB9AFB42MA        | MB9AFB41MA |

|                | MB9AFB44NA | MB9AFB42NA        | MB9AFB41NA |

|                | MB9AFB44LB | MB9AFB42LB        | MB9AFB41LB |

|                | MB9AFB44MB | MB9AFB42MB        | MB9AFB41MB |

|                | MB9AFB44NB | MB9AFB42NB        | MB9AFB41NB |

|                | MB9AFA44L  | MB9AFA42L         | MB9AFA41L  |

|                | MB9AFA44M  | MB9AFA42M         | MB9AFA41M  |

|                | MB9AFA44N  | MB9AFA42N         | MB9AFA41N  |

|                | MB9AFA44LA | MB9AFA42LA        | MB9AFA41LA |

|                | MB9AFA44MA | MB9AFA42MA        | MB9AFA41MA |

|                | MB9AFA44NA | MB9AFA42NA        | MB9AFA41NA |

|                | MB9AFA44LB | MB9AFA42LB        | MB9AFA41LB |

|                | MB9AFA44MB | MB9AFA42MB        | MB9AFA41MB |

|                | MB9AFA44NB | MB9AFA42NB        | MB9AFA41NB |

| TYPE6          | MB9AF344L  | MB9AF342L         | MB9AF341L  |

|                | MB9AF344M  | MB9AF342M         | MB9AF341M  |

|                | MB9AF344N  | MB9AF342N         | MB9AF341N  |

|                | MB9AF344LA | MB9AF342LA        | MB9AF341LA |

|                | MB9AF344MA | MB9AF342MA        | MB9AF341MA |

|                | MB9AF344NA | MB9AF342NA        | MB9AF341NA |

|                | MB9AF344LB | MB9AF342LB        | MB9AF341LB |

|                | MB9AF344MB | MB9AF342MB        | MB9AF341MB |

|                | MB9AF344NB | MB9AF342NB        | MB9AF341NB |

|                | MB9AF144L  | MB9AF142L         | MB9AF141L  |

|                | MB9AF144M  | MB9AF142M         | MB9AF141M  |

|                | MB9AF144N  | MB9AF142N         | MB9AF141N  |

|                | MB9AF144LA | MB9AF142LA        | MB9AF141LA |

|                | MB9AF144MA | MB9AF142MA        | MB9AF141MA |

|                | MB9AF144NA | MB9AF142NA        | MB9AF141NA |

|                | MB9AF144LB | MB9AF142LB        | MB9AF141LB |

|                | MB9AF144MB | MB9AF142MB        | MB9AF141MB |

|                | MB9AF144NB | MB9AF142NB        | MB9AF141NB |

#### Table 7 TYPE6 product list

#### Table 8 TYPE7 product list

| Description in | Flash me   | emory size |

|----------------|------------|------------|

| this manual    | 128 Kbytes | 64 Kbytes  |

|                | MB9AFA32L  | MB9AFA31L  |

|                | MB9AFA32M  | MB9AFA31M  |

|                | MB9AFA32N  | MB9AFA31N  |

|                | MB9AF132M  | MB9AF131M  |

| TYPF7          | MB9AF132N  | MB9AF131N  |

| ITFE/          | MB9AFAA2L  | MB9AFAA1L  |

|                | MB9AFAA2M  | MB9AFAA1M  |

|                | MB9AFAA2N  | MB9AFAA1N  |

|                | MB9AF1A2M  | MB9AF1A1M  |

|                | MB9AF1A2N  | MB9AF1A1N  |

#### Table 9 TYPE8 product list

| Description in | Flash memory size |            |            |

|----------------|-------------------|------------|------------|

| this manual    | 512 Kbytes        | 384 Kbytes | 256 Kbytes |

|                | MB9AF156M         | MB9AF155M  | MB9AF154M  |

|                | MB9AF156N         | MB9AF155N  | MB9AF154N  |

|                | MB9AF156R         | MB9AF155R  | MB9AF154R  |

|                | MB9AF156MA        | MB9AF155MA | MB9AF154MA |

| TYPE8          | MB9AF156NA        | MB9AF155NA | MB9AF154NA |

|                | MB9AF156RA        | MB9AF155RA | MB9AF154RA |

|                | MB9AF156MB        | MB9AF155MB | MB9AF154MB |

|                | MB9AF156NB        | MB9AF155NB | MB9AF154NB |

|                | MB9AF156RB        | MB9AF155RB | MB9AF154RB |

#### Table 10TYPE9 product list

| Description in | Flash memory size |            |           |

|----------------|-------------------|------------|-----------|

| this manual    | 256 Kbytes        | 128 Kbytes | 64 Kbytes |

|                | MB9BF524K         | MB9BF522K  | MB9BF521K |

|                | MB9BF524L         | MB9BF522L  | MB9BF521L |

|                | MB9BF524M         | MB9BF522M  | MB9BF521M |

|                | MB9BF324K         | MB9BF322K  | MB9BF321K |

| TYPE9          | MB9BF324L         | MB9BF322L  | MB9BF321L |

|                | MB9BF324M         | MB9BF322M  | MB9BF321M |

|                | MB9BF124K         | MB9BF122K  | MB9BF121K |

|                | MB9BF124L         | MB9BF122L  | MB9BF121L |

|                | MB9BF124M         | MB9BF122M  | MB9BF121M |

#### Table 11 TYPE10 product list

| Description in | Flash memory size |  |

|----------------|-------------------|--|

| this manual    | 64 Kbytes         |  |

| TYPE10         | MB9BF121J         |  |

| Description in | Flash memory size |

|----------------|-------------------|

| this manual    | 64 Kbytes         |

| TYPE11 -       | MB9AF421K         |

|                | MB9AF421L         |

|                | MB9AF121K         |

|                | MB9AF121L         |

#### Table 12 TYPE11 product list

#### Table 13 TYPE12 product list

| Description in | Flash mer  | mory size  |

|----------------|------------|------------|

| this manual    | 1.5 Mbytes | 1 Mbytes   |

|                | MB9BF529S  | MB9BF528S  |

|                | MB9BF529T  | MB9BF528T  |

|                | MB9BF529SA | MB9BF528SA |

|                | MB9BF529TA | MB9BF528TA |

|                | MB9BF429S  | MB9BF428S  |

|                | MB9BF429T  | MB9BF428T  |

|                | MB9BF429SA | MB9BF428SA |

| TYPE12         | MB9BF429TA | MB9BF428TA |

| TTPEIZ         | MB9BF329S  | MB9BF328S  |

|                | MB9BF329T  | MB9BF328T  |

|                | MB9BF329SA | MB9BF328SA |

|                | MB9BF329TA | MB9BF328TA |

|                | MB9BF129S  | MB9BF128S  |

|                | MB9BF129T  | MB9BF128T  |

|                | MB9BF129SA | MB9BF128SA |

|                | MB9BF129TA | MB9BF128TA |

# Contents

| CHAPTER 1-1: Multi-function Serial Interface19                                                | 9      |

|-----------------------------------------------------------------------------------------------|--------|

| 1. Overview of the Multi-function Serial Interface                                            | 0      |

| CHAPTER 1-2: UART (Asynchronous Serial Interface)2                                            | 3      |

| 1. Overview of UART (Asynchronous Serial Interface)24                                         | 4      |

| 2. UART Interrupt                                                                             | 6      |

| 2.2. Interrupt and flag set timing when received FIFO is used                                 |        |

| 2.3. Interrupt and flag set timing when transmit FIFO is used                                 |        |

| 3. UART Operation                                                                             | 2      |

| 4. Dedicated Baud Rate Generator                                                              |        |

| 5. Setting Procedure and Program Flow in Operation Mode 0 (Asynchronous Normal Mode) 46       | 6      |

| 6. Setting Procedure and Program Flow in Operation Mode 1 (Asynchronous Multiprocessor Mode)4 | 9      |

| <ul> <li>7. UART (Asynchronous Serial Interface) Registers</li></ul>                          | 4<br>7 |

| 7.4. Extended Communication Control Register (ESCR)                                           |        |

| 7.5. Received Data Register/Transmit Data Register (RDR/TDR)6                                 |        |

| 7.6. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)                                    |        |

| 7.7. FIFO Control Register 1 (FCR1)                                                           |        |

| 7.8. FIFO Control Register 0 (FCR0)                                                           |        |

| CHAPTER 1-3: CSIO (Clock Synchronous Serial Interface)                                            | 77  |

|---------------------------------------------------------------------------------------------------|-----|

| 1. Overview of CSIO (Clock Synchronous Serial Interface)                                          | 78  |

| 2. CSIO (Clock Synchronous Serial Interface) interrupts                                           |     |

| 2.1. Received interrupt and flag set timing                                                       |     |

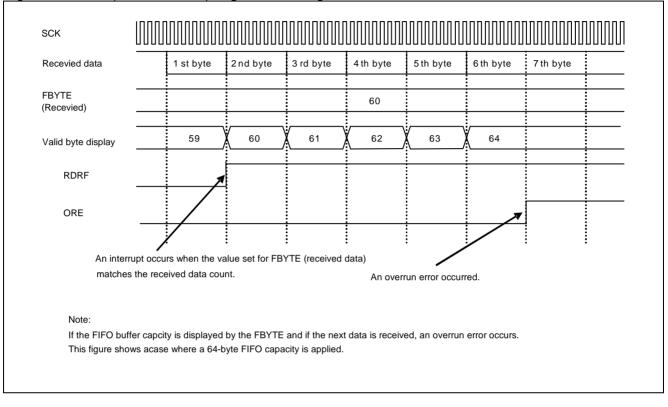

| 2.2. Interrupt and flag set timing when received FIFO is used                                     |     |

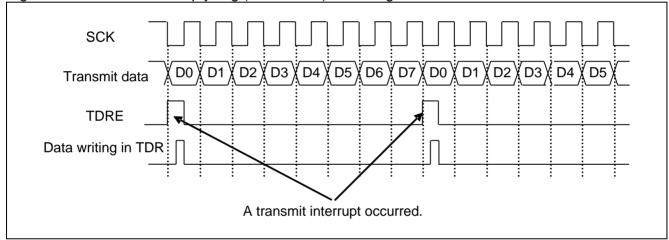

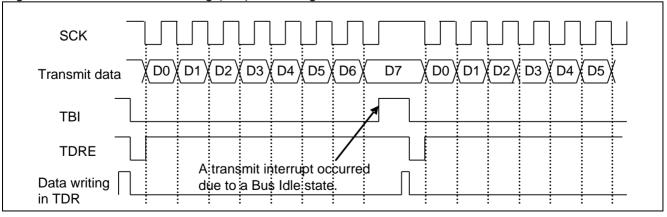

| 2.3. Transmit interrupt and flag set timing                                                       |     |

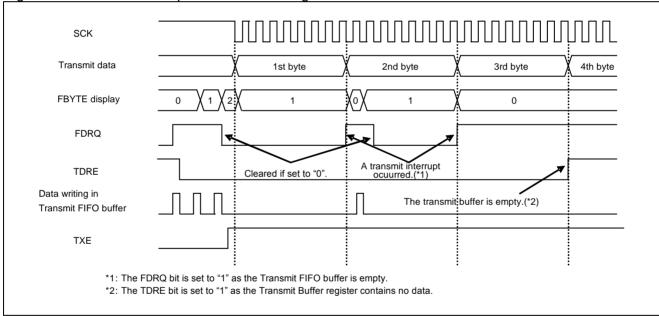

| 2.4. Interrupt and flag set timing when transmit FIFO is used                                     |     |

| 3. CSIO (Clock Synchronous Serial Interface) operations                                           |     |

| 3.1. Normal transfer (I)                                                                          |     |

| 3.2. Normal transfer (II)                                                                         |     |

| 3.3. SPI transfer (I)                                                                             |     |

| 3.4. SPI transfer (II)                                                                            |     |

| 4. Dedicated baud rate generator                                                                  | 106 |

| 4.1. Baud rate settings                                                                           |     |

| 4.2. CSIO (Clock Synchronous Serial Interface) setup procedure and program flow                   | 110 |

| 5. CSIO (Clock Synchronous Serial Interface) registers                                            | 112 |

| 5.1. Serial Control Register (SCR)                                                                | 113 |

| 5.2. Serial Mode Register (SMR)                                                                   |     |

| 5.3. Serial Status Register (SSR)                                                                 |     |

| 5.4. Extended Communication Control Register (ESCR)                                               |     |

| 5.5. Received Data Register/Transmit Data Register (RDR/TDR)                                      |     |

| 5.6. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)<br>5.7. FIFO Control Register 1 (FCR1) |     |

| 5.8. FIFO Control Register 0 (FCR0)                                                               |     |

| 5.9. FIFO Byte Register (FBYTE)                                                                   |     |

|                                                                                                   |     |

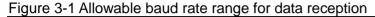

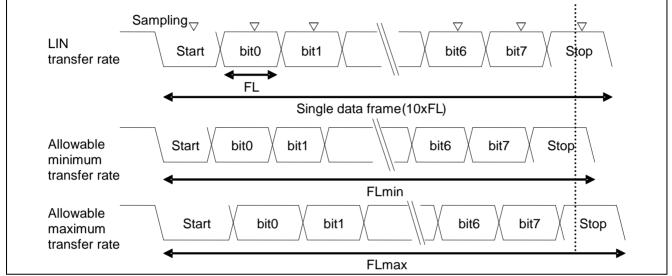

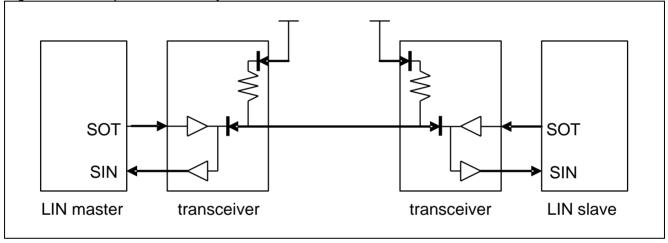

| CHAPTER 1-4: LIN Interface (Ver. 2.1) (LIN Communication Control Interface Ver. 2.1)              |     |

| 1. Overview of LIN Interface (Ver. 2.1) (LIN Communication Control Interface Ver. 2.1)            |     |

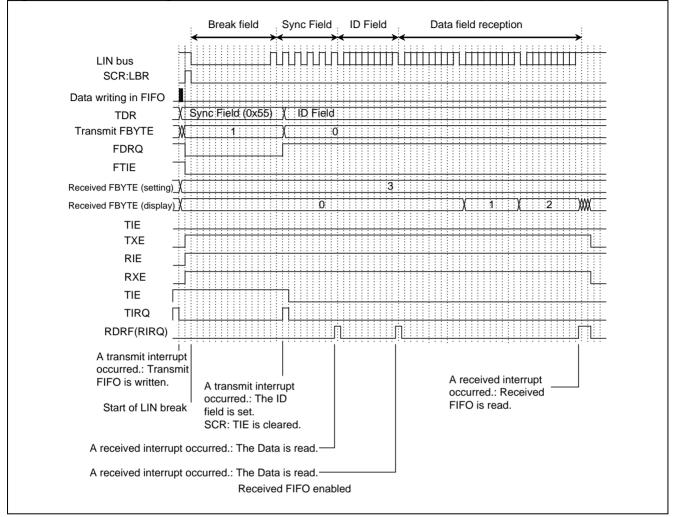

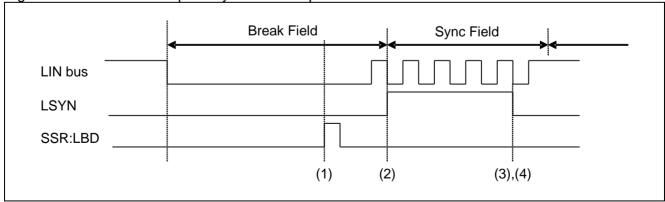

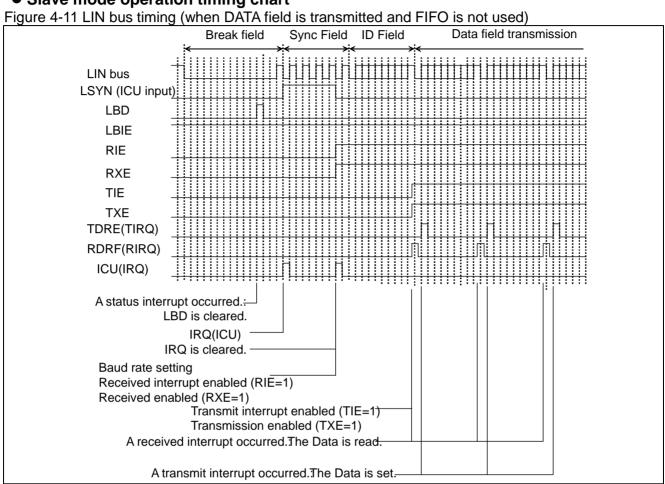

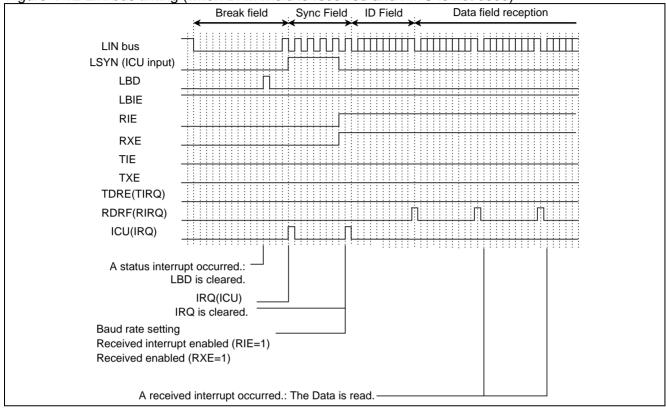

| 2. LIN Interface (Ver. 2.1) Interrupts                                                            |     |

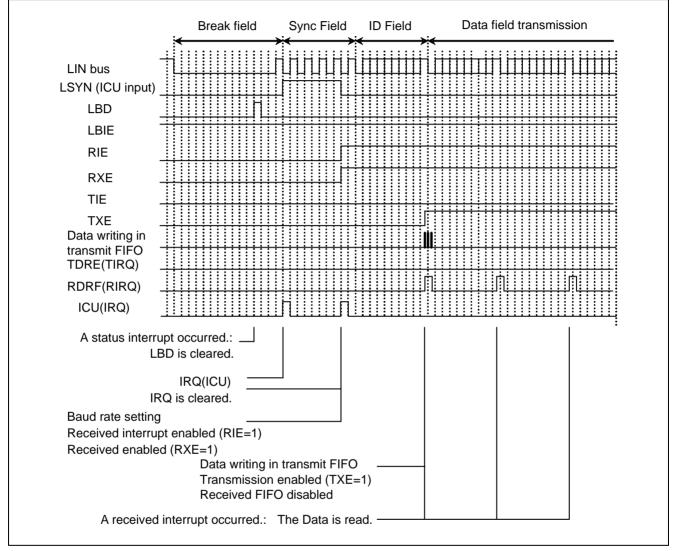

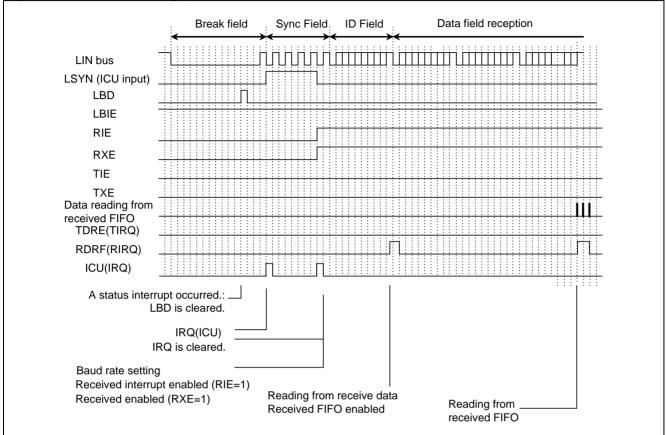

| 2.1. Received interrupt and flag set timing                                                       |     |

| 2.2. Interrupt and flag set timing when received FIFO is used                                     |     |

| 2.3. Transmit interrupt and flag set timing                                                       |     |

| 2.4. Interrupt and flag set timing when transmit FIFO is used                                     |     |

| 3. Dedicated Baud Rate Generator                                                                  |     |

| 3.1. Baud rate settings                                                                           |     |

| 4. LIN Interface (Ver. 2.1) Operations                                                            | 150 |

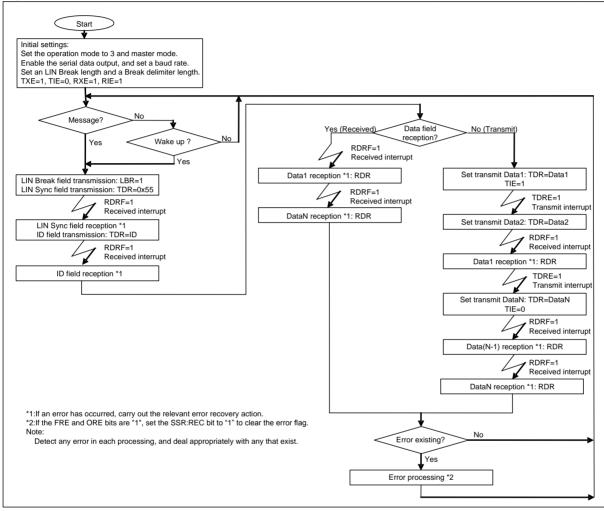

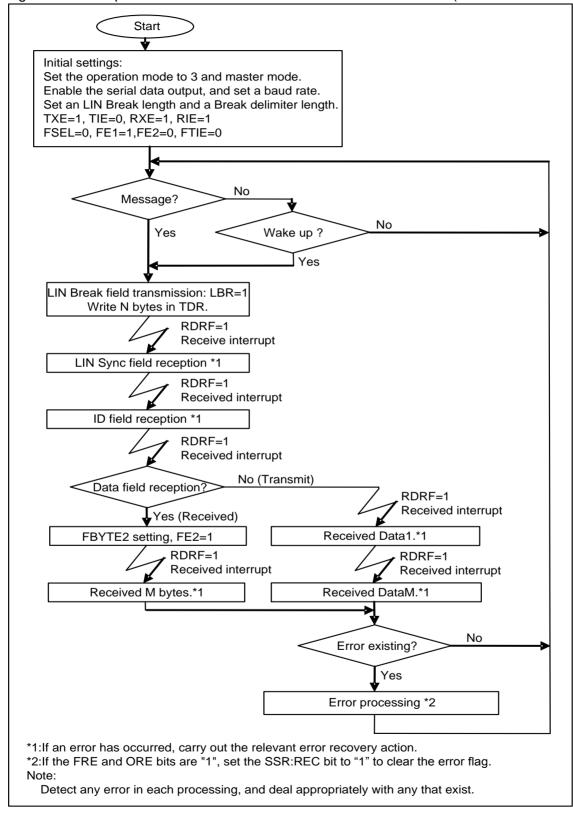

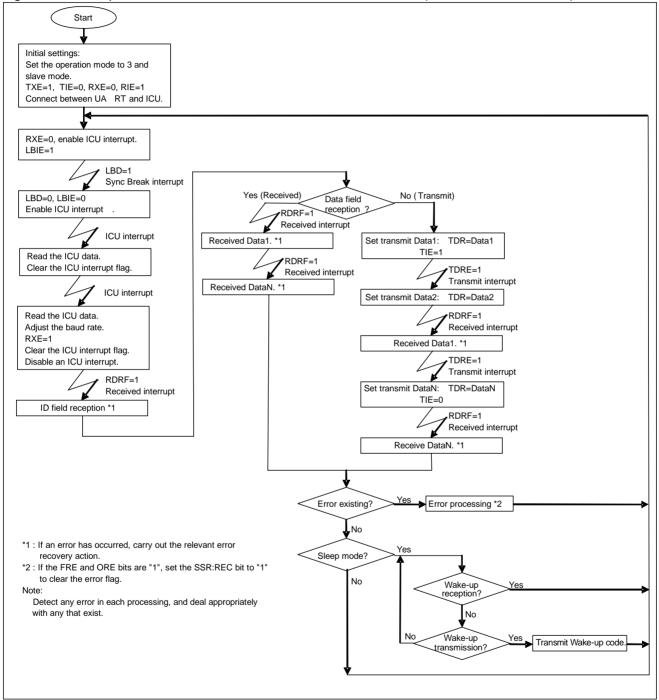

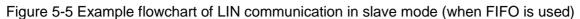

| 5. Operation Mode 3 (LIN Communication Mode) Setting Procedure and Program Flow                   | 163 |

| 6. LIN Interface (ver. 2.1) Registers                                                             | 168 |

| 6.1. Serial Control Register (SCR)                                                                |     |

| 6.2. Serial Mode Register (SMR)                                                                   |     |

| 6.3. Serial Status Register (SSR)                                                                 |     |

| 6.4. Extended Communication Control Register (ESCR)                                               |     |

| 6.5. Received Data Register/Transmit Data Register (RDR/TDR)                                      |     |

| 6.6. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)                                        |     |

| 6.7. FIFO Control Register 1 (FCR1)<br>6.8. FIFO Control Register 0 (FCR0)                        |     |

| 6.9. FIFO Byte Register (FBYTE)                                                                   |     |

|                                                                                                   |     |

| APTER 1-5: I <sup>2</sup> C Interface (I <sup>2</sup> C Communications Control Interface)                                                                                                                                                                          |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1. Overview of I <sup>2</sup> C Interface (I <sup>2</sup> C Communications Control Interface)                                                                                                                                                                      |     |

| 2. I <sup>2</sup> C Interface interrupt                                                                                                                                                                                                                            |     |

| 2.1. I <sup>2</sup> C interface operation                                                                                                                                                                                                                          |     |

| 2.2. Master mode                                                                                                                                                                                                                                                   |     |

| 2.3. Slave mode<br>2.4. Bus error                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                    |     |

| 3. Dedicated Baud Rate Generator                                                                                                                                                                                                                                   |     |

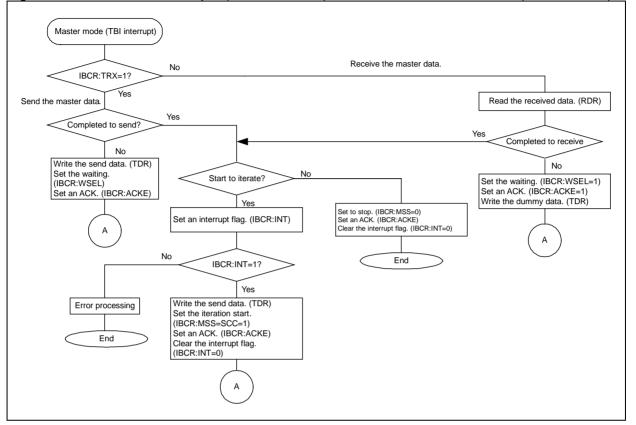

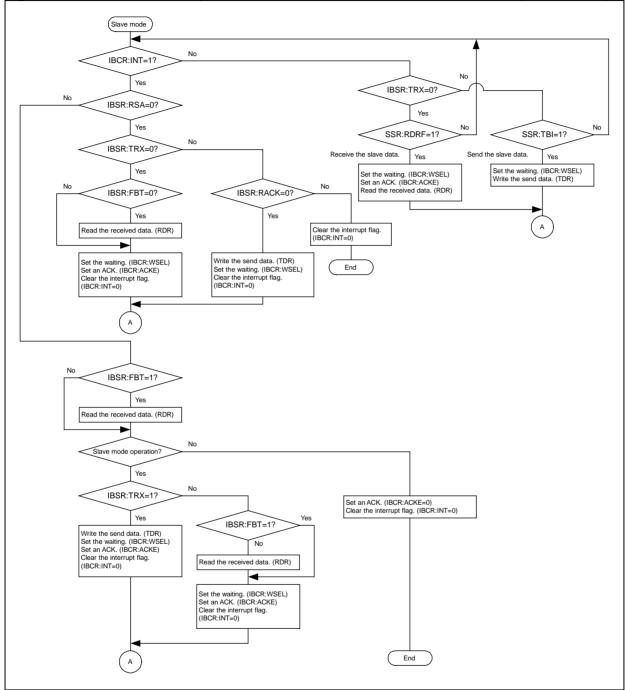

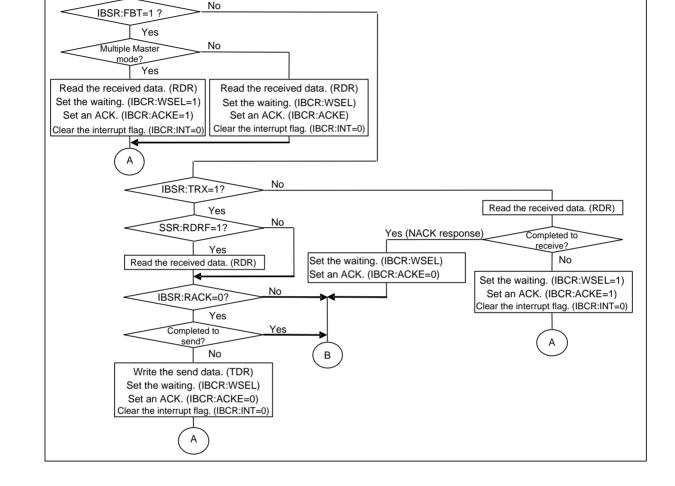

| 4. I <sup>2</sup> C communication operation flowchart examples                                                                                                                                                                                                     |     |

| 5. I <sup>2</sup> C Interface Registers                                                                                                                                                                                                                            |     |

| 5.1. I <sup>2</sup> C Bus Control Register (IBCR)                                                                                                                                                                                                                  |     |

| 5.2. Serial Mode Register (SMR)<br>5.3. I <sup>2</sup> C Bus Status Register (IBSR)                                                                                                                                                                                |     |

| 5.4. Serial Status Register (SSR)                                                                                                                                                                                                                                  |     |

| 5.5. Received Data Register/Transmit Data Register (RDR/TDR)                                                                                                                                                                                                       |     |

| 5.6. Received Data Register/Transmit Data Register (RDR/TDR)                                                                                                                                                                                                       |     |

| 5.7. 7-bit Slave Address Mask Register (ISMK)                                                                                                                                                                                                                      |     |

| 5.8. 7-bit Slave Address Register (ISBA)                                                                                                                                                                                                                           |     |

| 5.9. Baud Rate Generator Registers 1 and 0 (BGR1 and BGR0)                                                                                                                                                                                                         |     |

| 5.10. FIFO Control Register 1 (FCR1)                                                                                                                                                                                                                               |     |

| 5.11. FIFO Control Register 0 (FCR0)                                                                                                                                                                                                                               |     |

| 5.12. FIFO Byte Register (FBYTE)                                                                                                                                                                                                                                   | 278 |

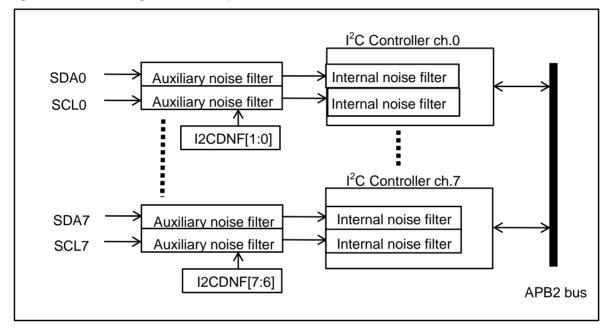

| APTER 1-6: I <sup>2</sup> C Auxiliary Noise Filter                                                                                                                                                                                                                 |     |

| 1. Overview and Configuration                                                                                                                                                                                                                                      |     |

| 2. Register of I <sup>2</sup> C Auxiliary Noise Filter                                                                                                                                                                                                             |     |

| 2.1. I <sup>2</sup> C Auxiliary Noise Filter Setting Register (I2CDNF)                                                                                                                                                                                             |     |

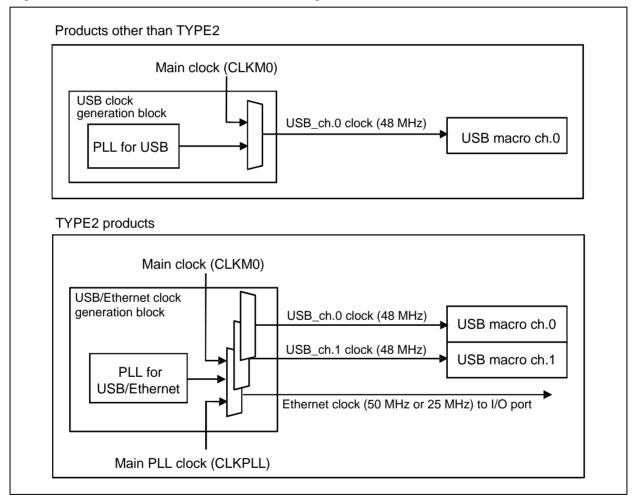

| APTER 2-1: USB/Ethernet Clock Generation Block                                                                                                                                                                                                                     |     |

| 1. Overview and Configuration                                                                                                                                                                                                                                      |     |

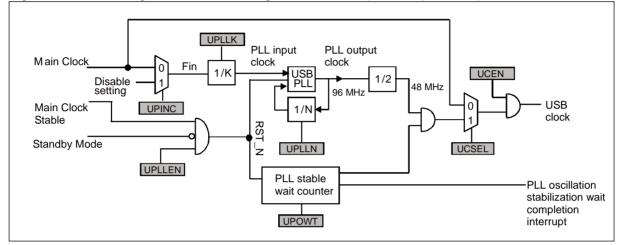

| APTER 2-2: USB Clock Generation                                                                                                                                                                                                                                    |     |

| 1. Overview                                                                                                                                                                                                                                                        |     |

|                                                                                                                                                                                                                                                                    |     |

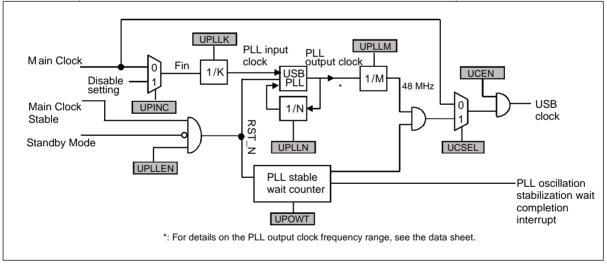

| 2. Configuration and Block Diagram                                                                                                                                                                                                                                 |     |

| 3. Explanation of Operation                                                                                                                                                                                                                                        |     |

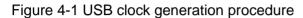

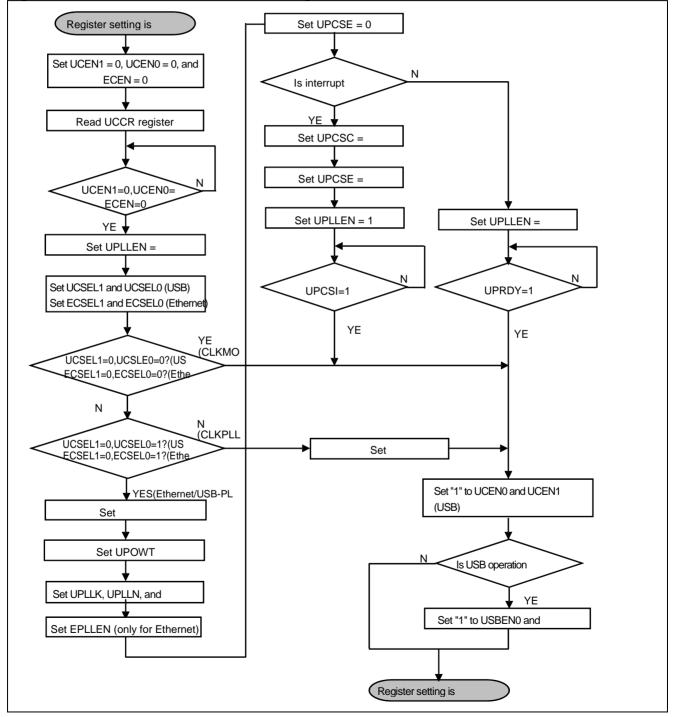

| 4. Setup Procedure Example                                                                                                                                                                                                                                         |     |

| 5. Register List.                                                                                                                                                                                                                                                  |     |

| 5.1. USB Clock Control Register (UCCR)                                                                                                                                                                                                                             |     |

| 5.2. USB-PLL Control Register1 (UPCR1)                                                                                                                                                                                                                             |     |

| 5.3. USB-PLL Control Register2 (UPCR2)                                                                                                                                                                                                                             |     |

| 5.4. USB-PLL Control Register 3 (UPCR3)                                                                                                                                                                                                                            |     |

| 5.5. USB-PLL Control Register 4 (UPCR4)                                                                                                                                                                                                                            |     |

| 5.6 USB DLL Control Productor 5 (UDCD5)                                                                                                                                                                                                                            |     |

| 5.6. USB-PLL Control Register 5 (UPCR5)                                                                                                                                                                                                                            |     |

| 5.7. USB-PLL Status Register (UP_STR)                                                                                                                                                                                                                              |     |

| 5.7. USB-PLL Status Register (UP_STR)<br>5.8. USB-PLL Interrupt Source Enable Register (UPINT_ENR)                                                                                                                                                                 |     |

| <ul> <li>5.7. USB-PLL Status Register (UP_STR)</li> <li>5.8. USB-PLL Interrupt Source Enable Register (UPINT_ENR)</li> <li>5.9. USB-PLL Interrupt Source Status Register (UPINT_STR)</li> </ul>                                                                    |     |

| <ul> <li>5.7. USB-PLL Status Register (UP_STR)</li> <li>5.8. USB-PLL Interrupt Source Enable Register (UPINT_ENR)</li> <li>5.9. USB-PLL Interrupt Source Status Register (UPINT_STR)</li> <li>5.10. USB-PLL Interrupt Source Clear Register (UPINT_CLR)</li> </ul> |     |

| <ul> <li>5.7. USB-PLL Status Register (UP_STR)</li> <li>5.8. USB-PLL Interrupt Source Enable Register (UPINT_ENR)</li> <li>5.9. USB-PLL Interrupt Source Status Register (UPINT_STR)</li> </ul>                                                                    |     |

Contents

| CHAPTER 2-3: USB/Ethernet Clock Generation                          |  |

|---------------------------------------------------------------------|--|

| 1. Overview                                                         |  |

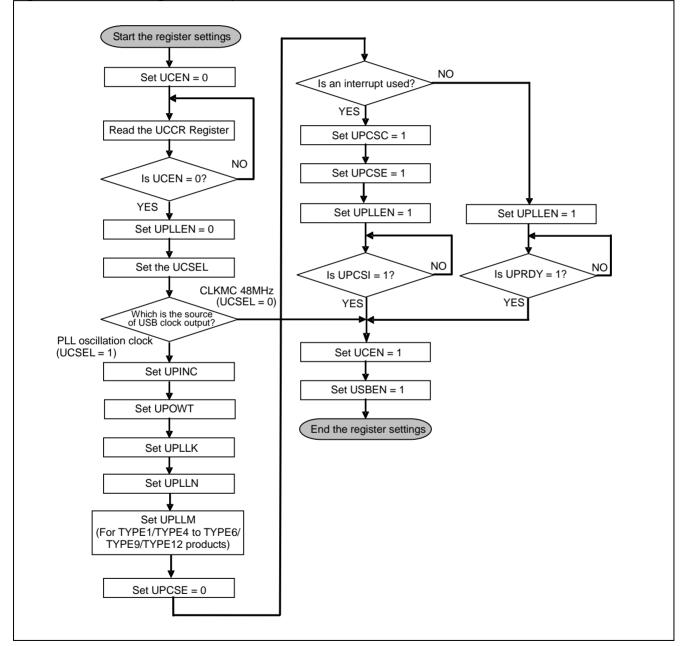

| 2. Configuration and Block Diagram                                  |  |

| 3. Description of Operation                                         |  |

| 4. Example of Setting Procedure                                     |  |

| 5. List of Registers                                                |  |

| 5.1. USB/Ethernet Clock Setting Register (UCCR)                     |  |

| 5.2. USB/Ethernet-PLL Setting Register1 (UPCR1)                     |  |

| 5.3. USB/Ethernet-PLL Setting Register2 (UPCR2)                     |  |

| 5.4. USB/Ethernet-PLL Setting Register3 (UPCR3)                     |  |

| 5.5. USB/Ethernet-PLL Setting Register4 (UPCR4)                     |  |

| 5.6. USB/Ethernet-PLL Setting Register5 (UPCR5)                     |  |

| 5.7. USB/Ethernet-PLL Setting Register6 (UPCR6)                     |  |

| 5.8. USB/Ethernet-PLL Setting Register7 (UPCR7)                     |  |

| 5.9. USB/Ethernet-PLL State Register (UP_STR)                       |  |

| 5.10. USB/Ethernet-PLL Interrupt Factor Enable Register (UPINT_ENR) |  |

| 5.11. USB/Ethernet-PLL Interrupt Factor State Register (UPINT_STR)  |  |

| 5.12. USB/Ethernet-PLL Interrupt Factor Clear Register (UPINT_CLR)  |  |

| 5.13. USB (ch.0) Enable Register (USBEN0)                           |  |

| 5.14. USB (ch.1) Enable Register (USBEN1)                           |  |

| 6. Usage Precautions                                                |  |

| CHAPTER 3-1: USB Device (USB Function)                              |  |

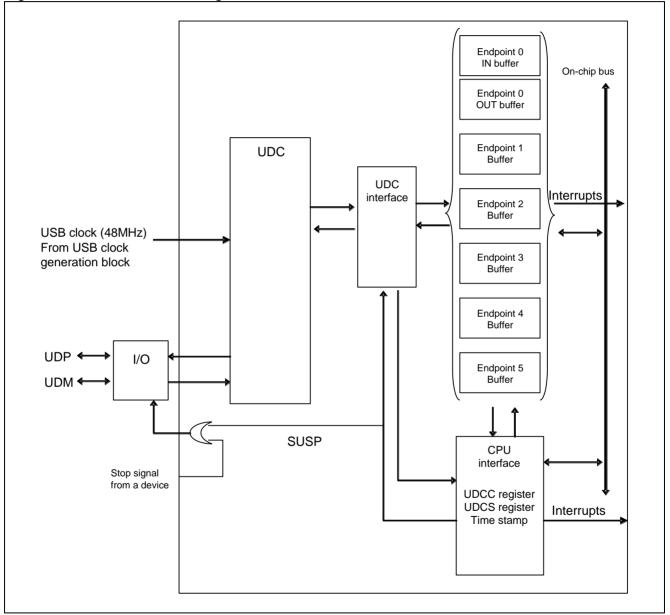

| 1. Overview of USB Device                                           |  |

| 1.1. Features of USB Device                                         |  |

| 2. Configuration of USB Device                                      |  |

| 3. Operations of USB Device                                         |  |

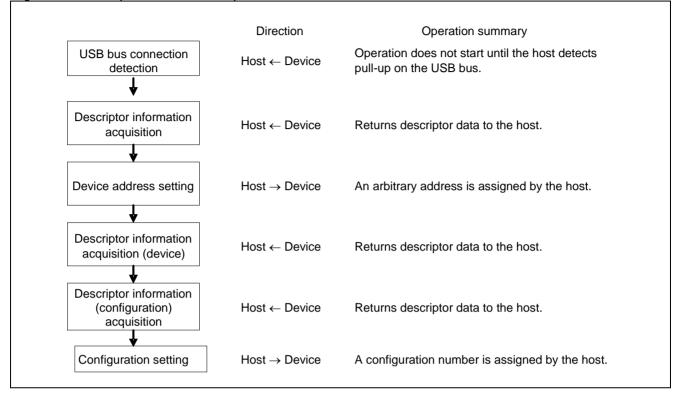

| 3.1. USB function operation                                         |  |

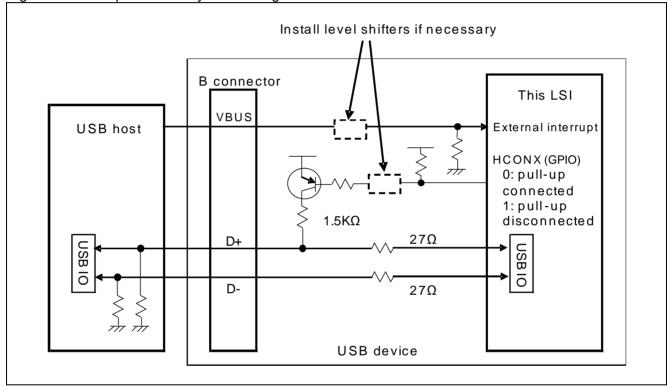

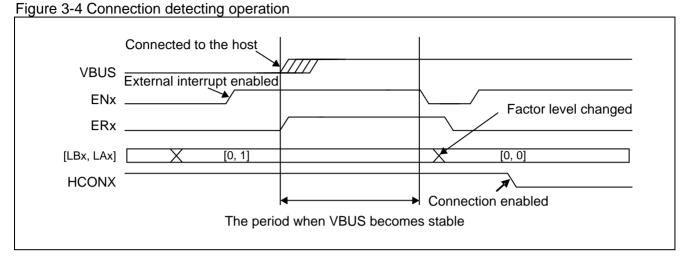

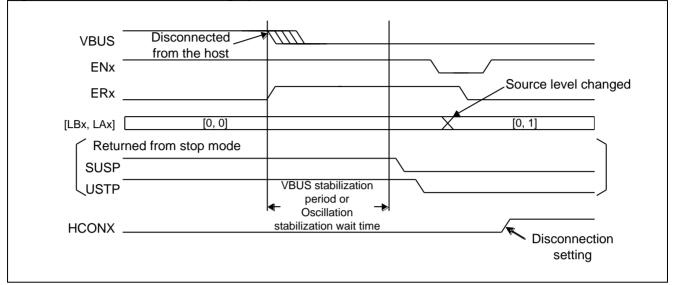

| 3.2. Detection of connection and disconnection                      |  |

| 3.3. Operation of each register in response to a command            |  |

| 3.4. Suspend function                                               |  |

| 3.5. Wake-up function                                               |  |

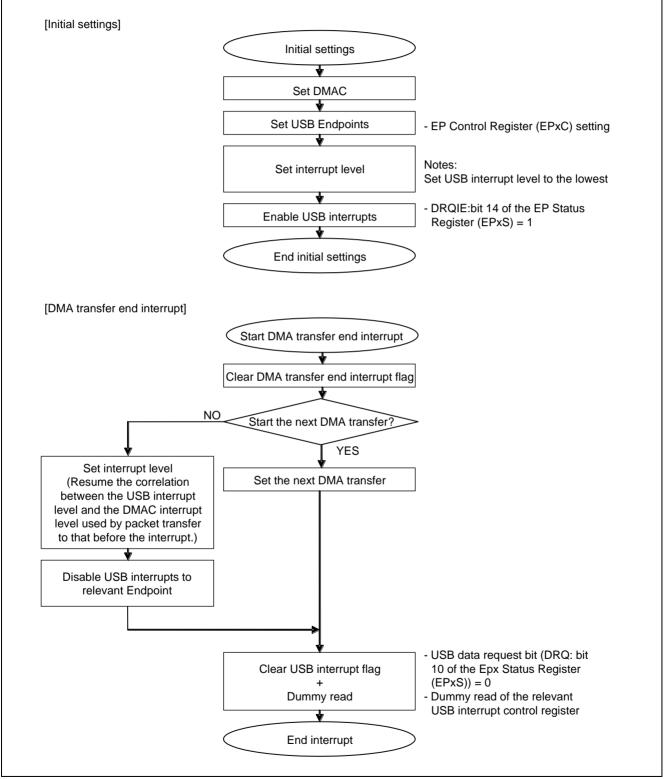

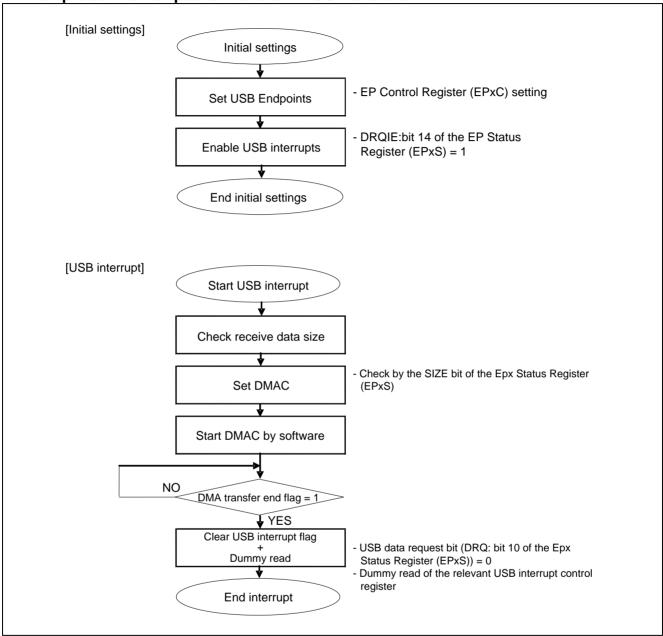

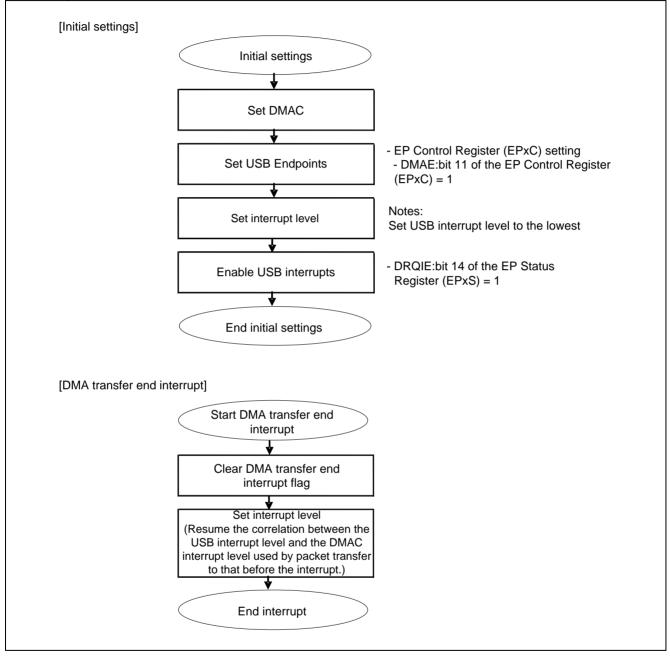

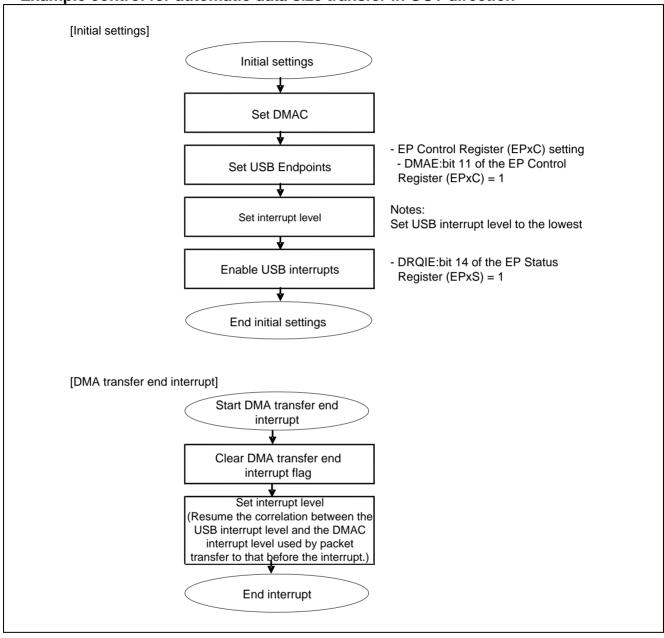

| 3.6. DMA transfer function                                          |  |

| 3.7. NULL transfer function                                         |  |

| 3.8. STALL response/release of endpoint 0                           |  |

| 3.9. STALL response/release of endpoints 1 to 5                     |  |

| 4. Examples of USB Device Setting Procedures                        |  |

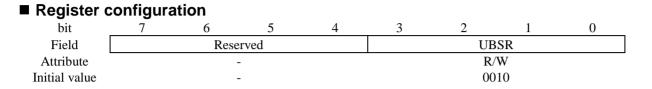

| 5. USB Device Registers                                             |  |

| 5.1. UDC Control Register (UDCC)                                    |  |

| 5.2. EP0 Control Register (EP0C)                                    |  |

| 5.3. EP1 to EP5 Control Registers (EP1C to EP5C)                    |  |

| 5.4. Time Stamp Register (TMSP)                                     |  |

| 5.5. UDC Status Register (UDCS)                                     |  |

| 5.6. UDC Interrupt Enable Register (UDCIE)                          |  |

| 5.7. EPOI Status Register (EPOIS)                                   |  |

| 5.8. EP00 Status Register (EP00S)                                   |  |

| 5.9. EP1 to EP5 Status Registers (EP1S to EP5S)                     |  |

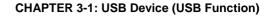

| 5.10. EP0 to EP5 Data Registers (EP0DTH to EP5DTH/EP0DTL to EP5DTL) |  |

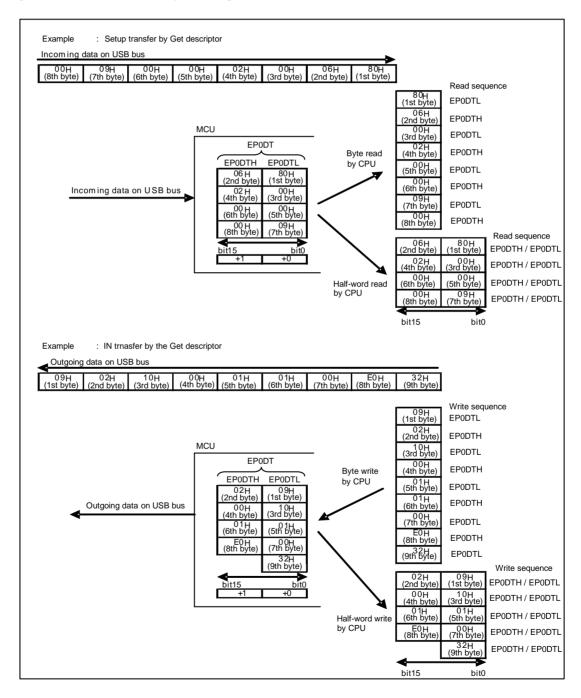

| CHAPTER 3-2: USB Host                                 |     |

|-------------------------------------------------------|-----|

| 1. Overview of USB host                               |     |

| 2. USB Host Configuration                             |     |

| 3. USB Host Operations                                |     |

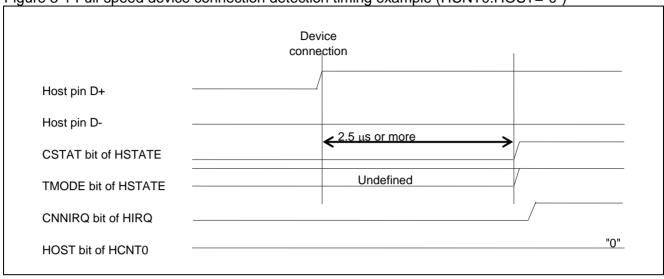

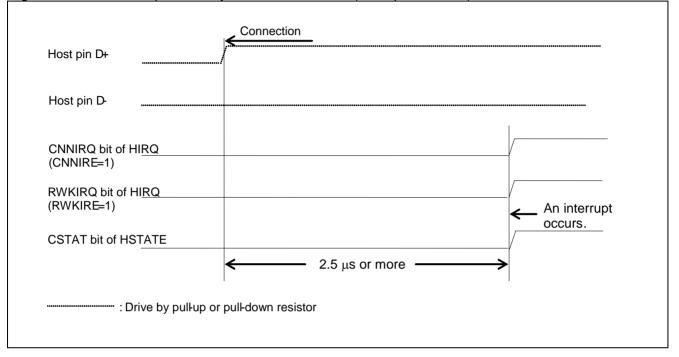

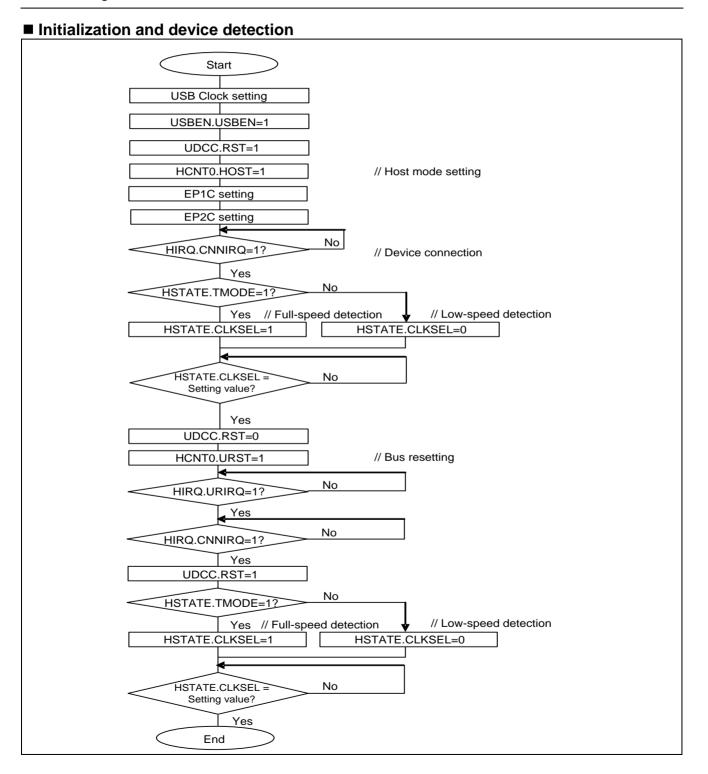

| 3.1. Device connection                                |     |

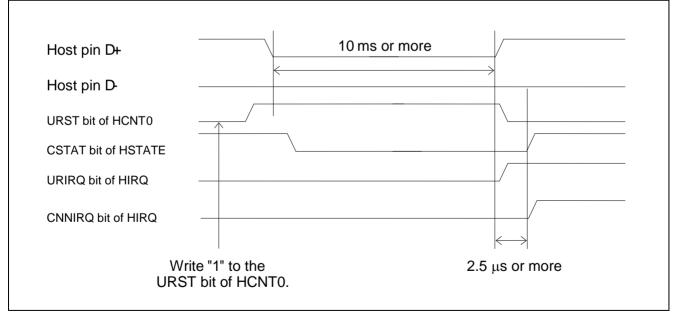

| 3.2. USB bus resetting                                |     |

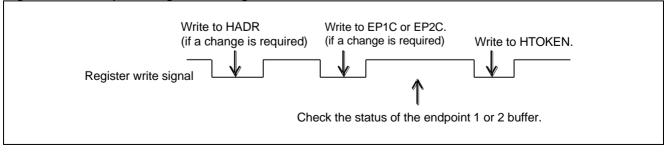

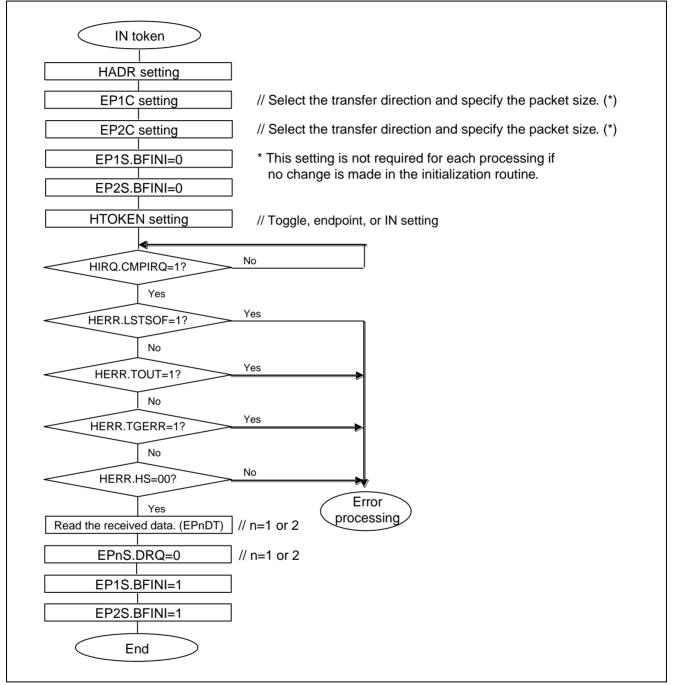

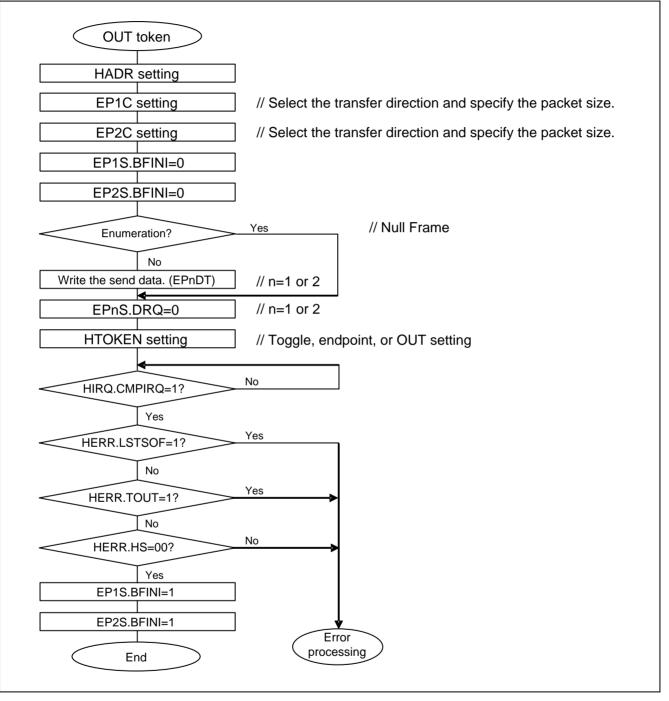

| 3.3. Token packet                                     |     |

| 3.4. Data packet                                      |     |

| 3.5. Handshake packet                                 |     |

| 3.6. Retry function                                   | 411 |

| 3.7. SOF interrupt                                    |     |

| 3.8. Error status                                     |     |

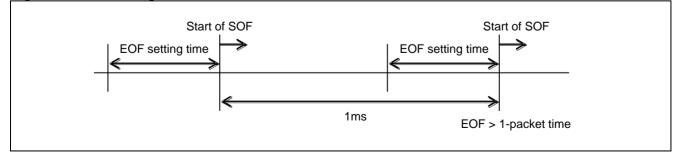

| 3.9. End of packet                                    | 415 |

| 3.10. Suspend and resume operations                   |     |

| 3.11. Device disconnection                            | 419 |

| 4. USB Host Setting Procedure Examples                |     |

| 5. USB Host Registers                                 |     |

| 5.1. Host Control Registers 0 and 1 (HCNT0 and HCNT1) |     |

| 5.2. Host Interrupt Register (HIRQ)                   |     |

| 5.3. Host Error Status Register (HERR)                |     |

| 5.4. Host Status Register (HSTATE)                    |     |

| 5.5. SOF Interrupt Frame Compare Register (HFCOMP)    |     |

| 5.6. Retry Timer Setup Register (HRTIMER)             |     |

| 5.7. Host Address Register (HADR)                     |     |

| 5.8. EOF Setup Register (HEOF)                        |     |

| 5.9. Frame Setup Register (HFRAME)                    |     |

| 5.10. Host Token Endpoint Register (HTOKEN)           |     |

| CHAPTER 4: Ethernet                                   |     |

| CHAPTER 5-1: CAN Prescaler                            | 451 |

| 1. Overview and Configuration                         |     |

| 2. CAN Prescaler Register                             |     |

| 2.1. CAN Prescaler Register (CANPRE)                  |     |

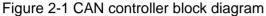

| CHAPTER 5-2: CAN Controller                                                                                                   | 455 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 1. Overview                                                                                                                   | 456 |

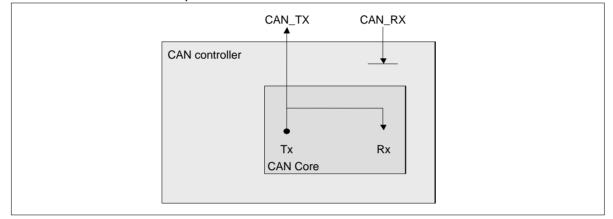

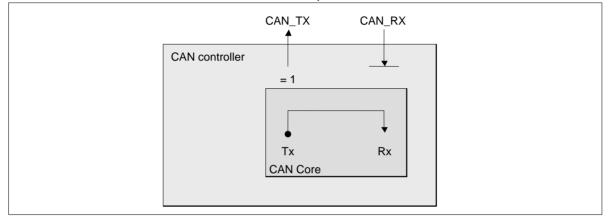

| 2. Configuration                                                                                                              | 457 |

| 3. CAN Controller Operations                                                                                                  | 458 |

| 3.1. Message objects                                                                                                          |     |

| 3.2. Message transmission                                                                                                     |     |

| 3.3. Message reception                                                                                                        |     |

| 3.4. FIFO buffer function                                                                                                     | 467 |

| 3.5. Interrupt function                                                                                                       | 469 |

| 3.6. Bit timing                                                                                                               | 470 |

| 3.7. Test mode                                                                                                                | 472 |

| 3.8. Software initialization                                                                                                  | 476 |

| 4. CAN Registers                                                                                                              | 477 |

| 4.1. CAN register functions                                                                                                   |     |

| 4.2. Total control registers                                                                                                  |     |

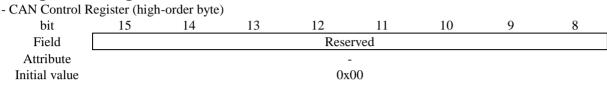

| 4.2.1. CAN Control Register (CTRLR)                                                                                           |     |

| 4.2.2. CAN Status Register (STATR)                                                                                            |     |

| 4.2.3. CAN Error Counter (ERRCNT)                                                                                             | 488 |

| 4.2.4. CAN Bit Timing Register (BTR)                                                                                          | 489 |

| 4.2.5. CAN Interrupt Register (INTR)                                                                                          |     |

| 4.2.6. CAN Test Register (TESTR)                                                                                              |     |

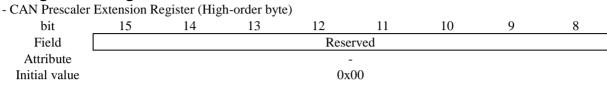

| 4.2.7. CAN Prescaler Extension Register (BRPER)                                                                               |     |

| 4.3. Message interface registers                                                                                              |     |

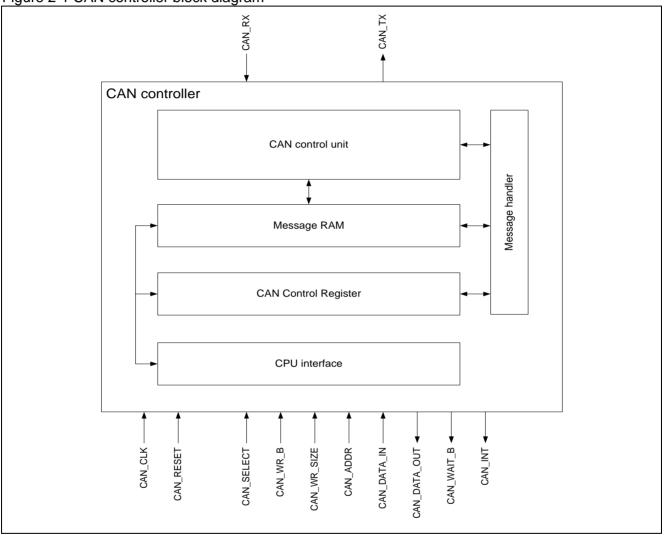

| 4.3.1. IFx Command Request Register (IFxCREQ)                                                                                 |     |

| 4.3.2. IFx Command Mask Register (IFxCMSK)                                                                                    |     |

| 4.3.3. IFx Mask Registers 1, 2 (IFxMSK1, IFxMSK2)                                                                             |     |

| 4.3.4. IFx Arbitration Registers 1, 2 (IFxARB1, IFxARB2)                                                                      |     |

| 4.3.5. IFx Message Control Register (IFxMCTR)<br>4.3.6. IFx Data Registers A1, A2, B1, and B2 (IFxDTA1, IFxDTA2, IFxDTB1, and | 504 |

| IFxDTBŽ)                                                                                                                      | 505 |

| 4.4. Message objects                                                                                                          | 506 |

| 4.5. Message handler registers                                                                                                |     |

| 4.5.1. CAN Transmit Request Registers 1, 2 (TREQR1, TREQR2)                                                                   |     |

| 4.5.2. CAN New Data Registers 1, 2 (NEWDT1, NEWDT2)                                                                           |     |

| 4.5.3. CAN Interrupt Pending Registers 1, 2 (INTPND1, INTPND2)                                                                |     |

| 4.5.4. CAN Message Valid Registers 1, 2 (MSGVAL1, MSGVAL2)                                                                    | 519 |

| 5. Notes                                                                                                                      | 520 |

| CHAPTER 6-1: HDMI-CEC/Remote Control Reception                                                                                | 521 |

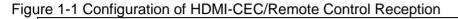

| 1. Configuration                                                                                                              | 522 |

| 2. Revision                                                                                                                   | 523 |

| 3. Usage Notes of HDMI-CEC                                                                                                    | 525 |

#### Contents

| CHAPTER 6-2: CEC Reception/Remote Reception                                                              | 527 |

|----------------------------------------------------------------------------------------------------------|-----|

| 1. Overview                                                                                              | 528 |

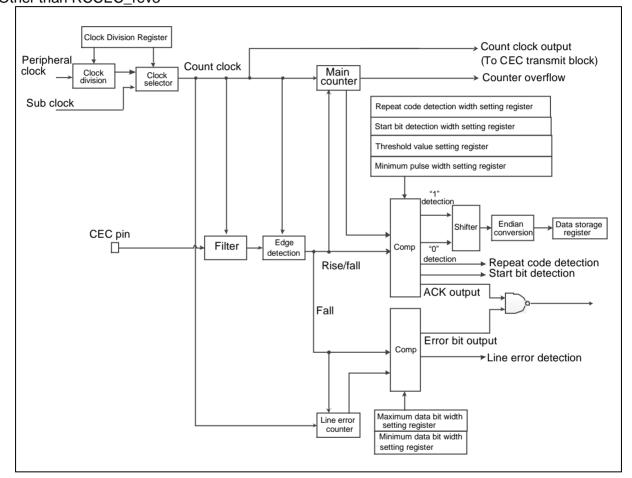

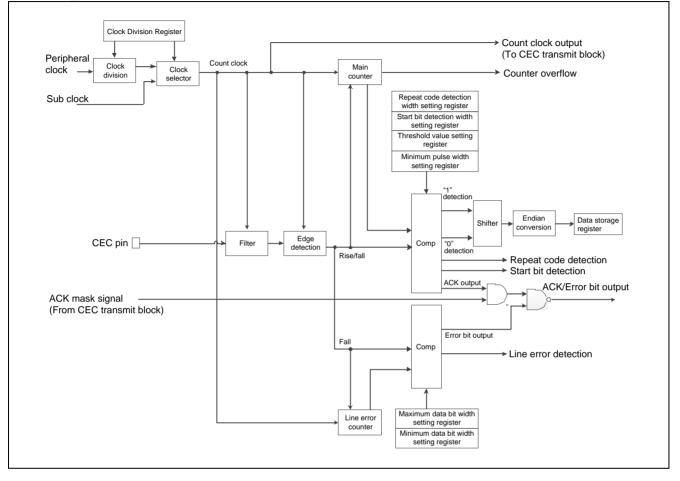

| 2. Configuration                                                                                         | 529 |

| 3. Operations                                                                                            | 531 |

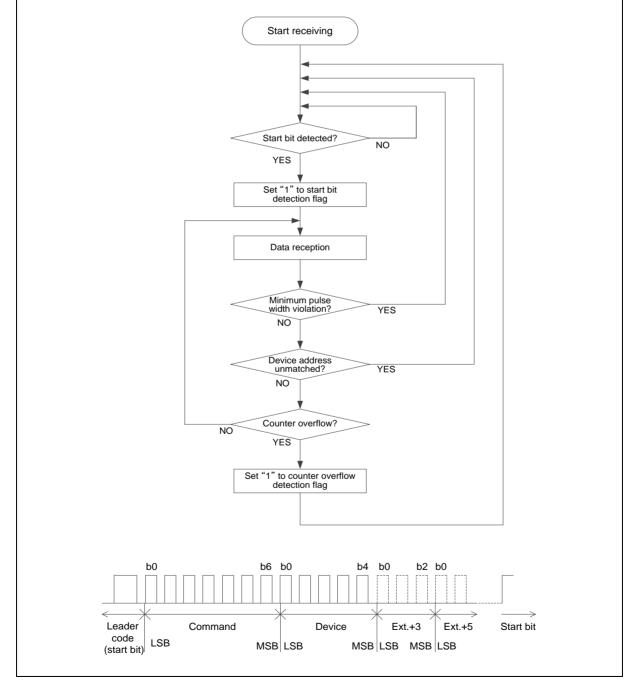

| 3.1 SIRCS mode                                                                                           | 531 |

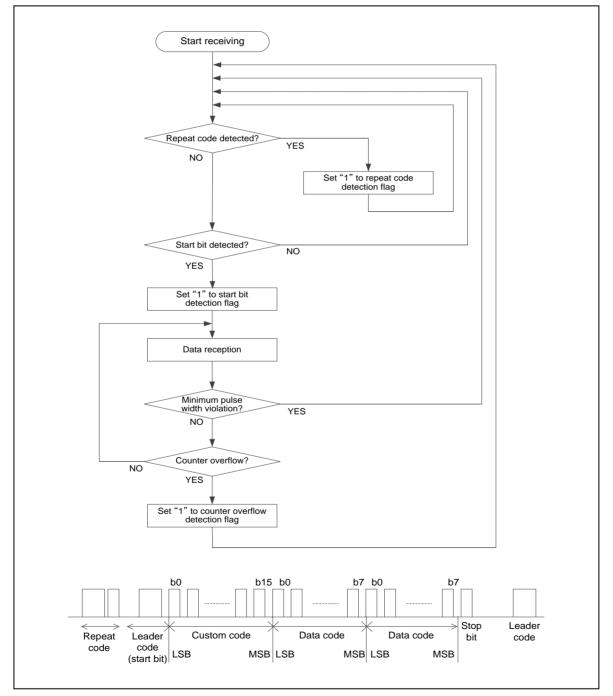

| 3.1.1. Operational flow chart and waves of SIRCS mode                                                    | 531 |

| 3.1.2. Basic operations of SIRCS mode                                                                    | 532 |

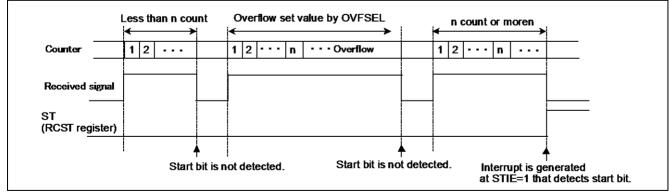

| 3.1.3. Start bit detection and interrupt output                                                          | 532 |

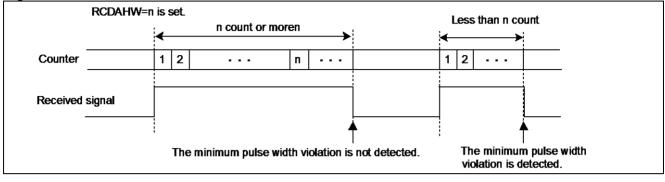

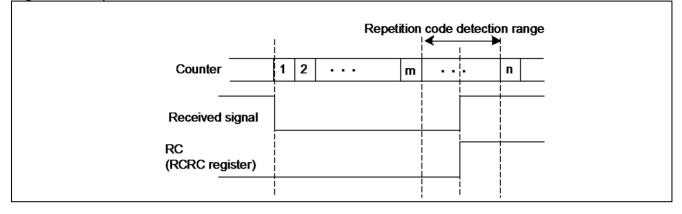

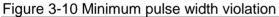

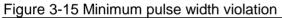

| 3.1.4. Minimum pulse width violation                                                                     | 533 |

| 3.1.5. Device address comparison                                                                         | 533 |

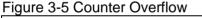

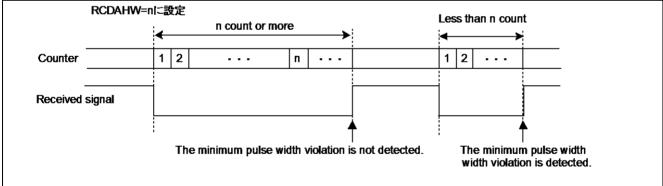

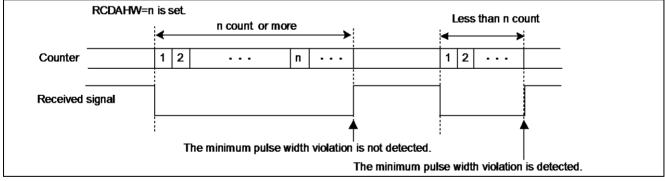

| 3.1.6. Counter overflow detection and interrupt output                                                   | 533 |

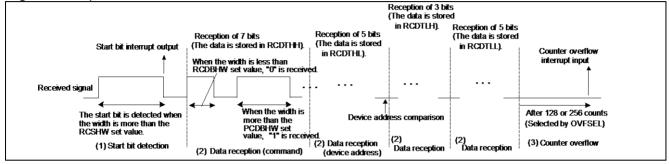

| 3.2. Operations of NEC/Association for Electric Home Appliances mode                                     | 534 |

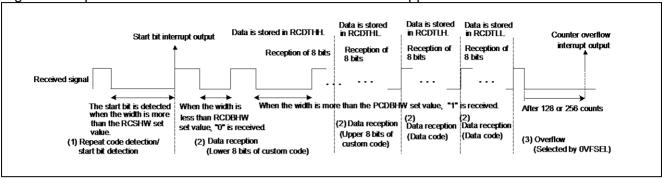

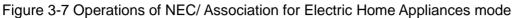

| 3.2.1. Operational flow chart and waves of NEC/Association for Electric Home<br>Appliances mode          | 534 |

| 3.2.2. Start bit detection                                                                               | 535 |

| 3.2.3. Repeat code detection                                                                             | 536 |

| 3.2.4. Minimum pulse width violation                                                                     | 536 |

| 3.2.5. Counter overflow detection and interrupt output                                                   | 537 |

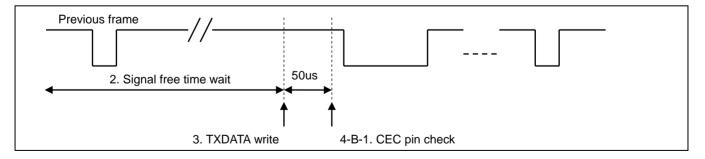

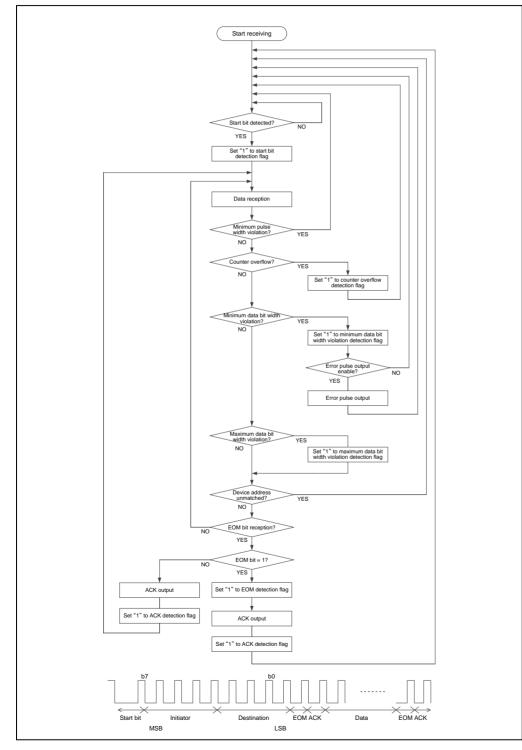

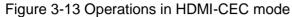

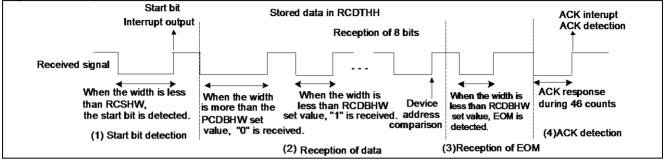

| 3.3. HDMI-CEC mode                                                                                       |     |

| 3.3.1. Operational flow chart and waves in HDMI-CEC mode                                                 | 538 |

| 3.3.2. Start bit detection and interrupt output                                                          |     |

| 3.3.3. Minimum pulse width violation                                                                     |     |

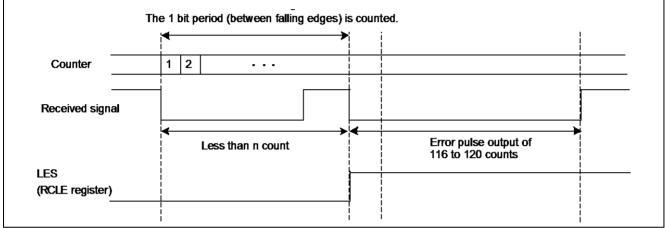

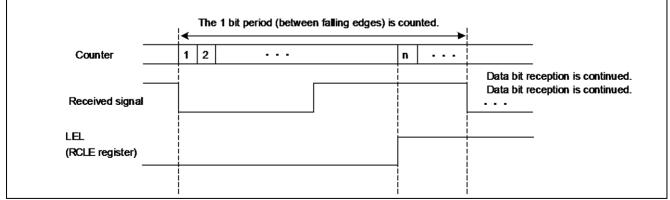

| 3.3.4. Counter overflow detection and interrupt output                                                   | 541 |

| 3.3.5. Device address comparison                                                                         | 542 |

| 3.3.6. Data bit width violation and error pulse automatic output                                         |     |

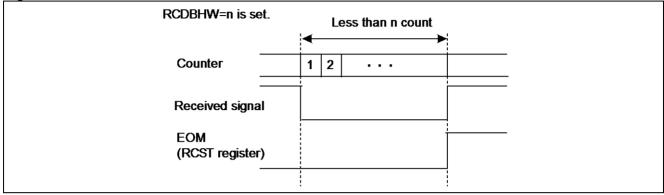

| 3.3.7. EOM detection                                                                                     | 543 |

| 3.3.8. ACK detection and interrupt output                                                                |     |

| 3.4. Noise filter                                                                                        | 544 |

| 4. Example of Setting                                                                                    | 545 |

| 5. Registers                                                                                             |     |

| 5.1. Reception Control Register (RCCR)                                                                   |     |

| 5.2. Reception Interrupt Control Register (RCST)                                                         |     |

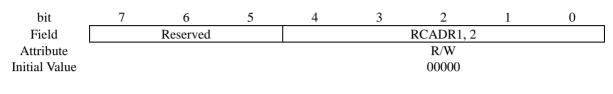

| 5.3. Device Address Setting Register 1, 2 (RCADR1, RCADR2)                                               |     |

| 5.4. Start Bit Detection Width Setting Register (RCSHW)                                                  |     |

| 5.5. Minimum Pulse Width Setting Register A (RCDAHW)<br>5.6. Threshold Value Setting Register B (RCDBHW) |     |

| 5.7. Data Save Register (RCDTHH, RCDTHL, RCDTLH, RCDTLL)                                                 |     |

| 5.8. Clock Division Setting Register (RCCKD)                                                             |     |

| 5.9. Repeat Code Interrupt Control Register (RCRC)                                                       |     |

| 5.10. Repeat Code Detection Width Setting Register (RCRHW)                                               |     |

| 5.11. Data Bit Width Violation Control Register (RCLE)                                                   |     |

| 5.12. Maximum Data Bit Width Setting Register (RCLELW)                                                   |     |

| 5.13. Minimum Data Bit Width Setting Register (RCLESW)                                                   | 563 |

CYPRESS

| CHAPTER 6-3: CEC Transmission                                                                                                                                                                                                                                          |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1. Overview of CEC Transmission                                                                                                                                                                                                                                        |     |

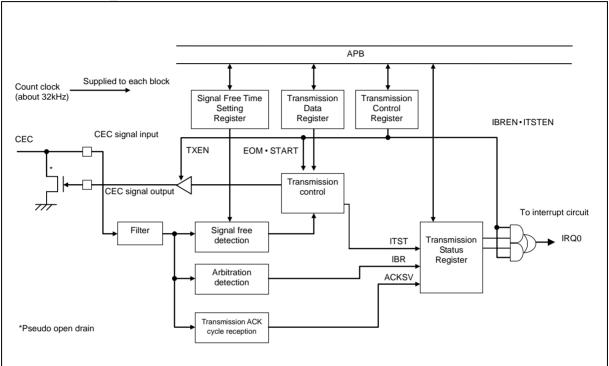

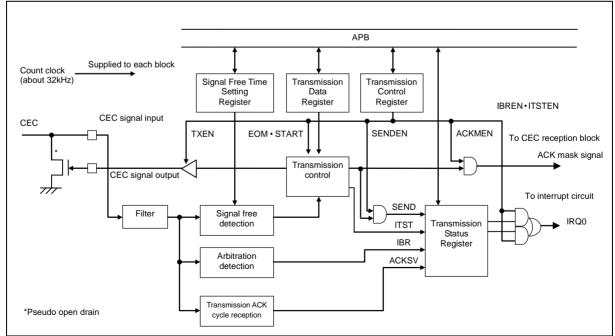

| 2. Block Diagram of CEC Transmitting Circuit                                                                                                                                                                                                                           |     |

| 3. CEC Transmission Interrupts                                                                                                                                                                                                                                         |     |

| 4. CEC Transmission Registers                                                                                                                                                                                                                                          |     |

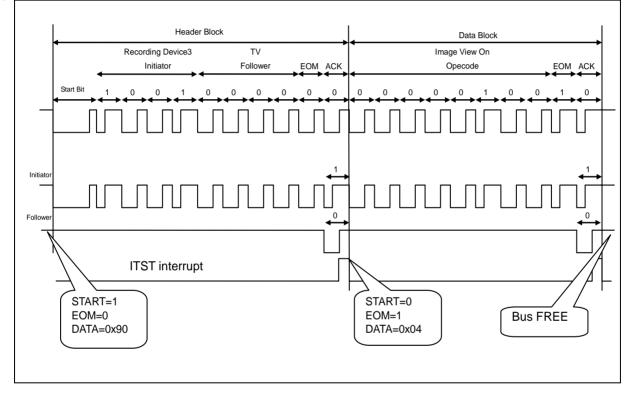

| <ol> <li>5. CEC Transmission Operations</li> <li>5.1. CEC Transmission Operations</li> <li>5.2. Interrupt Factors and Timing Chart</li> </ol>                                                                                                                          | 571 |

| 5.3. Arbitration Lost Detection                                                                                                                                                                                                                                        |     |

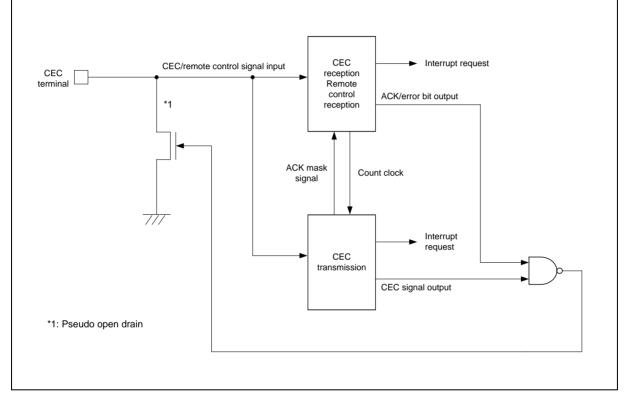

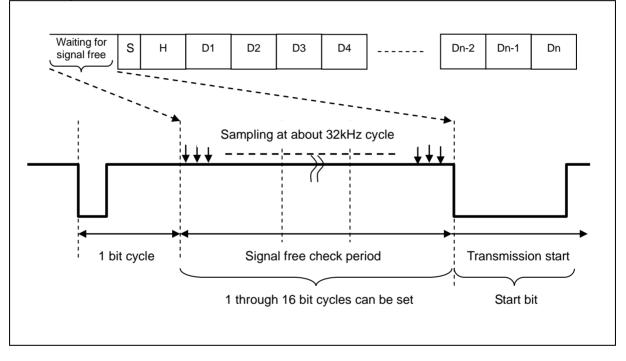

| 5.4. Signal Free Detection                                                                                                                                                                                                                                             |     |

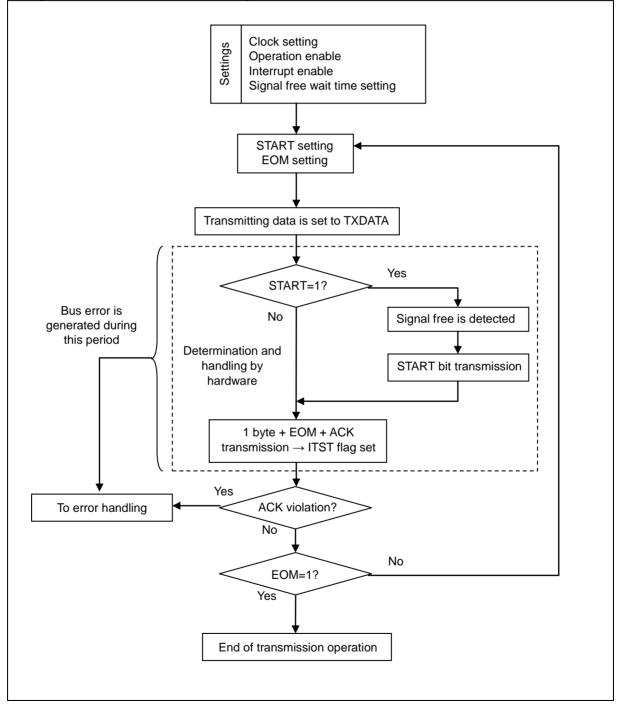

| 5.5. Filtering<br>5.6. CEC Transmission Operations Flow                                                                                                                                                                                                                |     |

| <ol> <li>6. CEC Transmission Register Set</li> <li>6.1. Transmission Control Register (TXCTRL)</li> <li>6.2. Transmission Data Register (TXDATA)</li> <li>6.3. Transmission Status Register (TXSTS)</li> <li>6.4. Signal Free Time Setting Register (SFREE)</li> </ol> |     |

| Appendixes                                                                                                                                                                                                                                                             |     |

| A Register Map<br>1. Register Map                                                                                                                                                                                                                                      |     |

| <ul><li>B List of Notes</li><li>1. Notes when high-speed CR is used for the master clock</li></ul>                                                                                                                                                                     |     |

| <ul> <li>C List of Limitations</li> <li>1. List of Limitations for TYPE0 Products</li> <li>2. List of Limitations for TYPE1 Products</li> </ul>                                                                                                                        | 654 |

| D Product TYPE List<br>1. Product TYPE List                                                                                                                                                                                                                            |     |

| Major Changes                                                                                                                                                                                                                                                          | 665 |

| Revision History                                                                                                                                                                                                                                                       |     |

# **CHAPTER 1-1: Multi-function Serial Interface**

This chapter describes the overview of the multi-function serial interface.

1. Overview of the Multi-function Serial Interface

CODE: 9BFMFS-E02.0

### 1. Overview of the Multi-function Serial Interface

This multi-function serial interface has the following characteristics.

#### Interface Mode

The following interface modes are selectable for the multi-function serial interface depending on the operation mode settings.

- · UART0 (Asynchronous normal serial interface)

- UART1 (Asynchronous multi-processor serial interface)

- · CSIO (Clock synchronous serial interface) (SPI can be supported)

- · LIN(LIN bus interface)

- ·  $I^2C$  ( $I^2C$  bus interface)

#### <Note>

See explanations of "UART (Asynchronous normal serial interface), "CSIO (Clock synchronous serial interface)", "LIN(LIN bus interface)", and "I<sup>2</sup>C (I<sup>2</sup>C bus interface)" chapters for details about each interface.

#### Switching the Interface Mode

To communicate through each serial interface, the serial mode register (SMR) shown in Table 1-1 should be used to set the operation mode before starting the communication.

| MD2                         | MD1 | MD0      | Interface mode                                                       |  |  |

|-----------------------------|-----|----------|----------------------------------------------------------------------|--|--|

| 0                           | 0   | 0        | UART0 (Asynchronous normal serial interface)                         |  |  |

| 0                           | 0   | 1        | UART1 (Asynchronous multi-processor serial interface)                |  |  |

| 0                           | 1   | 0        | CSIO (Clock synchronization serial interface) (SPI can be supported) |  |  |

| 0                           | 1   | 1        | LIN(LIN bus interface)                                               |  |  |

| 1                           | 0   | 0        | I <sup>2</sup> C (I <sup>2</sup> C bus interface)                    |  |  |

| Values other than the above |     | he above | Setting is prohibited.                                               |  |  |

#### Table 1-1 Switching Interface Mode

#### <Notes>

- Transmission and reception cannot be guaranteed when the operation mode is switched while one of the serial interfaces is still in use for transmission or reception operation.

- To switch the current operation mode, issue a programmable clear (SCR:UPCL=1) or disable the I<sup>2</sup>C (ISMK:EN=0), and switch the operation mode continuously. After the operation mode is set, set each register.

- $\cdot~$  The settings not listed in Table 1-1 are prohibited.

#### Transmission/Reception FIFO

This function has a  $16 \times 9$  bits transmission FIFO and  $16 \times 9$  bits reception FIFO. The FIFO steps should be converted to  $16 \times 9$  bits when reading through this text.

#### ■ LIN Sync field Detection: LSYN

If you are to use an ICU in the LIN bus interface mode, use the ICU of the multifunction timer. For switching an input to an ICU, see the section for Extended Function Pin Setting Register in the chapter "I/O PORT" in "Peripheral Manual".

#### ■ I<sup>2</sup>C Auxiliary Noise Filter

If the APB2 bus clock frequency exceeds 40 MHz when using the  $I^2C$  bus interface, use an auxiliary noise filter.  $I^2C$  standard input noise to a maximum of 50 ns is cut off.

For details, see the chapter "I<sup>2</sup>C Auxiliary Noise Filter".

The I<sup>2</sup>C auxiliary noise filter is built into only the product with the APB1 bus clock whose maximum frequency is 40 MHz or more.

#### <Notes>

- Since the maximum frequency of the APB1 bus clock varies depending on the product TYPE, refer to the internal operation clock frequency (FCP1) of the "Data Sheet" of products used.

- When the I<sup>2</sup>C auxiliary noise filter is used, the calculation formula of the reload value that should be set to the Baud rate generator registers (BGR1, BGR0) is different. See chapter "I<sup>2</sup>C Auxiliary Noise Filter" for the calculation formula of reload value when using the I<sup>2</sup>C auxiliary noise filter.

#### Extended I<sup>2</sup>C Bus Control Register (EIBCR)

TYPE6 products and later equip the extended  $I^2C$  bus control register (EIBCR). This register controls the following features. For details, see the chapter " $I^2C$  Interface ( $I^2C$  Communication Control Interface)".

- · Output control of SDA/SCL

- · Continuity/non-continuity of I<sup>2</sup>C operation after a bus error occurs

#### <Note>

Because TYPE0 to TYPE5 products do not equip the EIBCR register, read the following explanation as EIBCR:BEC=0.

## CHAPTER 1-2: UART (Asynchronous Serial Interface)

This chapter explains the UART (asynchronous serial interface) function supported in operation mode 0 and 1 of the multifunction serial interface.

- 1. Overview of UART (Asynchronous Serial Interface)

- 2. UART Interrupt

- 3. UART Operation

- 4. Dedicated Baud Rate Generator

- 5. Setting Procedure and Program Flow in Operation Mode 0 (Asynchronous Normal Mode)

- 6. Setting Procedure and Program Flow in Operation Mode 1 (Asynchronous Multiprocessor Mode)

- 7. UART (Asynchronous Serial Interface) Registers

### 1. Overview of UART (Asynchronous Serial Interface)

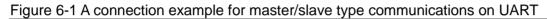

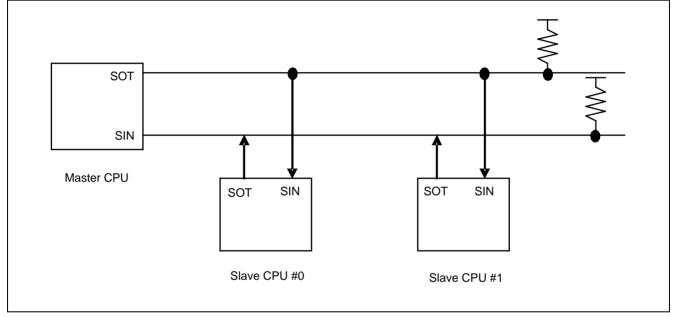

UART (asynchronous serial interface) is a general-purpose serial data communications interface for asynchronous communications (start/stop synchronization) with external devices. It supports a bi-directional communications function (normal mode) and a master/slave type communications function (multi-processor mode: both master and slave modes supported). It also has transmit /received FIFO installed.

#### Function • Full duplex double buffer (when FIFO is not used) 1 Data . Transmit /received FIFO (size: max $128 \times 9$ bits each)<sup>\*1</sup> (when FIFO is used) Run oversampling three times with the bus clock and determine the value of 2 Serial input received data based on the majority sampling value. 3 Transfer system Asynchronous A dedicated baud rate generator (constructed with a 15-bit reload counter) . 4 Baud rate The external clock input can be adjusted with the reload counter.

#### ■ Functions of UART (Asynchronous Serial Interface)

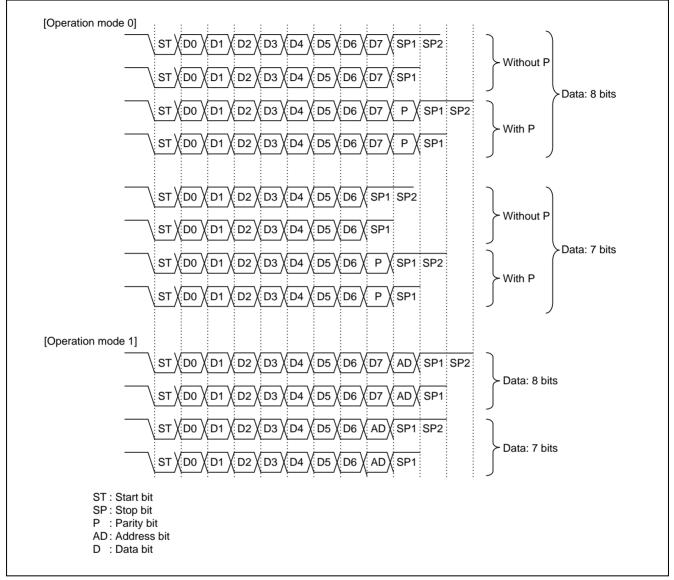

| 5  | Data length                                                    | · 5 to 9 bits (in normal mode)/7 bits or 8 bits (in multiprocessor mode)                                                                                                                                                                                                                                                                                                    |  |  |

|----|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

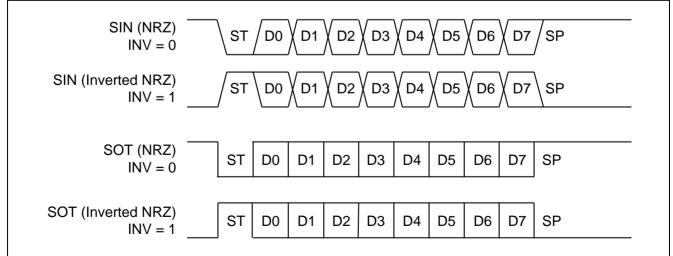

| 6  | Signaling system                                               | NRZ (Non Return to Zero), inverted NRZ                                                                                                                                                                                                                                                                                                                                      |  |  |

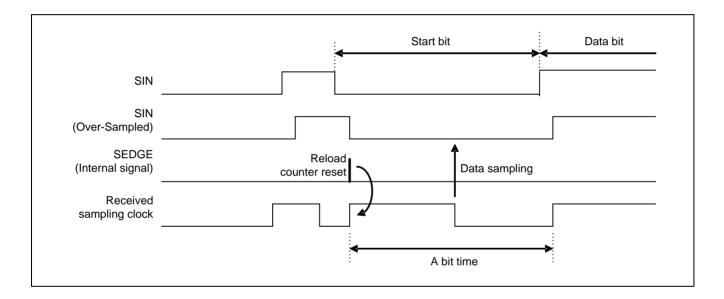

| 7  | Start bit detection                                            | <ul> <li>In synch with the falling edge of the start bit (in the NRZ system)</li> <li>In synch with the rising edge of the start bit (in the inverted NRZ system)</li> </ul>                                                                                                                                                                                                |  |  |

| 8  | Received error detection                                       | <ul> <li>Framing error</li> <li>Overrun error</li> <li>Parity error<sup>*2</sup></li> </ul>                                                                                                                                                                                                                                                                                 |  |  |

| 9  | Hardware flow control                                          | CTS/RTS-based automatic transmit /received control*3                                                                                                                                                                                                                                                                                                                        |  |  |

| 10 | Interrupt request                                              | <ul> <li>Received interrupt         <ul> <li>(upon reception completed, framing error, overrun error or parity error<sup>*2</sup>)</li> <li>Transmit interrupts (transmit data empty, transmit bus idle)</li> <li>Transmit FIFO interrupt (when transmit FIFO is empty)</li> <li>DMA(Transmit /Received) transferring support function is available.</li> </ul> </li> </ul> |  |  |

| 11 | Master/slave communications functions (in multiprocessor mode) | One (master)-to-n (slaves) communication is enabled.<br>(Both master and slave systems are supported.)                                                                                                                                                                                                                                                                      |  |  |

| 12 | FIFO options                                                   | <ul> <li>Transmit /received FIFO installed (maximum capacity: 128 × 9 bits for transmit FIFO, 128 bytes × 9 bits for received FIFO) *1</li> <li>Transmit FIFO or received FIFO can be selected.</li> <li>Transmit data can be resent.</li> <li>Received FIFO interrupt timing can be changed via software.</li> <li>FIFO resetting is supported independently.</li> </ul>   |  |  |

\*1: The FIFO capacity size varies depending on the product type.

\*2: Parity errors are only generated in normal mode.

\*3: The channel number, which the hardware flow control input/output (RTS/CTS) can be used, is dependent on the product type. See Data Sheet of the product used.

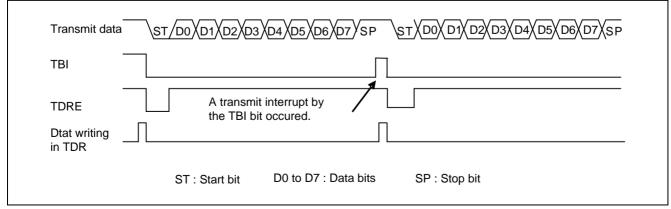

### 2. UART Interrupt

UART generates transmit or received interrupts. These interrupt requests can be generated if:

- Received data is set in the Received Data Register (RDR) or a data received error occurs.

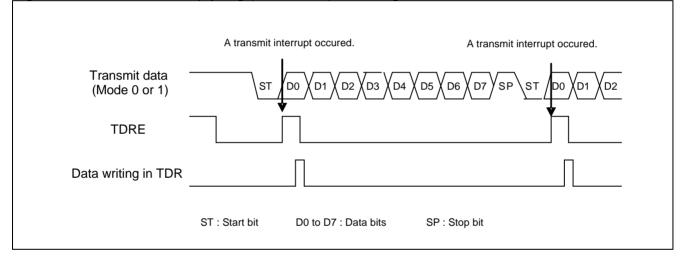

- Transmit data is transferred from the Transmit Data Register (TDR) to the transmit shift register and the data transmission is started.

- The transmit bus is idle (No data transmission occurs).

- Transmit FIFO data is requested.

#### ■ UART Interrupt

Table 2-1 shows the relationships between the UART interrupt control bits and the interrupt factors.

| Interrupt<br>type | Interrupt<br>request | Flag<br>register | Oper<br>mo |   | Interrupt factor                                                                                                                               | Interrupt<br>factor | Operation to clear<br>interrupt request flag                                                                                                                                                                                                                   |

|-------------------|----------------------|------------------|------------|---|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | flag bit             | rogiotor         | 0          | 1 |                                                                                                                                                | enable bit          |                                                                                                                                                                                                                                                                |

| Received          | RDRF                 | SSR              |            |   | A single-byte received                                                                                                                         | SCR:RIE             | Reading from the received data register (RDR)                                                                                                                                                                                                                  |

|                   |                      |                  | 0          | 0 | Received of a data volume<br>matching the value set for<br>FBYTE.                                                                              |                     | Reading from the Received Data Register<br>(RDR) until received FIFO is emptied                                                                                                                                                                                |

|                   |                      |                  | U          |   | While the FRIIE bit is "1"<br>and the received FIFO<br>contains valid data, a<br>received idle state continues<br>for 8 bits or longer period. |                     |                                                                                                                                                                                                                                                                |

|                   | ORE                  | SSR              | 0          | 0 | Overrun error                                                                                                                                  |                     |                                                                                                                                                                                                                                                                |

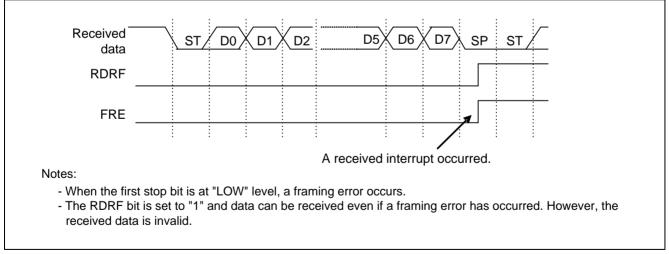

|                   | FRE                  | SSR              | 0          | 0 | Framing error                                                                                                                                  |                     | Setting the received error flag clear bit (SSR:REC) to "1"                                                                                                                                                                                                     |

|                   | PE                   | SSR              | 0          | х | Parity error                                                                                                                                   |                     |                                                                                                                                                                                                                                                                |

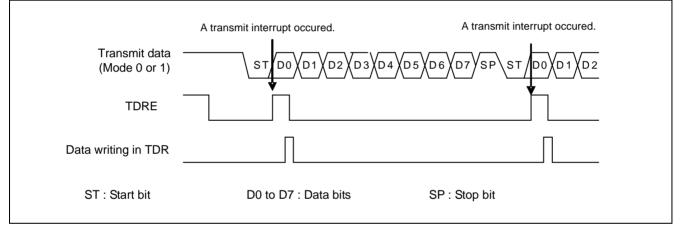

| Transmit          | TDRE                 | SSR              | 0          | 0 | The Transmit Data Register is empty                                                                                                            | SCR:TIE             | Writing to the Transmit Data Register<br>(TDR) or setting the transmit FIFO<br>operation enable bit to "1" when the<br>transmit FIFO operation enable bit is set<br>to "0" and valid data are present in<br>transmit FIFO (re-transmitting data) <sup>*1</sup> |

|                   | TBI                  | SSR              | 0          | 0 | No data transmission                                                                                                                           | SCR:TBIE            | Writing to the Transmit Data Register<br>(TDR) or setting the transmit FIFO<br>operation enable bit to "1" when the<br>transmit FIFO operation enable bit is set<br>to "0" and valid data are present in<br>transmit FIFO (re-transmitting data) <sup>*1</sup> |

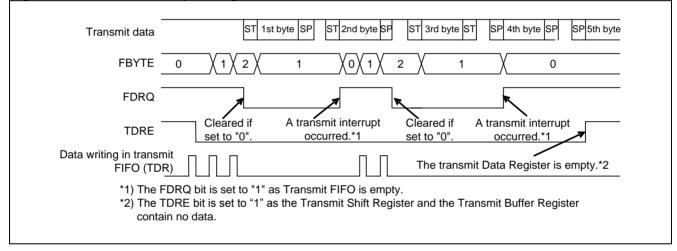

|                   | FDRQ                 | FCR1             | 0          | 0 | Transmit FIFO is empty.                                                                                                                        | FCR1:FTIE           | The FIFO transmit data request bit<br>(FCR1:FDRQ) is set to "0" or transmit<br>FIFO is full.                                                                                                                                                                   |

#### Table 2-1 UART interrupt control bits and interrupt factors

\*1: Set the TIE bit to "1" only after the TDRE bit has been set to "0".

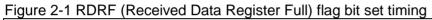

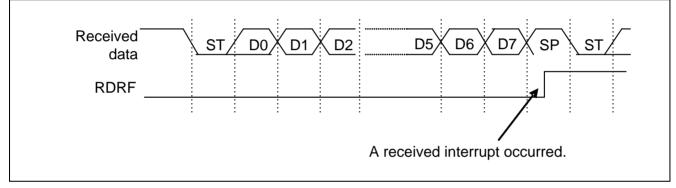

### 2.1. Received interrupt and flag set timing

Data reception can be interrupted by a Received Completion (SSR:RDRF=1) or a Received Error Occurrence (SSR:PE,ORE,FRE=1).

#### Received interrupt and flag set timing

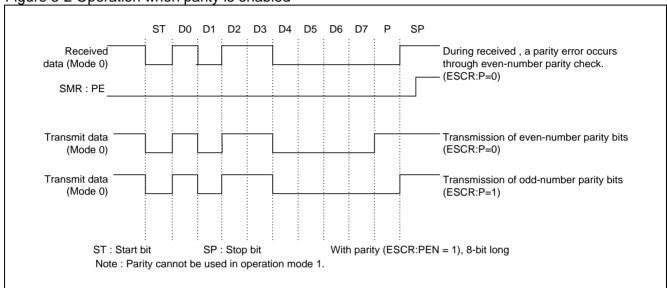

Upon detection of the first stop bit, received data are stored in the Received Data Register (RDR). When the data received is completed (SSR:RDRF=1) or when a data received error occurs (SSR:PE, ORE, FRE=1), each flag is set. If received interrupts are enabled (SSR:RIE=1) then, a received interrupt occurs.

#### <Note>

If a received error occurs, data in the Received Data Register (RDR) becomes invalid.

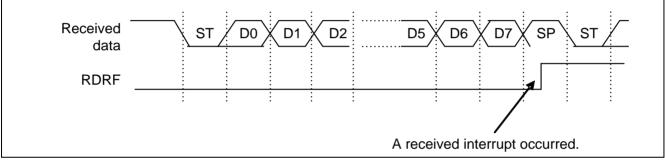

#### Figure 2-2 FRE (Framing Error) flag bit set timing

#### <Note>

During reception, if the following is detected at the same time as the stop bit sampling point or before the 1 to 2 bus clocks, the relevant edge becomes invalid, which may disable normal received of the next data. To output frames continuously, adequate intervals are required between frames.

- The falling edge of serial data (When ESCR:INV=0)

- The rising edge of serial data (When ESCR:INV=1)

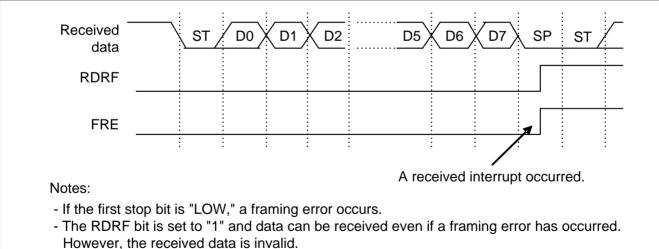

#### Figure 2-3 ORE (Overrun Error) flag bit set timing

| Received<br>data |                                                                                       |

|------------------|---------------------------------------------------------------------------------------|

| RDRF             |                                                                                       |

| ORE              |                                                                                       |

| Note:            |                                                                                       |

| If the next de   | ta is transferred before the received data is read (RDRF=1), an overrun error occurs. |

| ii the next ua   |                                                                                       |

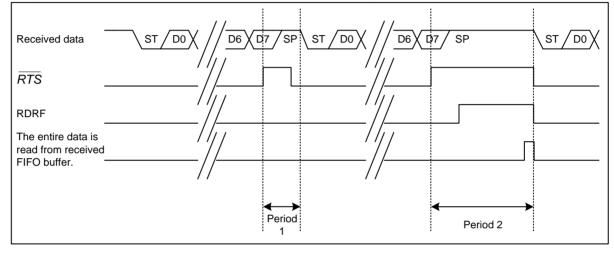

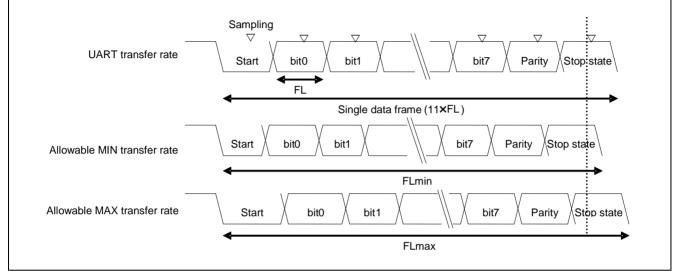

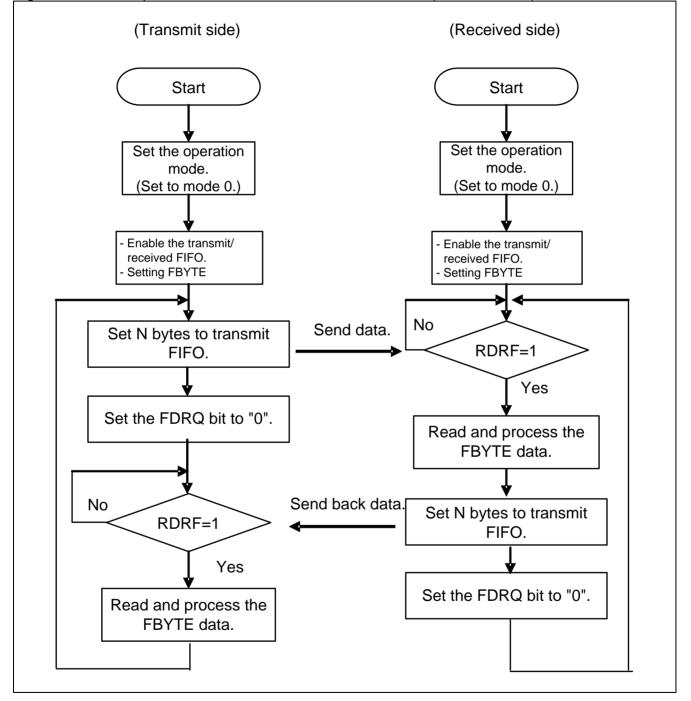

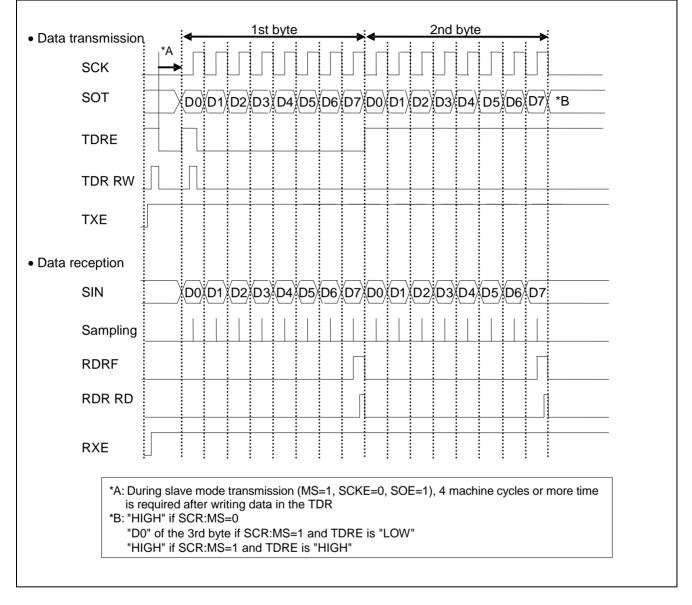

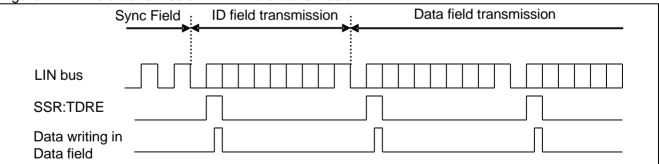

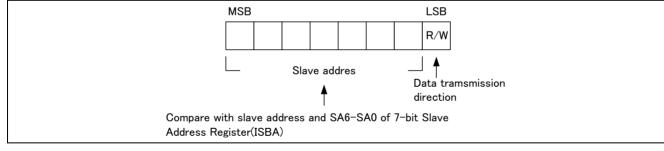

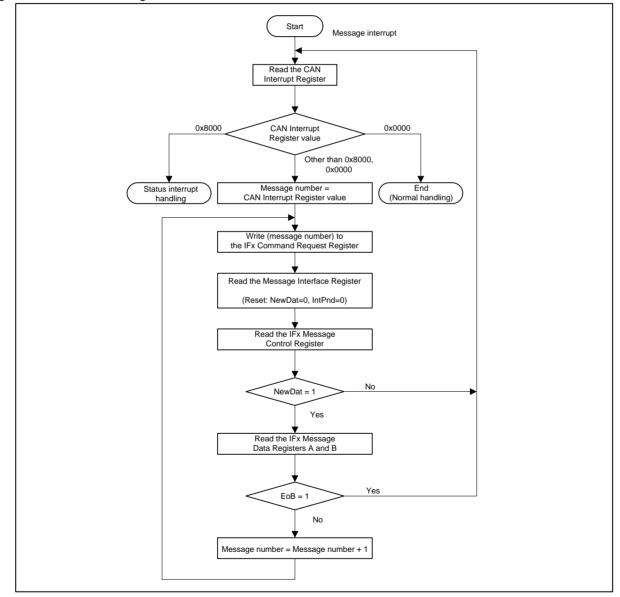

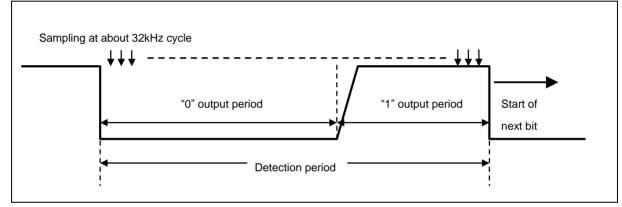

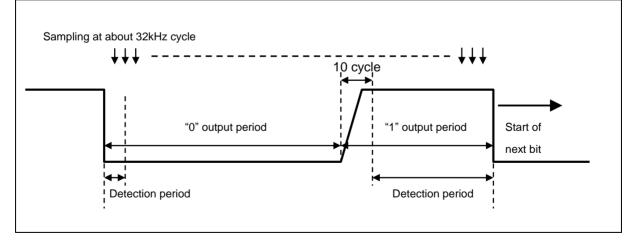

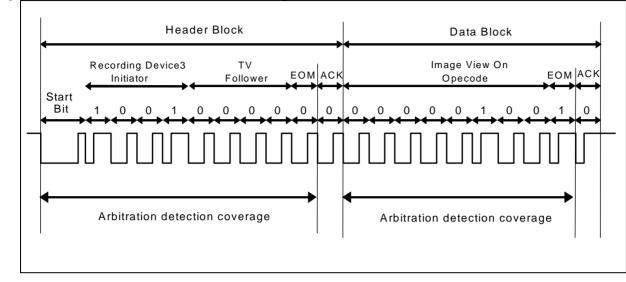

### 2.2. Interrupt and flag set timing when received FIFO is used