# AN4235 Application note

# I2C timing configuration tool for STM32F3xxxx and STM32F0xxxx microcontrollers

### Introduction

This application note presents the I2C timing configuration tool (STSW-STM32126) for the STM32F3xxxx and STM32F0xxxx microcontroller families.

The STM32F0xxxx and STM32F3xxxx devices embed an Inter-Integrated Circuit communication peripheral (I2C) supporting standard mode (100 KHz), fast mode (400 KHz) and fast mode plus (1 MHz). The I2C implements a new clock scheme allowing the peripheral to be used as a wake-up source from low-power mode on address match.

The purpose of this tool is to help the user configure the I2C timings, taking into consideration the I2C bus specification.

The configuration tool is implemented in the Microsoft Excel "12C\_Timing\_Config\_Tool\_Vx.y.z.x/s" file which can be downloaded from www.st.com.

For Vx.y.z, please refer to the tool version, for example: V1.0.0.

Before using the clock tool, it is essential to read the STM32 microcontroller reference manuals (RM0313 for STM32F37xxx products, RM0316 for STM32F30xxx products and RM0091 for STM32F0xxxx products). This application note is not a substitute for the reference manuals.

August 2013 DocID024161 Rev 2 1/18

Contents AN4235

# **Contents**

| 1 | Glos            | ssary     |                                       | 5  |  |  |  |  |  |  |  |

|---|-----------------|-----------|---------------------------------------|----|--|--|--|--|--|--|--|

| 2 | Getting started |           |                                       |    |  |  |  |  |  |  |  |

|   | 2.1             | Softwa    | are requirements                      | 6  |  |  |  |  |  |  |  |

|   | 2.2             | Hardw     | vare requirements                     | 7  |  |  |  |  |  |  |  |

|   |                 | 2.2.1     | Introduction                          | 7  |  |  |  |  |  |  |  |

|   |                 | 2.2.2     | I2C timing specification              | 7  |  |  |  |  |  |  |  |

|   |                 | 2.2.3     | I2C clock scheme                      | 9  |  |  |  |  |  |  |  |

|   |                 | 2.2.4     | I2C timing register                   | 10 |  |  |  |  |  |  |  |

| 3 | Tuto            | rials     |                                       | 13 |  |  |  |  |  |  |  |

| 4 | Con             | clusion   | · · · · · · · · · · · · · · · · · · · | 16 |  |  |  |  |  |  |  |

| 5 | Revi            | ision his | story                                 | 17 |  |  |  |  |  |  |  |

AN4235 List of tables

# List of tables

| Table 1. | Definition of terms                                                  | 5 |

|----------|----------------------------------------------------------------------|---|

| Table 2. | I2C timings specification (see I2C specification, rev.03, June 2007) | 8 |

| Table 3. | Timing register                                                      | 0 |

| Table 4. | Document revision history                                            | 7 |

List of figures AN4235

# List of figures

| Figure 1. | I2C bus timing (see I2C specification, rev.03, June 2007) | . 7 |

|-----------|-----------------------------------------------------------|-----|

| Figure 2. | I2C clock scheme                                          | . 9 |

| Figure 3. | Data setup time generation from SCLDEL                    | 10  |

| Figure 4. | Data hold time generation from SDADEL                     | 11  |

| Figure 5. | High and low period generation from SCLH and SCLL         | 11  |

| Figure 6. | I2C timing configuration tool user interface              | 13  |

| Figure 7. | Calculation is completed                                  | 14  |

| Figure 8. | Error message                                             | 15  |

| Figure 9. | Warning message                                           | 15  |

AN4235 Glossary

# 1 Glossary

Table 1. Definition of terms

| Term   | Description               |  |  |  |  |  |  |  |

|--------|---------------------------|--|--|--|--|--|--|--|

| AF     | Analog filter             |  |  |  |  |  |  |  |

| DNF    | Digital noise filter      |  |  |  |  |  |  |  |

| HSI    | High-speed internal clock |  |  |  |  |  |  |  |

| I2C    | Inter-Integrated Circuit  |  |  |  |  |  |  |  |

| I2CCLK | I2C kernel clock          |  |  |  |  |  |  |  |

| PCLK   | APBx clock                |  |  |  |  |  |  |  |

| PRESC  | Prescaler                 |  |  |  |  |  |  |  |

| SCL    | Serial clock line         |  |  |  |  |  |  |  |

| SDA    | Serial data line          |  |  |  |  |  |  |  |

| SYSCLK | System clock              |  |  |  |  |  |  |  |

## 2 Getting started

This section describes the requirements and procedures needed to start using the timing configuration tool.

## 2.1 Software requirements

To use the timing configuration tool with Windows operating system, a recent version of Windows, such as Windows XP, Vista or Windows 7, must be installed on the PC with at least 256 Mbytes of RAM.

Before starting to use the timing configuration tool, make sure that Microsoft Office is installed on your machine and then follow these steps:

- Download the latest version of the I2C timing configuration tool for the STM32 devices from www.st.com.

- Enable macros and ActiveX controls as shown below:

#### **Excel 1997-2003 version**

- Click **Tools** in the menu bar.

- 2. Click Macro.

- Click Security.

- 4. Click Low (not recommended).

Note:

If ActiveX controls are not enabled, a warning message is displayed asking you to enable ActiveX. In this case, you should click "OK" to enable it.

#### Excel 2007-2010 version

- 1. Click the Microsoft Office button and then click Excel options.

- Click Trust Center, click Trust center settings, and then click Macro settings.

- 3. Click Enable all macros (not recommended, potentially dangerous code can run).

- 4. Click Trust Center, click Trust center settings, and then click ActiveX settings.

- 5. Click Enable all controls without restrictions and without prompting (not recommended; potentiality dangerous controls can run).

- 6. Click OK.

Note:

For more information about how to enable macros and ActiveX controls, refer to the Microsoft Office website.

AN4235 Getting started

## 2.2 Hardware requirements

### 2.2.1 Introduction

The I2C timing configuration tool is designed to help the end-user easily configure the timing settings for the I2C peripheral and guarantee its operation as specified in the I2C timing specification.

## 2.2.2 I2C timing specification

The I2C timings should be configured with values that are compliant with the I2C bus specification:

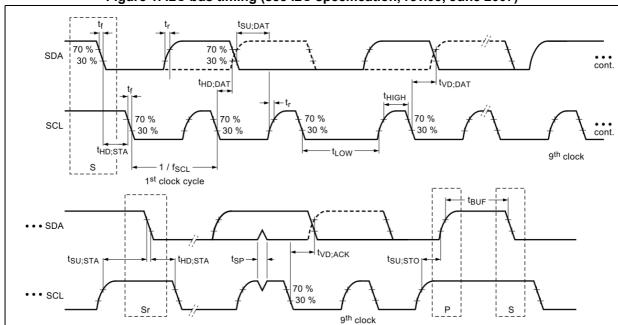

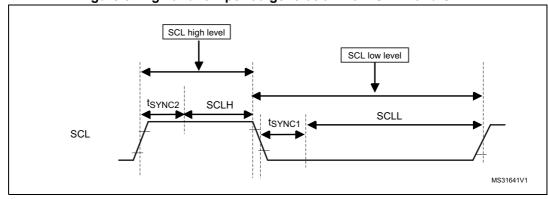

Figure 1. I2C bus timing (see I2C specification, rev.03, June 2007)

The table below shows the value range of these timings:

Table 2. I2C timings specification (see I2C specification, rev.03, June 2007)

| Symbol              | Danier de la                                     | Sta | ndard               | Fast                         | node               | Fastı |                     |      |

|---------------------|--------------------------------------------------|-----|---------------------|------------------------------|--------------------|-------|---------------------|------|

|                     | Parameter                                        | Min | Max                 | Max Min                      |                    | Min   | Max                 | Unit |

| f <sub>SCL</sub>    | SCL clock frequency                              | 0   | 100                 | 0                            | 400                | 0     | 1000                | KHz  |

| t <sub>LOW</sub>    | Low period of the SCL clock                      | 4.7 | -                   | 1.3                          | -                  | 0.5   | -                   | μs   |

| t <sub>HIGH</sub>   | High Period of the SCL clock                     | 4   |                     | 0.6                          |                    | 0.26  | -                   | μs   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals            | -   | 1000                | 20 +<br>0.1Cb <sup>(1)</sup> | 300                | -     | 120                 | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals            | -   | 300                 | 20 +<br>0.1Cb <sup>(1)</sup> | 300                | -     | 120                 | ns   |

| t <sub>HD;DAT</sub> | Data hold time                                   | 0   | -                   | 0                            | -                  | 0     | -                   | μs   |

| t <sub>VD;DAT</sub> | Data valid time                                  | -   | 3.45 <sup>(2)</sup> | -                            | 0.9 <sup>(2)</sup> | -     | 0.45 <sup>(2)</sup> | μs   |

| t <sub>VD;ACK</sub> | Data valid acknowledge time                      | -   | 3.45 <sup>(2)</sup> | -                            | 0.9 <sup>(2)</sup> | -     | 0.45 <sup>(2)</sup> | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                  | 250 | -                   | 100                          | -                  | 50    | -                   | ns   |

| t <sub>HD:STA</sub> | Hold time (repeated) START condition             | 4.0 | -                   | 0.6                          | -                  | 0.26  | -                   | μs   |

| <sup>t</sup> su:sta | Set-up time for a repeated START condition       | 4.7 | -                   | 0.6                          | -                  | 0.26  |                     | μs   |

| t <sub>SU:STO</sub> | Set-up time for STOP condition                   | 4.0 | -                   | 0.6                          | -                  | 0.26  | -                   | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 4.7 | -                   | 1.3                          | -                  | 0.5   | -                   | μs   |

<sup>1.</sup> Cb = total capacitance of one bus line in pF.

The maximum t<sub>HD;DAT</sub> could be 3.45 μs, 0.9 μs and 0.45 μs for standard mode, fast mode and fast mode plus, but must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time. This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

AN4235 Getting started

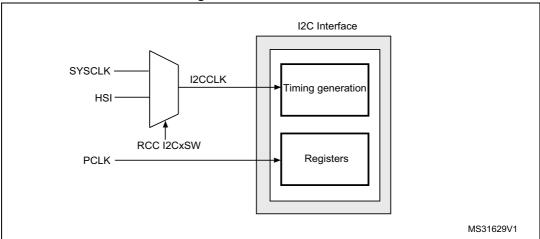

#### 2.2.3 I2C clock scheme

The I2C kernel is clocked by an independent clock source. The clock source can be:

- HSI (default source)

- SYSCLK

Figure 2. I2C clock scheme

These two clocks allow I2C to operate independently from the PCLK frequency.

Setting HSI as I2C clock source frequency allows the use of wake-up from STOP mode capability at address match.

The I2CCLK period t<sub>I2CCLK</sub> must respect the following conditions:

$t_{I2CCLK} < (t_{LOW} - t_{filters}) / 4$  and  $t_{I2CCLK} < t_{HIGH}$

$t_{\mbox{\scriptsize filters}}\!\!:$  when enabled, sum of the delays brought by the analog filter and the digital filter.

Analog filter delay is maximum 260 ns and digital filter delay is DNF x t<sub>I2CCLK</sub>.

The PCLK clock period t<sub>PCLK</sub> must respect the following condition:

$$t_{PCLK} < 4/3 t_{SCL}$$

Please refer to the RCC section in STM32 product reference manual for more details about the selection of the I2C clock source.

### 2.2.4 I2C timing register

The I2C timing register is defined as the following table shows:

Table 3. Timing register

| 31                             | 30        | 29 | 28 | 27 | 26 | 25 | 24          | 23 | 22        | 21 | 20          | 19 | 18 | 17 | 16 |

|--------------------------------|-----------|----|----|----|----|----|-------------|----|-----------|----|-------------|----|----|----|----|

| PRESC[3:0] Res. Res. Res. Res. |           |    |    |    |    |    | SCLDEL[3:0] |    |           |    | SDADEL[3:0] |    |    |    |    |

|                                | rw        |    |    |    |    |    | rw          |    |           |    | rw          |    |    |    |    |

| 15                             | 14        | 13 | 12 | 11 | 10 | 9  | 8           | 7  | 6         | 5  | 4           | 3  | 2  | 1  | 0  |

|                                | SCLH[7:0] |    |    |    |    |    |             |    | SCLL[7:0] |    |             |    |    |    |    |

| rw                             |           |    |    |    |    |    |             | rw |           |    |             |    |    |    |    |

|                                |           |    |    |    |    |    |             |    |           |    |             |    |    |    |    |

PRESC[3:0] is used to prescale I2C clock source (I2CCLK); it allows the generation of a divided clock. The period of this divided clock t<sub>PRESC</sub> is defined by:

$t_{PRESC}$  = (PRESC+1) x  $t_{I2CCLK}$

The time unit t<sub>PRESC</sub> is used for the generation of other I2C timings.

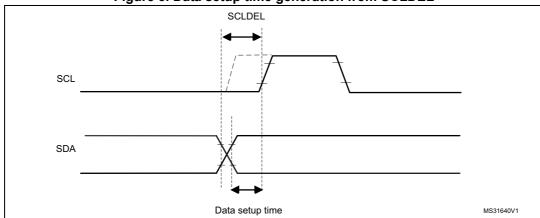

SCLDEL[3:0] is used to program the data setup time ( $t_{SU;DAT}$ ) as shown in the following figure:

Figure 3. Data setup time generation from SCLDEL

SCLDEL is defined as follows:

$\{[t_r + t_{SU;DAT(min)}] / [t_{PRESC}]\} - 1 \le SCLDEL$

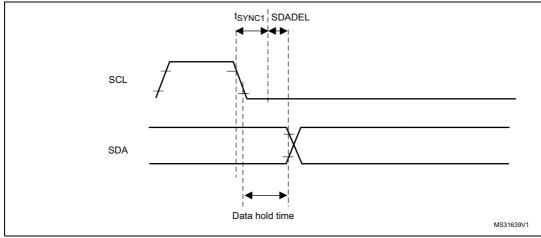

SDADEL[3:0] is used to program the data hold time  $(t_{\text{HD;DAT}})$  as shown in the following figure:

AN4235 Getting started

Figure 4. Data hold time generation from SDADEL

$t_{\mbox{\scriptsize SYNC1}}$  duration depends on these parameters:

- SCL falling time

- When enabled, input delay brought by the analog filter: 0.05  $\mu s < t_{AF} < 0.26 \ \mu s$

- When enabled, input delay brought by the digital filter: t<sub>DNF</sub> = DNF x t<sub>I2CCLK</sub>

- Delay due to SCL synchronization to I2CCLK clock (2 to 3 I2CCLK periods)

SDADEL is defined by:

$$\begin{split} & \text{SDADEL} >= \{t_{\text{f}} + t_{\text{HD;DAT(min)}} - t_{\text{AF(min)}} - t_{\text{DNF}} - [3 \times t_{\text{I2CCLK}}]\} \ / \ \{t_{\text{PRESC}}\} \\ & \text{SDADEL} <= \{t_{\text{VD;DAT(max)}} - t_{\text{r}} - t_{\text{AF(max)}} - t_{\text{DNF}} - [4 \times t_{\text{I2CCLK}}]\} \ / \ \{t_{\text{PRESC}}\} \end{split}$$

SCLH[7:0] and SCLL[7:0] are used to configure I2C speed frequency when master mode is selected. SCLH generates the high period of the SCL clock ( $t_{HIGH}$ ) and SCLL generates the low period of the SCL clock ( $t_{LOW}$ ). The figure below shows how these timings are deduced:

Figure 5. High and low period generation from SCLH and SCLL

$\ensuremath{t_{SYNC2}}$  duration depends on these parameters:

- SCL rising time

- When enabled, input delay brought by the analog filter: 0.05  $\mu$ s <  $t_{AF}$  < 0.26  $\mu$ s

- When enabled, input delay brought by the digital filter:  $t_{DNF}$  = DNF x  $t_{I2CCLK}$

- Delay due to SCL synchronization to I2CCLK clock (2 to 3 I2CCLK periods)

SCL clock period ( $t_{SCL}$ ) which defines I2C speed frequency ( $f_{SCL}$ = 1/ $t_{SCL}$ ) is defined by:

$$t_{SCL} = t_f + t_{LOW} + t_r + t_{HIGH}$$

SCLH and SCLL are defined as follows:

$$\begin{split} t_{\text{HIGH(min)}} <= t_{\text{AF(min)}} + t_{\text{DNF}} + 2 & \text{x } t_{\text{I2CCLK}} + \text{[(SCLH+1) x } t_{\text{PRESC}}\text{]} \\ t_{\text{LOW(min)}} <= t_{\text{AF(min)}} + t_{\text{DNF}} + 2 & \text{x } t_{\text{I2CCLK}} + \text{[(SCLL+1) x } t_{\text{PRESC}}\text{]} \end{split}$$

Note: SCLH and SCLL values depend on the rise and fall time.

The rise time is defined by:

$t_r = R_p \times C_b \times 0.8473$  ( $R_p$  is the pull\_up resistor and  $C_b$  is the bus capacitance)

The fall time depends on the software configuration of the I/O. Please refer to "I/O AC characteristics" table in STM32 products datasheets to get the value of fall time.