# Advance Information Dual CVSD/PLL Cordless Phone System

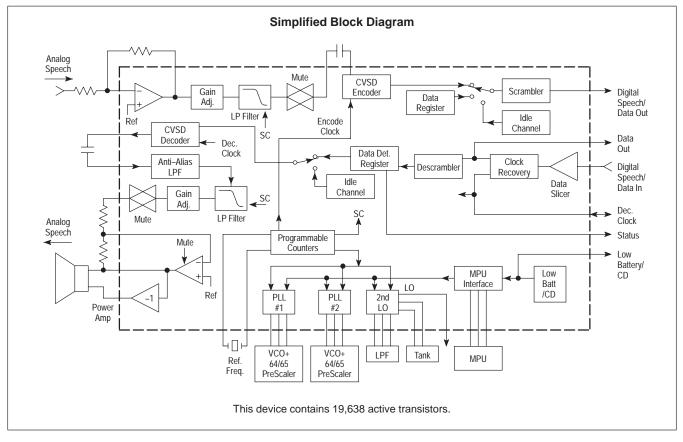

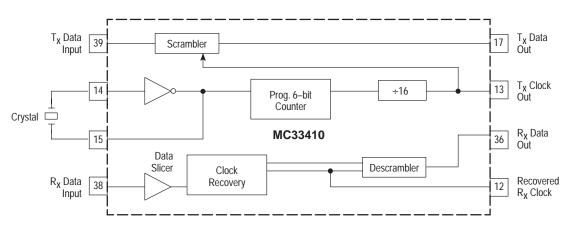

The MC33410 Dual CVSD/Cordless Phone system is designed to fit the requirements of a 900 MHz digital cordless telephone system. The device contains a CVSD (Continuously Variable Slope Delta Modulator/Demodulator) Encoder to digitize the speech for the RF transmission, and a CVSD Decoder to reconstruct the received digital speech from the RF receiver. Provisions are made to transmit and receive data as well. Included are three PLLs (Phase–Locked Loops). Two are intended for use with external VCOs and 64/65 or 128/129 dual modulus prescalers, and can control the transmit and receive (LO1) frequencies for the 900 MHz communication. The third PLL is configured as the 2nd local oscillator (LO2), and is functional to 80 MHz. Also included are muting, audio gain adjust (internal and external), low battery/carrier detect, and a wide range for the PLL reference frequency. The power supply range is 2.7 to 5.5 V. A data only (non–voice) mode is also included.

- Two Complete CVSD Sections for Full Duplex Operation

- Two PLLs and an LO Suitable for a 900 MHz System

- Adjustable Detection for Low Battery or Carrier Signal (RSSI)

- Minimal External Components

- Encode Path Includes Adjustable Gain Amplifiers, Filters, Mute, CVSD Encoder, Data Insert, and Scrambler

- Decoder Path Contains Data Slicer, Clock Recovery, Descrambler, Data Detect, CVSD Decoder, Filters, Mute and Power Amplifier

- Data can be Transmitted During Voice Conversation with Minimal or No Noticeable Audio Disruption

- Idle Channel Noise Control

- Independent Power Amplifier with Differential Outputs, Mute

- Selectable Frequency for Switched Capacitor Filters, CVSD Function, PLLs, and the LO

- Reference Frequency Source can be a Crystal or System Clock

- Serial µP Port to Control Gain, Mute, Frequency Selection, Phase Detector Gain, Power Down Modes, Idle Channel Control, Scrambler Operation, Low Battery Detect, and Others

- Mode Available for Data Only Transmission (non-voice)

- Ambient Temperature Range: –20 to 70°C

- Power Supply Range: 2.7 to 5.5 V

- Power Down Modes for Power Conservation

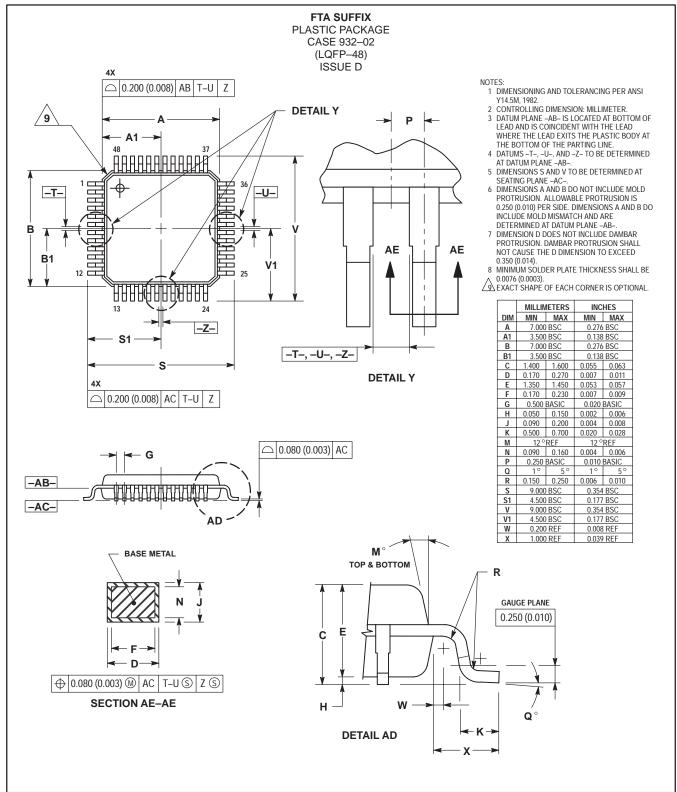

- 48 Pin LQFP with 0.5 mm Lead Pitch

# MC33410

# DUAL CVSD/PLL CORDLESS PHONE SYSTEM

SEMICONDUCTOR TECHNICAL DATA

PLASTIC PACKAGE CASE 932 (LQFP-48)

#### **ORDERING INFORMATION**

| Device     | Operating<br>Temperature | Package |

|------------|--------------------------|---------|

| MC33410FTA | –20 to 70°C              | LQFP-48 |

#### MAXIMUM RATINGS

| Rating                     | Symbol              | Value                 | Unit |

|----------------------------|---------------------|-----------------------|------|

| Supply Voltage             | VCC                 | 6.0                   | V    |

| Input Voltage – All Inputs | V <sub>in</sub>     | V <sub>CC</sub> + 0.5 | V    |

| Junction Temperature       | T <sub>J(max)</sub> | 150                   | °C   |

| Storage Temperature Range  | T <sub>stg</sub>    | -65 to 150            | °C   |

NOTES: 1. Meets Human Body Model (HBM) ≤2000 V and Machine Model (MM) ≤200 V.

2. ESD data available upon request.

#### **RECOMMENDED OPERATING CONDITIONS**

| Characteristic                                                | Symbol | Min  | Тур              | Max | Unit            |

|---------------------------------------------------------------|--------|------|------------------|-----|-----------------|

| Supply Voltage                                                | -      | 2.7  | -                | 5.5 | V               |

| V <sub>B</sub> Load Current                                   | -      | -100 | 0                | 50  | μA              |

| VB Adjusted Voltage Using Bits 7/20–17                        | -      | -    | 1.5              | -   | Vdc             |

| Vag Load Current                                              | -      | -500 | 0                | 50  | μA              |

| CVSD Clock Rate                                               | _      | -    | 32, 50,<br>or 64 | -   | kHz             |

| Encoder in Signal Level (Pin 19, $V_{CC} \ge 3.0 \text{ V}$ ) | -      | -    | -                | 2.9 | V <sub>pp</sub> |

| Rx Audio Input Signal Level (Pin 34)                          | -      | -    | -                | -   | V <sub>pp</sub> |

| Peak Output Current at PAO+, PAO-                             | -      | -    | -                | ±10 | mA              |

| Reference Frequency Amplitude Applied to Pin 14               | -      | 100  | -                | VCC | mVpp            |

| Rx Digital Input Signal Amplitude (Pin 38)                    | -      | -    | -                | 0.7 | V <sub>pp</sub> |

NOTES: 1. Currents into a pin are positive. Currents out of a pin are negative. 2. All recommended limits are not necessarily functional concurrently.

### **RECOMMENDED OPERATING CONDITIONS (continued)**

| Characteristic                                                                              | Symbol | Min                              | Тур | Max                                 | Unit |

|---------------------------------------------------------------------------------------------|--------|----------------------------------|-----|-------------------------------------|------|

| Sink Current into Low Battery Output (Pin 16)                                               | -      | -                                | -   | 1.2                                 | mA   |

| Digital Input Voltage (Pins 10–12, 39)                                                      | -      | -                                | -   | -                                   | -    |

| Maximum Clock/Data Rate at MPU Port (Pins 10–12)                                            | -      | -                                | -   | 2.0                                 | MHz  |

| Crystal or Reference Frequency at Pin 14                                                    | -      | 4.0                              | -   | 18.25                               | MHz  |

| Maximum Data Rate in Data Modem Mode                                                        | -      | -                                | 250 | -                                   | kbps |

| LO2 VCO Control Voltage (Pin 44)                                                            | -      | 0                                | -   | VCC                                 | V    |

| Maximum 2nd LO Frequency                                                                    | -      | -                                | 65  | 80                                  | MHz  |

| 12 Bit Reference Counter Range                                                              | -      | 3 <sub>d</sub>                   | -   | 4095 <sub>d</sub>                   | -    |

| 13 Bit N Counter Range                                                                      | -      | 3 <sub>d</sub>                   | -   | 8191 <sub>d</sub>                   | -    |

| 7 Bit A Counter Range<br>With a 64/65 Modulus Prescaler<br>With a 128/129 Modulus Prescaler | _      | 0 <sub>d</sub><br>0 <sub>d</sub> |     | 63 <sub>d</sub><br>127 <sub>d</sub> | -    |

| 14 Bit LO2 Counter Range                                                                    | -      | 12 <sub>d</sub>                  | _   | 16383 <sub>d</sub>                  | -    |

| 6 Bit Counters (for SCF and Encode Clock)                                                   | -      | 3 <sub>d</sub>                   | -   | 63 <sub>d</sub>                     | -    |

| Maximum SCF Clock Frequency                                                                 | -      | -                                | -   | 512                                 | kHz  |

| Operating Ambient Temperature                                                               | -      | -20                              | -   | 70                                  | °C   |

NOTES: 1. Currents into a pin are positive. Currents out of a pin are negative. 2. All recommended limits are not necessarily functional concurrently.

# **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 3.6 V, f<sub>ref</sub> = 10.24 MHz, unless otherwise noted.)

| Characteristic                                                                                                                                                                                         | Symbol | Min                   | Тур                         | Max                          | Unit                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|-----------------------------|------------------------------|-----------------------------|

| MICROPHONE AMPLIFIER                                                                                                                                                                                   |        |                       | 1                           |                              |                             |

| Output Offset with Respect to $V_B$ (RF = 100 k $\Omega$ )                                                                                                                                             | -      | -                     | 0.5                         | -                            | mVdc                        |

| Input Bias Current (Pin 23)                                                                                                                                                                            | -      | -                     | 10                          | -                            | nA                          |

| Open Loop Gain (f < 100 Hz)                                                                                                                                                                            | -      | -                     | 70                          | -                            | dB                          |

| Gain Bandwidth                                                                                                                                                                                         | -      | -                     | 1.0                         | -                            | MHz                         |

| Maximum Output Voltage Swing (THD < 1%, V <sub>CC</sub> $\geq$ 3.0 V)                                                                                                                                  | -      | -                     | 3.0                         | -                            | V <sub>pp</sub>             |

| Maximum Output Current Capability (V <sub>CC</sub> = 3.6 V)                                                                                                                                            | -      | -                     | 2.2                         | -                            | mA pk                       |

| Tx AUDIO PATH (Pins 22–20)                                                                                                                                                                             | 1      | 1                     | 1                           | 1                            | 1                           |

| Remote Gain Adjust (f = 1.0 kHz)<br>Gain with Bits 6/15–11 = 00100<br>Gain Change (Relative to Bits 6/15–11 = 00100)                                                                                   | -      | -                     | ±0.4                        | _                            | dB                          |

| Bits 6/15–11 = 00001                                                                                                                                                                                   |        | -8.5                  | -7.6                        | -6.5                         |                             |

| Bits 6/15–11 = 00010                                                                                                                                                                                   |        | -5.0                  | -4.3                        | -3.0                         |                             |

| Bits 6/15–11 = 01000                                                                                                                                                                                   |        | 3.0                   | 3.6                         | 5.0                          |                             |

| Bits 6/15–11 = 10000                                                                                                                                                                                   |        | 4.0                   | 7.4                         | 12                           |                             |

| Low Pass Filter (SCF Clock = 256 kHz, Gains are Relative to 400 Hz)<br>-3.0 dB Point<br>$\Delta$ Gain at 3.5 kHz<br>$\Delta$ Gain at 3.7 kHz<br>Gain Reduction at 20 kHz<br>Ripple (400 Hz to 3.5 kHz) | -      | -<br>0<br>-<br>-<br>- | 5.0<br>-<br>-<br>40<br>±0.1 | _<br>0.15<br>_0.15<br>_<br>_ | kHz<br>dB<br>dB<br>dB<br>dB |

| Smoothing Filter –3.0 dB point                                                                                                                                                                         | -      | -                     | 30                          | -                            | kHz                         |

| Muting (Gain Reduction), Bit 6/2 = 1                                                                                                                                                                   | -      | 60                    | 95                          | -                            | dB                          |

| Pin 20 DC Level                                                                                                                                                                                        | -      | -                     | VB                          | -                            | Vdc                         |

| Maximum Output Voltage Swing (THD < 1%, V <sub>CC</sub> $\geq$ 3.0 V)                                                                                                                                  | -      | -                     | 2.9                         | -                            | V <sub>pp</sub>             |

| Maximum Output Current Capability (V <sub>CC</sub> = 3.6 V)                                                                                                                                            | _      | -                     | 1.8                         | -                            | mA pk                       |

| ELECTRICAL CHARACTERISTICS (continued) ( $T_A = 25^{\circ}C$ , V | $V_{CC} = 3.6 \text{ V}, \text{ f}_{ref} = 10.24 \text{ MHz}, \text{ unless otherwise noted.}$ |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Characteristic                                                                 | Symbol | Min                   | Тур                   | Max                   | Unit     |

|--------------------------------------------------------------------------------|--------|-----------------------|-----------------------|-----------------------|----------|

| CVSD ENCODER AND IDLE CHANNEL DETECTION                                        |        |                       |                       |                       |          |

| DC Level (Pin 19)                                                              | _      | -                     | Vag                   | -                     | Vdc      |

| Input Impedance (Pin 19)                                                       | _      | _                     | 150                   | _                     | kΩ       |

| Maximum Input Level                                                            | _      |                       |                       |                       | Vpp      |

| $V_{CC} = 2.7 V$                                                               |        | -                     | 0.8                   | -                     | FF       |

| $V_{CC} \ge 3.0 \text{ V}$                                                     |        | -                     | 2.9                   | -                     |          |

| CVSD DECODER OUTPUT (Pin 35)                                                   |        | 1                     |                       |                       |          |

| Minimum Step Size<br>Bits 2/22–21 = 01                                         | -      | _                     | 1.4                   | _                     | mV       |

| Bits 2/22–21 = 10                                                              |        | -                     | 5.6                   | -                     |          |

| Bits 2/22–21 = 11                                                              |        | -                     | 22.4                  | -                     |          |

| Maximum Output Signal                                                          | -      |                       |                       |                       | Vpp      |

| $V_{CC} \le 3.0 \text{ V}$<br>$V_{CC} > 3.0 \text{ V}$                         |        | -                     | 1.6<br>2.6            | _                     |          |

| Output Current Capability                                                      | _      |                       | _                     |                       | mA pk    |

| Clock Noise Content                                                            | _      | _                     | -65                   |                       | dBm      |

| Rx AUDIO PATH (Pins 34–32)                                                     |        |                       |                       |                       | dBill    |

| Rx Audio In (Pin 34)                                                           | _      |                       |                       |                       |          |

| DC Level                                                                       |        | _                     | VB                    | -                     | Vdc      |

| Input Impedance                                                                |        | -                     | 600                   | -                     | kΩ       |

| Maximum Input Signal                                                           |        | -                     | -                     | -                     | V        |

| Rx Audio Out (Pin 32)<br>DC Level                                              | -      | _                     |                       |                       | Vdc      |

| Maximum Output Current                                                         |        | _                     | V <sub>B</sub><br>1.8 | _                     | mA       |

| Maximum Output Signal                                                          |        | -                     | -                     | -                     | V        |

| Low Pass Filter (SCF Clock = 256 kHz, Gains are Relative to 400 Hz)            | -      |                       |                       |                       |          |

| -3.0 dB Point                                                                  |        | -                     | 5.0                   | -                     | kHz      |

| $\Delta$ Gain at 3.5 kHz<br>$\Delta$ Gain at 3.7 kHz                           |        | 0                     | _                     | 0.25<br>0.25          | dB<br>dB |

| Gain Reduction at 20 kHz                                                       |        | -                     | 40                    | -                     | dB       |

| Ripple (400 Hz to 3.5 kHz)                                                     |        | -                     | ±0.1                  | -                     | dB       |

| Smoothing Filter –3.0 dB Point                                                 | -      | -                     | 30                    | -                     | kHz      |

| Decoder Clock Noise Reduction                                                  | -      | -                     | >20                   | -                     | dB       |

| Receive Gain Adjust (Gain From Pins 34–32, f = 1.0 kHz)                        | -      |                       |                       |                       | dB       |

| Bits 6/10–6 = 01111                                                            |        | -3.0                  | 0                     | 3.0                   |          |

| Bits 6/10–6 = 11001<br>Bits 6/10–6 = 00110                                     |        | 13<br>-15.5           | 14.7<br>-13.7         | 17<br>11.5            |          |

| Gain Range (Gain at 11001 – Gain at 00110)                                     |        | 27                    | 28.5                  | 30                    |          |

| Muting (Gain Reduction), Bit 6/1 = 1                                           | _      | 60                    | 95                    | _                     | dB       |

| POWER AMPLIFIERS                                                               |        |                       |                       |                       |          |

| PAI (Pin 31)                                                                   | _      |                       |                       |                       |          |

| DC Level                                                                       |        | -                     | VB                    | -                     | Vdc      |

| Bias Current                                                                   |        | -                     | <10                   | -                     | nA       |

| PAO- Offset (V <sub>PAO-</sub> - V <sub>B</sub> , Feedback R = 30 k $\Omega$ ) | _      | -                     | 12                    | _                     | mVdc     |

| PAO- to PAO+ Offset                                                            | -      | -                     | ±5.0                  | -                     | mVdc     |

| Open Loop Gain (PAI to PAO–, f < 100 Hz)                                       | -      | -                     | 65                    | -                     | dB       |

| Gain Bandwidth                                                                 | -      | -                     | 1.0                   | -                     | MHz      |

| Closed Loop Gain (PAO- to PAO+)                                                | -      | -                     | ±0.1                  | -                     | dB       |

| Maximum Output Swing (THD $\leq$ 1%)                                           | _      | -                     | -                     | -                     | -        |

| PAO– High Voltage (I <sub>out</sub> = -5.0 mA)                                 | _      | V <sub>CC</sub> – 1.2 | V <sub>CC</sub> – 1.0 | V <sub>CC</sub> – 0.2 | VDC      |

| <b>ELECTRICAL CHARACTERISTICS (continued)</b> ( $T_A = 25^{\circ}C$ , $V_{CC} = 3.6$ V, $f_{ref} = 10.24$ MHz, unless otherwise not | ted.) |

|-------------------------------------------------------------------------------------------------------------------------------------|-------|

|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| <b>ELECTRICAL CHARACTERISTICS (continued)</b> ( $T_A = 25^{\circ}C$ , $V_{CC} = 3$                                        |        | 1                     |                       | oted.)                |       |

|---------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|-----------------------|-----------------------|-------|

| Characteristic                                                                                                            | Symbol | Min                   | Тур                   | Мах                   | Unit  |

| POWER AMPLIFIERS                                                                                                          |        |                       |                       |                       |       |

| PAO- Low Voltage (I <sub>out</sub> = 5.0 mA)                                                                              | -      | 50                    | 420                   | 600                   | mVdc  |

| PAO+ High Voltage (I <sub>out</sub> = -5.0 mA)                                                                            | -      | V <sub>CC</sub> – 1.2 | V <sub>CC</sub> – 1.0 | V <sub>CC</sub> - 0.2 | VDC   |

| PAO+ Low Voltage (I <sub>out</sub> = 5.0 mA)                                                                              | _      | 50                    | 280                   | 600                   | mVdc  |

| Muting to PAO- (Gain Reduction), Bit 6/0 = 1                                                                              | -      | 60                    | 95                    | -                     | dB    |

| VB REFERENCE (Pin 33)                                                                                                     |        |                       |                       |                       |       |

| Initial Voltage (Bits 3/20–17 = 0111)                                                                                     | -      | 1.38                  | 1.50                  | 1.62                  | Vdc   |

| Adjustment Range From Initial Value (Bits 3/20–17 = 0000 to 1111)                                                         | _      | -                     | ±9.0                  | -                     | %     |

| Adjustment per Step (Bits 3/20–17)                                                                                        | _      | _                     | 1.2                   | _                     | %     |

| Closest Adjustment to 1.5 V (Using Bits 3/20–17)                                                                          | _      | 1.47                  | _                     | 1.53                  | Vdc   |

| Power Supply Rejection (f = 1.0 kHz, $C_{VB}$ = 4.7 $\mu$ F)                                                              | _      | _                     | 84                    | _                     | dB    |

|                                                                                                                           |        |                       |                       |                       |       |

| Low Battery Mode (Bit 6/5 = 0) – $V_{CC}$ Threshold (1.47 $\ge$ V <sub>B</sub> $\ge$ 1.53 V,                              | _      |                       |                       |                       | Vdc   |

| V <sub>CC</sub> Decreasing)                                                                                               |        |                       |                       |                       |       |

| Bits 3/23–21 = 000                                                                                                        |        | 2.63                  | 2.9                   | 3.18                  |       |

| Bits $3/23-21 = 001$                                                                                                      |        | 2.71                  | 2.99                  | 3.27                  |       |

| Bits 3/23–21 = 010<br>Bits 3/23–21 = 011                                                                                  |        | 2.79<br>2.87          | 3.07<br>3.16          | 3.36                  |       |

| Bits $3/23 - 21 = 000$                                                                                                    |        | 2.96                  | 3.25                  | 3.45<br>3.54          |       |

| Bits $3/23-21 = 100$                                                                                                      |        | 3.04                  | 3.34                  | 3.64                  |       |

| Bits 3/23–21 = 110                                                                                                        |        | 3.11                  | 3.42                  | 3.73                  |       |

| Bits 3/23–21 = 111                                                                                                        |        | 3.19                  | 3.5                   | 3.81                  |       |

| Hysteresis                                                                                                                | _      | -                     | 6.0                   | -                     | mV    |

| Step Size (Low Battery Mode)                                                                                              | -      | 30                    | 85                    | -                     | mV    |

| Carrier Detect Mode (6/5 = 1) – Threshold @ Pin 36 (V <sub>B</sub> = 1.50 V, $\pm$ 20 mV, Bits 3/23–21 = 000, 7/5–4 = 11) | -      | 650                   | 845                   | 1050                  | mV    |

| Hysteresis                                                                                                                | -      | -                     | 5.0                   | _                     | mV    |

| Output Voltage @ Pin 16 (Output Low, 100 k Pullup Resistor)                                                               | -      | -                     | 0.02                  | _                     | Vdc   |

| Leakage Current @ Pin 16 (Output High)                                                                                    | -      | -                     | <10                   | -                     | nA    |

| MP1, MP2, MP3 ENCODE OUT                                                                                                  | 1      |                       |                       | I                     |       |

| Output Levels (I <sub>out</sub> = $\pm 100 \ \mu$ A)                                                                      | -      |                       |                       |                       |       |

| High Level                                                                                                                |        | -                     | 3.5                   | -                     | Vdc   |

| Low Level                                                                                                                 |        | -                     | 40                    | -                     | mVdc  |

| Input Impdeance @ MP1 (Bits 7/5–4 = 11)                                                                                   | _      |                       |                       |                       |       |

| Low Battery Mode $(6/5 = 0)$                                                                                              |        | -                     | >10                   | -                     | MΩ    |

| Carrier Detect Mode $(6/5 = 1)$                                                                                           |        | -                     | 600                   | -                     | kΩ    |

| DC Level @ MP1 (Bist 7/5-4 = 11, Carrier Detect Mode)                                                                     | -      | -                     | VB                    | -                     | Vdc   |

| MP2 (Bits 7/7–6 = 01 or 1X)                                                                                               | -      |                       |                       |                       |       |

| Input Impedance                                                                                                           |        | -                     | -                     | -                     |       |

| DC Level ( $I_{in} = 0$ )                                                                                                 |        | -                     | 0                     | -                     | Vdc   |

| Input Threshold                                                                                                           |        |                       | 1/2- 24               |                       | 17-1- |

| High                                                                                                                      |        | -                     | V <sub>CC</sub> - 0.4 | -                     | Vdc   |

| Low                                                                                                                       |        | -                     | 0.8                   | -                     | Vdc   |

| DATA SLICER (Pin 38)                                                                                                      | 1      | 1                     |                       |                       |       |

| DC Level                                                                                                                  | -      | -                     | V <sub>CC</sub> – 0.7 | -                     | Vdc   |

| Input Impedance                                                                                                           | -      | -                     | 250                   | -                     | kΩ    |

| Threshold (Increasing Signal)                                                                                             | -      | -                     | V <sub>CC</sub> – 0.7 | -                     | Vdc   |

| Hysteresis                                                                                                                | _      | 20                    | 35                    | 60                    | mV    |

**ELECTRICAL CHARACTERISTICS (continued)** ( $T_A = 25^{\circ}C$ ,  $V_{CC} = 3.6$  V,  $f_{ref} = 10.24$  MHz, unless otherwise noted.)

| Characteristic                                                                                                                             | Symbol | Min        | Тур  | Max         | Unit   |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|------|-------------|--------|

| Tx/Rx PLL/PHASE DETECTORS                                                                                                                  | •      | •          |      | •           | •      |

| Phase Detector Output Current (0.5 V $\leq$ V <sub>OUt</sub> $\leq$ V <sub>CC</sub> – 0.5 V)<br>100 $\mu$ A Mode (Bits 1/20, 2/20 = 0)     | -      |            |      |             | μA     |

| Sink                                                                                                                                       |        | 70         | 100  | 130         |        |

| Source                                                                                                                                     |        | -130       | -100 | -70         |        |

| 400 μA Mode (Bits 1/20, 2/20 = 1)                                                                                                          |        |            |      |             |        |

| Sink                                                                                                                                       |        | 280        | 400  | 520         |        |

| Source                                                                                                                                     |        | -520       | -400 | -280        |        |

| Phase Detector Current Ratio (Source/Sink)<br>( $V_{out} = V_{CC}/2$ , ±100 µA and ±400 µA Ranges)                                         | -      | 0.80       | 1.0  | 1.25        | μΑ/μΑ  |

| Phase Detector Leakage Current (High–Z Mode @ V <sub>CC</sub> /2)                                                                          | -      | -80        | ±1.5 | 80          | nA     |

| FRxMC/FTxMC Output Voltage (Bit 7/13 = 1, $I_{OUT} = \pm 100 \mu A$ )                                                                      |        |            |      |             | V      |

| High                                                                                                                                       |        | 3.4        | 3.5  | -           |        |

| Low                                                                                                                                        |        | -          | 0.02 | 0.2         |        |

| FRxMC/FTxMC Output Current (Bit 7/13 = 0, V <sub>OUt</sub> = 0.8 V)                                                                        | -      |            |      |             | μΑ     |

| Sink                                                                                                                                       |        | 70         | 100  | 130         |        |

| Source                                                                                                                                     |        | -130       | -100 | -70         |        |

| FRx/FTx                                                                                                                                    | -      |            |      |             |        |

| Input Current, V <sub>in</sub> = V <sub>CC</sub><br>FRx                                                                                    |        | 0          | 10   | 14          | μA     |

| FTx                                                                                                                                        |        | 0          | 10   | 30          |        |

| V <sub>in</sub> = 0 V                                                                                                                      |        | -10        | -7.5 | -           |        |

| DC Level                                                                                                                                   |        | _          | 1.5  | _           | Vdc    |

| Input Amplitude                                                                                                                            |        | 200        | -    | 1200        | mVpp   |

| Propagation Delay (FRx to FRxMC and FTx to FTxMC)                                                                                          | -      | -          | 20   | -           | ns     |

| L <b>O2 PLL</b> (Pins 41–48)                                                                                                               |        |            |      |             |        |

| Maximum Frequency                                                                                                                          | -      | 65         | 80   | -           | MHz    |

| Input Current @ LO2 Control (0.5 V $\leq$ V <sub>in</sub> $\leq$ V <sub>CC</sub> – 0.5 V)                                                  | -      | -1.0       | 0    | 1.0         | μΑ     |

| Phase Detector Output Current (0.5 V $\leq$ V <sub>OUt</sub> $\leq$ V <sub>CC</sub> – 0.5 V)<br>100 $\mu$ A Mode (Bit 3/14 = 0)            | -      |            |      |             | μΑ     |

| Sink                                                                                                                                       |        | 70         | 100  | 130         |        |

| Source                                                                                                                                     |        | -130       | -100 | -70         |        |

| 400 µA Mode (Bit 3/14 = 1)                                                                                                                 |        |            |      |             |        |

| Sink                                                                                                                                       |        | 280        | 400  | 520         |        |

| Source                                                                                                                                     |        | -520       | -400 | -280        |        |

| Phase Detector Current Ratio (Source/Sink) $(V_{out} = V_{CC}/2, \pm 100 \ \mu\text{A} \text{ and } \pm 400 \ \mu\text{A} \text{ Ranges})$ | -      | 0.80       | 1.0  | 1.25        | μΑ/μΑ  |

| Phase Detector Leakage Current (High–Z Mode @ V <sub>CC</sub> /2)                                                                          | -      | -80        | ±1.5 | 80          | nA     |

| LO2 Output Amplitude (Pin 41 with 25 $\Omega$ Load)                                                                                        | -      | -          | 58   | _           | mVpp   |

| Frequency Change (L = 150 nH, C = 27 pF)                                                                                                   | -      |            |      |             | MHz    |

| Pin 44 Changed from 0.4 to 0.6 V                                                                                                           |        | 0.9        | 1.3  | 1.7         |        |

| Pin 44 Changed from 2.5 to 3.0 V                                                                                                           |        | 0.8        | 1.2  | 1.6         |        |

| Internal Capacitor (Pin 43–45)                                                                                                             | -      |            |      |             | pF     |

| Bits 7/20–18 = 001                                                                                                                         |        | 1.0        | 1.1  | 1.3         |        |

| Bits $7/20-18 = 010$                                                                                                                       |        | 1.9        | 2.2  | 3.5         |        |

| Bits 7/20–18 = 100<br>Bits 7/20–18 = 111                                                                                                   |        | 4.0<br>7.0 | 4.4  | 6.5<br>10.5 |        |

|                                                                                                                                            |        |            |      | 10.0        |        |

| Internal Capacitor Change (Pin 43–45)<br>(Bits 7/20–18 Increased from 000 to 111)                                                          | -      | 0          | 1.1  | -           | pF/Ste |

| <b>ELECTRICAL CHARACTERISTICS (continued)</b> (T <sub>A</sub> = 25°C, $V_{CC}$ = 3 | 3.6 V, f <sub>ref</sub> = 10.24 | 4 MHz, unles | s otherwise r | noted.) |      |

|------------------------------------------------------------------------------------|---------------------------------|--------------|---------------|---------|------|

| Characteristic                                                                     | Symbol                          | Min          | Typ           | Max     | Unit |

| Characteristic                                                                                                                                                                                                                                                            | Symbol | Min              | Тур                           | Max              | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|-------------------------------|------------------|------|

| REFERENCE OSCILLATOR (Pins 14, 15)                                                                                                                                                                                                                                        |        | •                |                               |                  |      |

| f <sub>ref</sub> Out Output Levels (I <sub>OUt</sub> = ±100 μA)<br>High Level<br>Low Level                                                                                                                                                                                | -      |                  | V <sub>CC</sub> - 0.2<br>0.2  | -                | Vdc  |

| DC Bias Voltage @ f <sub>ref</sub> In                                                                                                                                                                                                                                     | _      | -                | V <sub>CC</sub> /2            | _                | Vdc  |

| Input Current @ $f_{ref}$ In<br>$V_{in} = 0 V$<br>$V_{in} = V_{CC}$                                                                                                                                                                                                       | -      | -15<br>2.0       | 5.0<br>5.6                    | -2.0<br>15       | μA   |

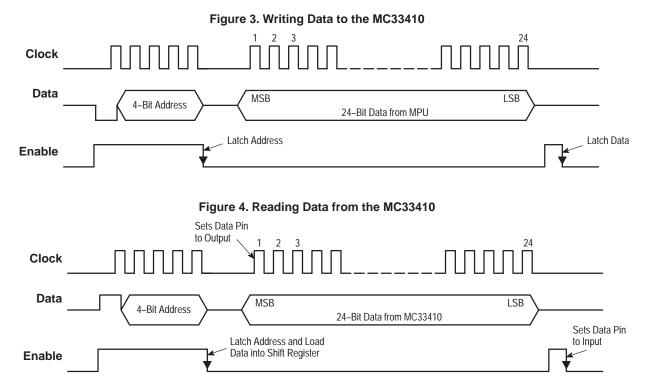

| MPU SERIAL INTERFACE PORT (Pins 10-12)                                                                                                                                                                                                                                    |        |                  |                               |                  |      |

| Input Switching Threshold @ V <sub>CC</sub> = 3.6 V<br>High<br>Low                                                                                                                                                                                                        | _      |                  | 3.1<br>0.7                    | -<br>-           | Vdc  |

| Input Current<br>$V_{in} = 3.3 V$<br>$V_{in} = 0.3 V$                                                                                                                                                                                                                     | _      | 0.5<br>0.05      | 1.6<br>0.5                    | 3.0<br>1.5       | μΑ   |

| Data (Pin 12) Output Levels (I <sub>out</sub> = ±100 μA)<br>High<br>Low                                                                                                                                                                                                   | -      |                  | 3.5<br>0.1                    | -                | Vdc  |

| Timing<br>Enable to Clock Setup Time<br>Data to Clock Setup Time<br>Data, Clock Hold Time<br>Recovery Time<br>Data, Clock Pulse Width                                                                                                                                     | _      | -<br>-<br>-<br>- | 200<br>100<br>90<br>90<br>100 | -<br>-<br>-<br>- | ns   |

| Power On Reset Delay                                                                                                                                                                                                                                                      | _      | -                | 100                           | _                | μs   |

| Input Capacitance                                                                                                                                                                                                                                                         | -      | -                | 8.0                           | _                | pF   |

| Minimum V <sub>CC</sub> to Maintain Register Settings                                                                                                                                                                                                                     | -      | -                | 1.0                           | -                | Vdc  |

| POWER SUPPLY CURRENT                                                                                                                                                                                                                                                      | ·      |                  | •                             |                  | •    |

| All Sections Enabled (Bits 5/10–0 = 0)                                                                                                                                                                                                                                    | -      | 9.0              | 12.5                          | 16               | mA   |

| Wakeup Mode (Bits 5/9–5, 1 = 1)                                                                                                                                                                                                                                           | -      | 5.5              | 7.7                           | 10               | mA   |

| MPU Port Only Enabled (Bits 5/10–0, 18 = 1)<br>V <sub>CC</sub> = 3.6 V<br>V <sub>CC</sub> = 5.5 V                                                                                                                                                                         | _      | -                | 6.0<br>-                      | 15<br>50         | μA   |

| AUDIO SYSTEM SPECIFICATIONS                                                                                                                                                                                                                                               |        |                  |                               |                  |      |

| Gain From Audio In to PAO–<br>$V_{in} = -40 \text{ dBV}, f_{in} = 1.0 \text{ kHz}, V_{CC} = 3.6 \text{ V}$<br>$V_{in} = -60 \text{ dBV}, f_{in} = 200 \text{ Hz}, V_{CC} = 2.7 \text{ V}$<br>$V_{in} = -20 \text{ dBV}, f_{in} = 3.4 \text{ kHz}, V_{CC} = 5.5 \text{ V}$ | _      | 17<br>17<br>17   | 20.3<br>19.3<br>18.7          | 23<br>23<br>23   | dB   |

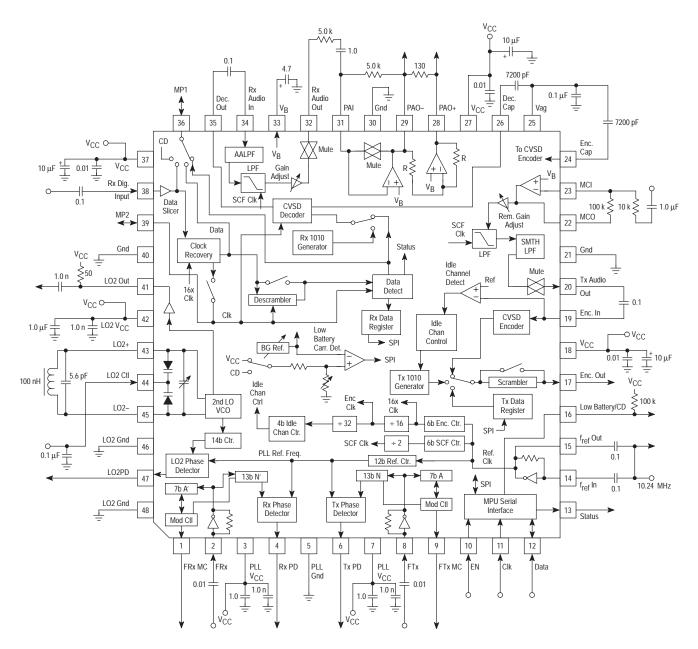

### Figure 1. Test Circuit

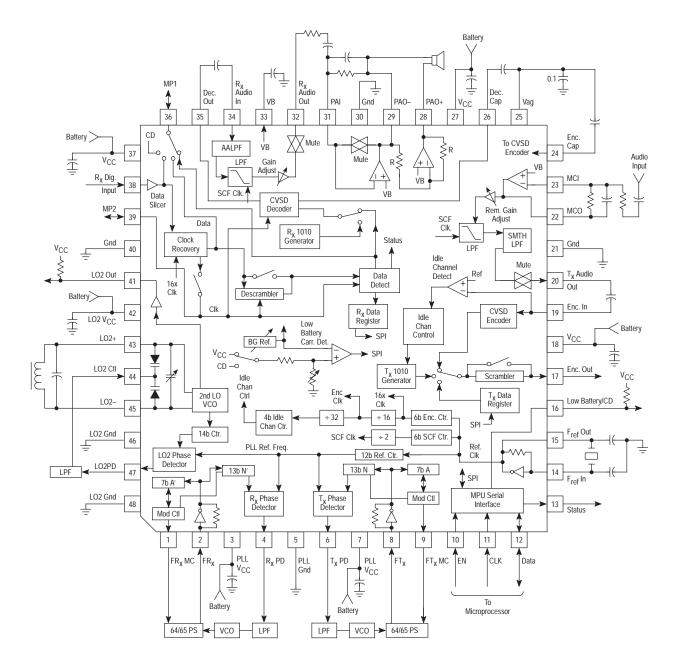

### Figure 2. Typical Applications Circuit

### PIN FUNCTION DESCRIPTION

| Pin    | Name                                         | Description                                                                                                                                                                                                                                                       |  |  |  |

|--------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1      | FR <sub>X</sub> MC                           | Modulus Control Output to the $R_X$ 64/65 or 128/129 dual modulus prescaler.                                                                                                                                                                                      |  |  |  |

| 2      | FR <sub>X</sub>                              | Input to the R <sub>X</sub> PLL.                                                                                                                                                                                                                                  |  |  |  |

| 3      | PLL V <sub>CC</sub>                          | Supply pin for the $R_X$ PLL section. Allowable range is 2.7 to 5.5 V.                                                                                                                                                                                            |  |  |  |

| 4      | R <sub>X</sub> PD                            | Phase detector charge pump output of the R <sub>X</sub> PLL.                                                                                                                                                                                                      |  |  |  |

| 5      | PLL Gnd                                      | Ground pin for the PLL sections.                                                                                                                                                                                                                                  |  |  |  |

| 6      | T <sub>X</sub> PD                            | Phase detector charge pump output of the T <sub>X</sub> PLL.                                                                                                                                                                                                      |  |  |  |

| 7      | PLL VCC                                      | Supply pin for the $T_X$ PLL section and the MPU Serial Interface section. Allowable range is 2.7 to 5.5 V.                                                                                                                                                       |  |  |  |

| 8      | FT <sub>X</sub>                              | Input to the T <sub>X</sub> PLL.                                                                                                                                                                                                                                  |  |  |  |

| 9      | FT <sub>X</sub> MC                           | Modulus Control Output to the $T_X$ 64/65 or 128/129 dual modulus prescaler.                                                                                                                                                                                      |  |  |  |

| 10     | EN                                           | Enable input for the $\mu$ P port. This signal latches in the register address and data.                                                                                                                                                                          |  |  |  |

| 11     | CLK                                          | Clock input for the $\mu$ P port. Maximum frequency is 2.0 MHz.                                                                                                                                                                                                   |  |  |  |

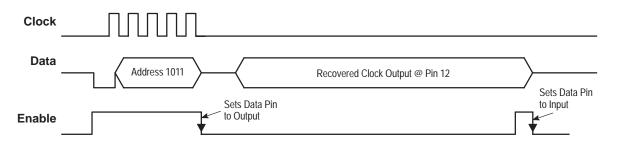

| 12     | Data                                         | Bi–directional data line for the $\mu$ P port. In Data Modem mode, this pin provides the recovered clock.                                                                                                                                                         |  |  |  |

| 13     | Status                                       | Logic output which indicates that a predetermined 16 or 24–bit code word has been detected in the Data Detect register, and the following data word has been loaded into register 10. In Data Modem mode, this pin provides the Transmit Data clock.              |  |  |  |

| 14, 15 | F <sub>ref</sub> In,<br>F <sub>ref</sub> Out | A crystal, in the range of 4.0 to 18.25 MHz can be connected to these pins to provide the reference frequency. If an external reference source is used, it is to be capacitively coupled to $F_{ref}$ In.                                                         |  |  |  |

| 16     | Low Battery/CD                               | An open collector output. When low, indicates either the supply voltage ( $V_{CC}$ ) is low, or the carrier level is above the threshold. This output is off when disabled.                                                                                       |  |  |  |

| 17     | Enc Out                                      | The digital output of the scrambler, which passes data from the CVSD encoder, or the $T_X$ Data register, the $T_X$ 1010 Generator. Source selection is done through the $\mu P$ port.                                                                            |  |  |  |

| 18     | VCC                                          | Supply input for the audio sections, filters, and CVSD blocks. Allowable range is 2.7 to 5.5 V. Internally connected to Pins 27 and 37.                                                                                                                           |  |  |  |

| 19     | Enc In                                       | The analog input to the CVSD encoder. Max. input level is 3.0 $V_{pp}$ .                                                                                                                                                                                          |  |  |  |

| 20     | T <sub>X</sub> Audio Out                     | Output of the transmit speech processing section.                                                                                                                                                                                                                 |  |  |  |

| 21     | Ground                                       | Ground for the audio sections, filters, and CVSD blocks. Internally connected to Pins 30 and 40.                                                                                                                                                                  |  |  |  |

| 22     | МСО                                          | Output of the microphone amplifier, and input to the filters. This output has rail-to-rail capability.                                                                                                                                                            |  |  |  |

| 23     | MCI                                          | Inverting input of the microphone amplifier. Gain and frequency response is set with external resistors and capacitors.                                                                                                                                           |  |  |  |

| 24     | Enc Cap                                      | This capacitor sets the time constant for the CVSD encoder. This pin is sensitive to leakage.                                                                                                                                                                     |  |  |  |

| 25     | VAG                                          | Analog ground for the audio section and the CVSD encoder and decoder.                                                                                                                                                                                             |  |  |  |

| 26     | Dec Cap                                      | The capacitor sets the time constant for the CVSD decoder. This pin is sensitive to leakage.                                                                                                                                                                      |  |  |  |

| 27     | VCC                                          | Supply input for the audio sections, filters, and CVSD blocks. Allowable range is 2.7 to 5.5 V. Internally connected to Pins 18 and 37.                                                                                                                           |  |  |  |

| 28, 29 | PAO+, PAO-                                   | Differential outputs of the power amplifier stage for driving an earpiece or hybrid network. The gain and frequency response are set with external resistors and capacitors.                                                                                      |  |  |  |

| 30     | Gnd                                          | Ground for the audio sections, filters, and CVSD blocks. Internally connected to Pins 21 and 40.                                                                                                                                                                  |  |  |  |

| 31     | PAI                                          | Input to the power amplifier stage. This pin is a summing node.                                                                                                                                                                                                   |  |  |  |

| 32     | R <sub>X</sub> Audio Output                  | Output of the receive speech processing section.                                                                                                                                                                                                                  |  |  |  |

| 33     | VB                                           | The capacitor filters the internal 1.5 V reference voltage. If VB is adjusted, it may be monitored at this pin.<br>Max. load current is 10 μA.                                                                                                                    |  |  |  |

| 34     | R <sub>X</sub> Audio In                      | Input to the receive speech processing section.                                                                                                                                                                                                                   |  |  |  |

| 35     | Dec Out                                      | The analog output of the CVSD decoder.                                                                                                                                                                                                                            |  |  |  |

| 36     | MP1                                          | As an output, provides the recovered $R_X$ data, or the Data Detect output, or the data slicer output. Or it can be set to a high impedance input (600 k $\Omega$ ) for the carrier detect input signal. Selection is done through the $\mu$ P port. See Table 6. |  |  |  |

NOTE: 1. All V\_CC pins must be within  $\pm 0.5$  V of each other.

### PIN FUNCTION DESCRIPTION (continued)

| Pin    | Name                         | Description                                                                                                                                                                                                                                                                                                                  |

|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37     | V <sub>CC</sub>              | Supply input for the audio sections, filters, and CVSD blocks. Allowable range is 2.7 to 5.5 V. Internally connected to Pins 18 and 27.                                                                                                                                                                                      |

| 38     | R <sub>X</sub> Digital Input | The digital stream from the RF receiver is applied to the data slicer at this pin. Minimum amplitude is 200 mVpp. Hysteresis ≈50 mV.                                                                                                                                                                                         |

| 39     | MP2                          | As an output, this pin provides the recovered clock from the Clock Recovery block. As an input, the CVSD decoder clock can be applied to this pin. Or this pin may be set to a disabled state. Selection is done through the $\mu$ P port. See Table 7. In Data Modem mode, the data to be transmitted is input to this pin. |

| 40     | Gnd                          | Ground for the audio sections, filters, and CVSD blocks. Internally connected to Pins 21 and 30.                                                                                                                                                                                                                             |

| 41     | LO2 Out                      | Buffered output of the 2nd LO frequency. A pullup resistor is required.                                                                                                                                                                                                                                                      |

| 42     | LO2 V <sub>CC</sub>          | Supply pin for the 2nd LO. Allowable range is 2.7 to 5.5 V.                                                                                                                                                                                                                                                                  |

| 43, 45 | LO2+, LO2–                   | A tank circuit is connected to these pins for the 2nd LO.                                                                                                                                                                                                                                                                    |

| 44     | LO2 Ctl                      | The varactor control pin for the 2nd LO.                                                                                                                                                                                                                                                                                     |

| 46     | LO2 Gnd                      | Ground for the 2nd LO section.                                                                                                                                                                                                                                                                                               |

| 47     | LO2 PD                       | Phase detector charge pump output of the 2nd LO PLL.                                                                                                                                                                                                                                                                         |

| 48     | LO2 Gnd                      | Ground for the 2nd LO section.                                                                                                                                                                                                                                                                                               |

NOTE: 1. All V\_CC pins must be within  $\pm 0.5$  V of each other.

# MC33410 FUNCTIONAL DESCRIPTION

Note: In the following descriptions, control bits in the MPU Serial Interface for the various functions will be identified by register number and bit number. For example, bit 3/19 indicates bit 19 of register 3. Bits 5/14–11 indicates register 5, bits 14 through 11. Please refer to Figure 1.

#### **Transmit Speech Processing Section**

This section is made up of the externally adjustable microphone amplifier (Pins 22 to 23), internally adjustable gain stage, two low pass filters, and a mute switch.

The gain of the microphone amplifier is set with external resistors to receive the audio from the microphone (in the handset), or from the hybrid (in the base unit), or from any other audio source. The MCO output has rail-to-rail capability, and the dc bias level is at VB ( $\approx$ 1.5 V).

The adjustable gain stage, referred to as the Remote Gain Adjust, provides 5 levels of gain in 4.0 dB increments. It is controlled with bits 6/15–11 as shown in Table 1.

| Register 6 |                 |  |  |  |

|------------|-----------------|--|--|--|

| Bits 15-11 | Gain            |  |  |  |

| 00001      | -8.0 dB         |  |  |  |

| 00010      | -4.0 dB         |  |  |  |

| 00100      | 0 dB            |  |  |  |

| 01000      | +4.0 dB         |  |  |  |

| 10000      | +8.0 dB         |  |  |  |

| 00100      | 0 dB<br>+4.0 dB |  |  |  |

Table 1. Remote Gain Adjust

Other combinations for the 5 bits are invalid.

The Low Pass Filter after the gain stage is a switched capacitor filter with a corner frequency at 5.0 kHz. The subsequent smoothing low pass filter has a corner frequency at 30 kHz, and is designed to filter out high frequency clock noise from the previously mentioned switched capacitor filter.

The mute switch at Pin 20 will mute a minimum of 60 dB. Bit 6/2 controls the mute.

#### CVSD Encoder/Idle Channel/T<sub>X</sub> Data Register

The analog signals to be digitized are input at Pin 19 to the CVSD Encoder. The output of the encoder will be the digital equivalent of the audio, at the selected clock rate. Based on the reference frequency, bits 4/23–18 are used to set the 6 Bit Encoder Counter, in conjunction with the subsequent ÷16 divider, to set the CVSD Encoder frequency to 32, 50, or 64 kHz. Bits 3/16–15 will set the CVSD for proper operation at the selected frequency, according to Table 2.

| Table | 2.       | CVSD | Clock/Data  | Rates |

|-------|----------|------|-------------|-------|

| TUDIC | <u> </u> | 0100 | Olociv Data | naico |

| Register 3 |        |                 |

|------------|--------|-----------------|

| Bit 16     | Bit 15 | Clock/Data Rate |

| 0          | 1      | 32 kHz          |

| 1          | 0      | 50 kHz          |

| 1          | 1      | 64 kHz          |

The Encoder's minimum step size can be selected using bits 2/22–21, according to Table 3.

| Table | 3. | Minimum | Step | Size |

|-------|----|---------|------|------|

|-------|----|---------|------|------|

| Encoder<br>Register 2<br>Bits 22, 21 | Decoder<br>Register 1<br>Bits 22, 21 | Step Size  |

|--------------------------------------|--------------------------------------|------------|

| 00                                   | 00                                   | No minimum |

| 01                                   | 01                                   | 1.4 mV     |

| 10                                   | 10                                   | 5.6 mV     |

| 11                                   | 11                                   | 22.4 mV    |

The  $T_X$  1010 Generator, when selected, provides an alternating "1–0" pattern (a square wave at half the CVSD clock rate) to the scrambler. This represents the lowest amplitude analog signal, and can be used when it is desired to send a quiet signal. Selection of this block can occur either automatically, or intentionally, as follows:

- a. The automatic selection occurs when the Idle Channel Detector senses the average audio signal at Pin 19 is below a threshold which is set with bits 5/17-15 (See Table 4). Bits 5/14–11 select a time delay for the automatic threshold detection to occur. The minimum delay is zero, with these bits set to 0000. Changing the bits provides delay in increments of 32 clock cycles (of the CVSD Encoder clock). The maximum delay is 480 clock cycles, (7.5 mS at 64 kHz). When the average audio signal at Pin 19 increases above the threshold, the  $T_x$  1010 Generator will be deselected with no delay. This automatic switchover feature can be disabled with bit 7/2. Bit 5/21 indicates when an idle channel condition has been detected. This output bit will be functional even when the idle channel detector is disabled with bit 7/2. Bit 5/18 will power down the Idle Channel Detect Circuit as a power saving measure.

- b. Bit 6/4 can be used to intentionally select the  $T_X$  1010 Generator at any time.

| Register 5 |           | Register 5 |           |

|------------|-----------|------------|-----------|

| Bits 17-15 | Threshold | Bits 17-15 | Threshold |

| 000        | –50 dBV   | 100        | -60 dBV   |

| 001        | -52.5     | 101        | -62.5     |

| 010        | -55       | 110        | -65       |

| 011        | -57.5     | 111        | -67.5     |

**Table 4. Idle Channel Detection Threshold**

The  $T_{\rm X}$  Data Register is used for the transmission of data between the handset and base units. The procedure is as follows:

- a. At the receiving unit: The code word (16 or 24 bits, set with bit 7/11) identifying that a data transmission is occurring must be loaded into the  $T_X$  Data Register (by loading register 8). This is used to detect when a code word is sent from the transmitting unit.

- b. At the transmitting unit: The same code word as above is loaded into register 8. It is automatically loaded into the  $T_X$  Data Register.

- c. The data word (16 or 24 bits, set with bit 7/12) is then loaded into register 9.

- d. Upon loading register 9, the MC33410 automatically sends out (at Pin 17) the code word, followed by the data word, at the CVSD clock rate.

When the data word is completely sent out, the MC33410 will then return Pin 17 to its previous source of digital information (CVSD Encoder or  $T_x$  1010 Generator).

#### Scrambler/Digital Output

The scrambler receives digital data from the CVSD Encoder, or the  $T_X$  1010 Generator, or the  $T_X$  Data Register,

to be output at Pin 17. The output level is 0 to  $V_{CC}$ . The scrambler can be bypassed with Bit 7/1.

The scrambler, better known as a randomizer, provides not only a level of communication security, but also helps ensure the digital output will not contain an abnormally long string of 1s or 0s which can adversely affect the CVSD Decoder operation, as well as the RF section. The scrambler is a maximal–length shift register sequence generator. The length of the shift register is selectable to one of eight values with bits 7/10–8 (the descrambler in the receiving unit must be set the same). Table 5 lists the polynomial associated with each tap selection.

| Тар | Register 7 |       |       |                       |                                        |

|-----|------------|-------|-------|-----------------------|----------------------------------------|

| No. | Bit 10     | Bit 9 | Bit 8 | Shift Register Length | Polynomial                             |

| 0   | 0          | 0     | 0     | 2                     | 1 + z <sup>-1</sup> + z <sup>-2</sup>  |

| 1   | 0          | 0     | 1     | 3                     | $1 + z^{-2} + z^{-3}$                  |

| 2   | 0          | 1     | 0     | 4                     | 1 + z <sup>-3</sup> + z <sup>-4</sup>  |

| 3   | 0          | 1     | 1     | 5                     | 1 + z <sup>-3</sup> + z <sup>-5</sup>  |

| 4   | 1          | 0     | 0     | 6                     | 1 + z <sup>-5</sup> + z <sup>-6</sup>  |

| 5   | 1          | 0     | 1     | 7                     | 1 + z <sup>-6</sup> + z <sup>-7</sup>  |

| 6   | 1          | 1     | 0     | 9                     | 1 + z <sup>-5</sup> + z <sup>-9</sup>  |

| 7   | 1          | 1     | 1     | 10                    | 1 + z <sup>-7</sup> + z <sup>-10</sup> |

#### Data Slicer/Clock Recovery

The data slicer will receive the low level digital signal from the RF receiver section at Pin 38. The input signal to the data slicer must be >200 mVpp. Hysteresis of 50 mV is internally provided. The output of the data slicer will be same waveform, but with an amplitude of 0 to V<sub>CC</sub>, and can be observed at Pin 36 (MP1) if bits 7/5–4 are set to 10. The output can be inverted by setting bit 5/19 = 1.

The clock recovery block will generate a phase locked clock, equal to the CVSD data rate, from the incoming data, as long as the Encoder Counter (bits 4/23–18) is set for that data rate. The recovered clock can be observed at Pin 39 (MP2) if bits 7/7–6 are set to 00. The data from the clock recovery block can be observed at Pin 36 if bits 7/5–4 are set to 00. The clock recovery block may be bypassed by setting bit 7/0 to 1. With this setting the data slicer output will go directly to the descrambler, and the encoder clock will replace the Clock Recovery Clock.

Tables 6 and 7 summarize the options available at MP1 and MP2 (Pins 36 and 39).

| Regis | ster 7 |                                |

|-------|--------|--------------------------------|

| Bit 5 | Bit 4  | Function                       |

| 0     | 0      | Data from clock recovery block |

| 0     | 1      | Data Detect Output             |

| 1     | 0      | Data Slicer Output             |

| 1     | 1      | Hi–Z/ CD Input                 |

Table 6. MP1 Options (Pin 36)