# CD22402

#### November 1996

## Features

- Interlaced Composite Sync Output

- Automatic Genlock Capability

- Crystal Oscillator Operation

- 525 or 625 Line Operation

- Vertical Reset Option

- Wide Power Supply Operating Voltage ..... 4V to 15V

## Applications

- Cameras

- Monitors and Displays

- CATV

- Teletext

- Video Games

- Sync Restorer

- Video Service Instruments

# Ordering Information

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE     | PKG.<br>NO. |

|-------------|----------------------------------|-------------|-------------|

| CD22402D    | -55 to 125                       | 24 Ld SBDIP | D24.6       |

| CD22402E    | -40 to 85                        | 24 Ld PDIP  | E24.6       |

# Description

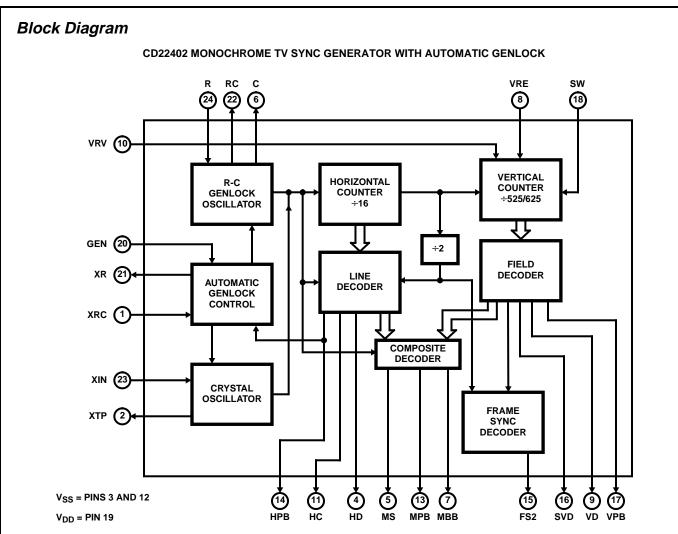

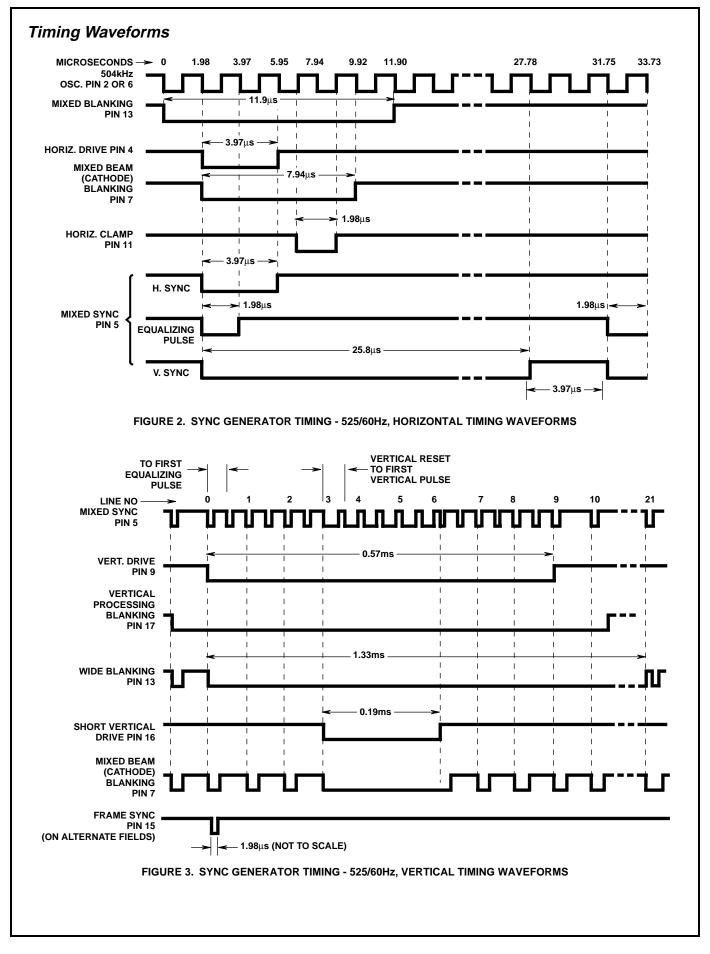

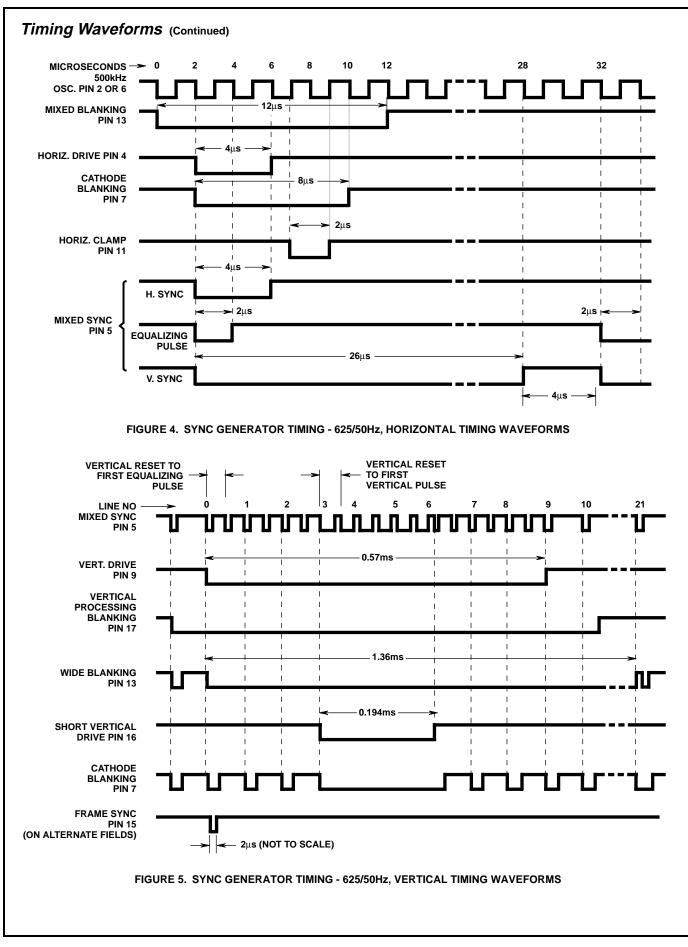

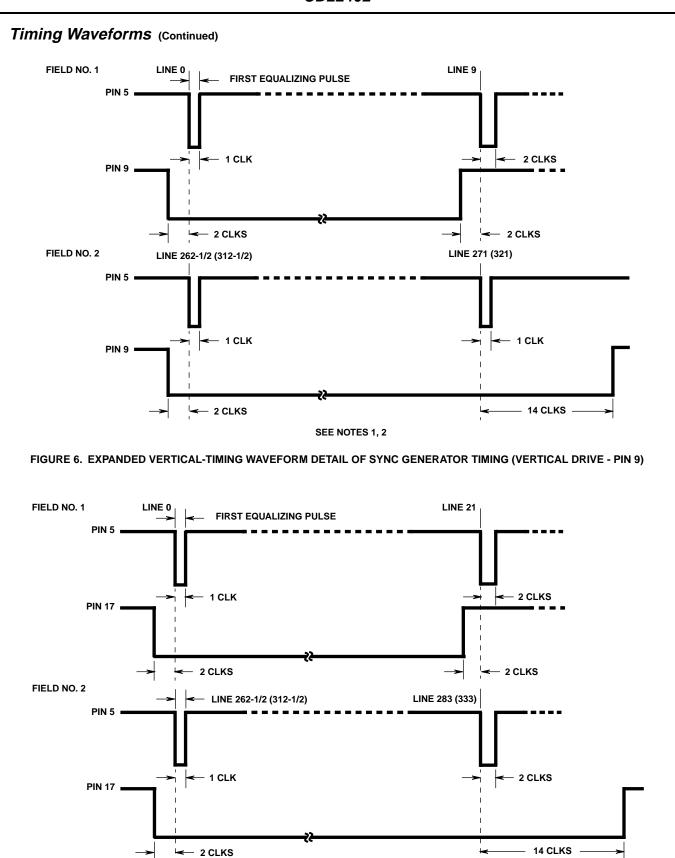

The Harris CD22402 (Note) is a CMOS LSI sync generator that produces all the timing signals required to drive a fully 2-to-1 interlaced 525-line 30-frame/second, or 625-line 25-frame/second TV camera or video processing system. A complete sync waveform is produced which begins each field with six serrated vertical sync pulses, preceded and followed by six half-width double frequency equalizing pulses. The sync output is gated by the master clock to preserve horizontal phase continuity during the vertical interval.

Sync Generator for TV Applications

and Video Processing Systems

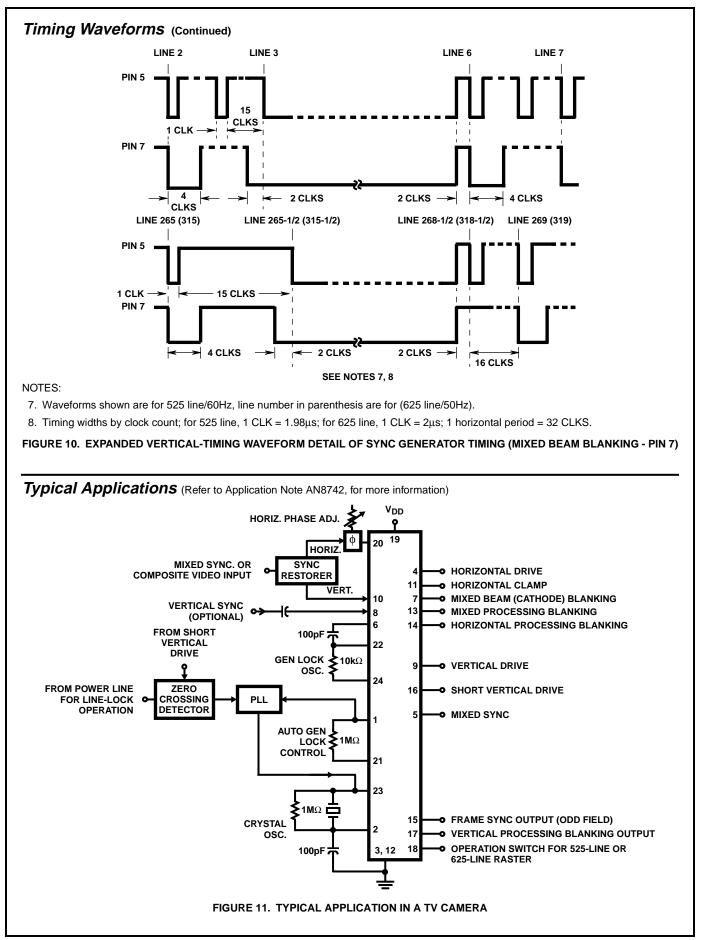

The CD22402 can be operated either in "genlock" mode, in which it is synchronized with a reference sync pulse train from another TV camera, or in "stand-alone" mode, in which it is synchronized with a local on-chip crystal oscillator (the crystal and two passive components are off chip). Also, the circuit can sense the presence or absence of a reference sync pulse train and automatically select the "genlock" or "stand-alone" mode.

A frame sync pulse is produced at the beginning of every odd field. The vertical counter can be reset to either the first equalizing pulse or the first vertical sync pulse of the vertical interval. The interlaced sync provided by the CD22402 differs from RS-170 by having slightly narrower sync and equalizing pulses. The clock frequency of 32 times horizontal rate allows for approximately 4µs horizontal pulse widths and 2µs equalizing pulses. Otherwise operation can be phase locked to a color sub-carrier for a full interlaced operating system.

The CD22402 is operable with a single supply over a voltage range of 4V to 15V.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

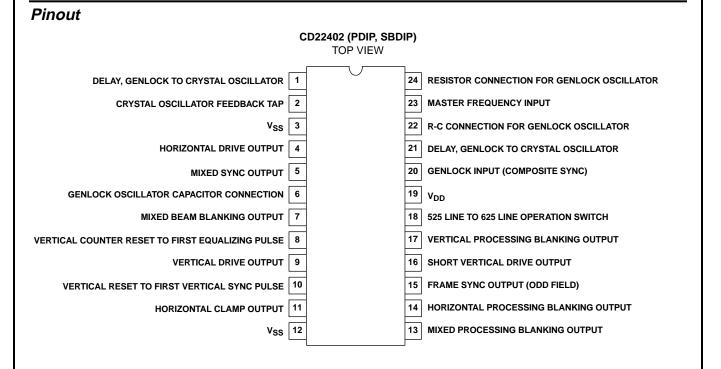

# Pin Descriptions

| PIN NO. | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | XRC             | <b>Delay, Genlock to Crystal Oscillator.</b> Resistor, diode and capacitor connection for delay that automatically turns on the crystal oscillator when the genlock input is removed. When the signal on Terminal 1 is high the crystal oscillator is inhibited. Typical values for R and C are $1M\Omega$ and $0.001\mu$ F. For operation as a crystal controlled stand alone sync generator without genlock, Terminal 1 should be hardwired to V <sub>SS</sub> .                                                                                                            |

| 2       | XTP             | <b>Crystal Oscillator Feedback Tap.</b> Feedback connection (tap) for crystal oscillator. When a crystal (shunted by a 1M $\Omega$ resistor) is connected between this terminal and Terminal 23, and a 100pF capacitor is connected from this terminal to V <sub>SS</sub> , the sync generator creates its own master frequency. For a 525-line, 30-frame/second raster, the crystal frequency is 504.000kHz (Note 1); and for a 625-line, 25-frame/second raster, the crystal frequency is 500.000kHz (Note 1).                                                              |

| 3       | V <sub>SS</sub> | Negative Power Supply Voltage. This terminal must be hardwired to Terminal 12 (V <sub>SS</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4       | HD              | Horizontal Drive Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5       | MS              | Mixed Sync Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6       | С               | Capacitor Connection for R-C Genlock Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7       | MBB             | Mixed Beam Blanking Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8       | VRE             | <b>Vertical Counter Reset to First Equalizing Pulse.</b> A low level signal on this terminal resets the vertical counter to the first equalizing pulse of a field. When not in use this terminal should be connected to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                            |

| 9       | VD              | Vertical Drive Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10      | VRV             | <b>Vertical Counter Reset to First Vertical Sync Pulse.</b> A low level signal on this terminal resets the sync generator to the first vertical sync pulse of a field. For genlock operation, Terminal 10 is used as a resistor and capacitor connection for an integrator network that detects vertical sync pulses in a master sync waveform to which the sync generator is to be genlocked. R is $22k\Omega$ , and C is $0.001\mu$ F. When not in use this terminal should be connected to $V_{DD}$ .                                                                      |

| 11      | HC              | Horizontal Clamp Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12      | V <sub>SS</sub> | Negative Power Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

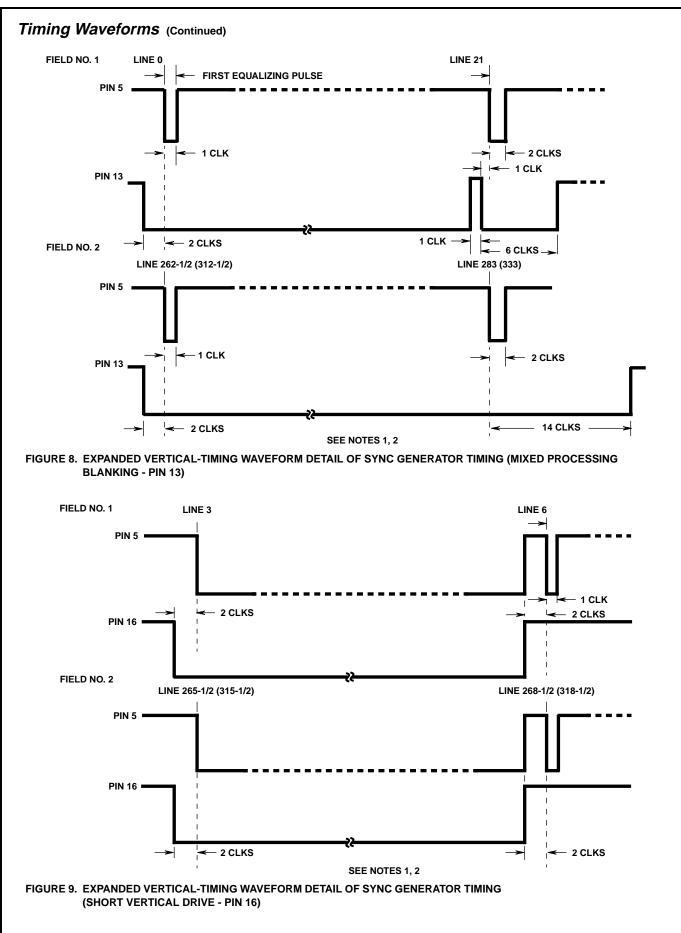

| 13      | MPB             | Mixed Processing Blanking Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14      | HPB             | Horizontal Processing Blanking Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15      | FS2             | Frame Sync Output (Odd Field). A pulse coinciding with the first equalizing pulse is produced at the beginning of every odd field.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16      | SVD             | Short Vertical Drive Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17      | VPB             | Vertical Processing Blanking Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 18      | SW              | <b>Operation Switch for 525-Line or 625-Line Raster.</b> A high level signal on Terminal 18 causes the sync generator to generate a 625-line raster. An internal pulldown resistor is connected to Terminal 18, so in the absence of an applied input to this terminal, a 525-line raster is produced.                                                                                                                                                                                                                                                                        |

| 19      | V <sub>DD</sub> | Positive Power Supply Voltage. $V_{DD}$ can be any voltage between +4 and +15 relative to $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20      | GEN             | <b>Genlock Input Composite Sync.</b> A negative going reference mixed sync waveform applied to Terminal 20 dis ables the crystal oscillator and locks the R-C genlock oscillator to the horizontal pulses of the reference sync waveform. Vertical sync detection is achieved by an R-C integrator connected from Terminal 20 to Terminal 10 (vertical reset to first vertical sync pulse). An internal pull-up resistor is connected to Terminal 20 so that in the absence of an applied input the crystal oscillator is enabled and the R-C genlock oscillator is disabled. |

| 21      | XR              | Delay, Genlock to Crystal Oscillator, Resistor and Diode Connection for Delay, Genlock to Crystal Oscil lator. Automatically turns on the crystal oscillator when the input to Terminal 20 is removed.                                                                                                                                                                                                                                                                                                                                                                        |

| 22      | RC              | <b>Resistor and Capacitor Connection for Genlock Oscillator.</b> If the genlock oscillator is not used this terminal should be connected to $V_{SS}$ . C should be 100pF, and R should be a 10k $\Omega$ potentiometer.                                                                                                                                                                                                                                                                                                                                                       |

| 23      | XIN             | Master Frequency Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 24      | R               | Resistor Connection for Genlock Oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

NOTE: 32 times horizontal frequency.

#### **Absolute Maximum Ratings**

#### **Operating Conditions**

Temperature Range

| CD22402D | ···· | 55°C to 125°C                          |

|----------|------|----------------------------------------|

| CD22402E |      | 40 <sup>o</sup> C to 85 <sup>o</sup> C |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)   | 0/ ( \  | θ <sub>JC</sub> ( <sup>o</sup> C/W)    |

|----------------------------------------|---------|----------------------------------------|

| SBDIP Package                          | 50      | 10                                     |

| PDIP Package                           | 50      | N/A                                    |

| Maximum Junction Temperature (SBDIP Pa |         | 175 <sup>0</sup> C                     |

| Maximum Junction Temperature (PDIP Pa  | ackage) | 150 <sup>0</sup> C                     |

| Maximum Storage Temperature Range      | 65      | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 1  | 0s)     | 300 <sup>0</sup> C                     |

| (SOIC - Lead Tips Only)                |         |                                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications Values at -55°C, 25°C, 125°C Apply to D Package

2. To prevent damage to the input protection circuit, input signals should never be greater than V<sub>DD</sub> nor less than V<sub>SS</sub>. Input currents must not exceed 10mA even when the power is off.

3. A connection must be provided at every input terminal. All unused inputs must be connected to V<sub>DD</sub> or V<sub>SS</sub>, whichever is appropriate.

| PARAMETER                         | SYMBOL                | TEST<br>CONDITIONS    |                        |                    |                    |                   |                    | 25 <sup>0</sup> C |       |      |       |

|-----------------------------------|-----------------------|-----------------------|------------------------|--------------------|--------------------|-------------------|--------------------|-------------------|-------|------|-------|

|                                   |                       | V <sub>O</sub><br>(V) | V <sub>DD</sub><br>(V) | -55 <sup>0</sup> C | -40 <sup>0</sup> C | 85 <sup>0</sup> C | 125 <sup>0</sup> C | MIN               | ТҮР   | МАХ  | UNITS |

| DC ELECTRICAL SPECIFIC            | ATIONS                |                       |                        |                    |                    |                   |                    |                   |       |      |       |

| Quiescent Device Current          | I <sub>DD</sub> (Max) | -                     | 5                      | -                  | -                  | -                 | -                  | 0.5               | 0.75  | 1    | mA    |

|                                   |                       | -                     | 10                     | -                  | -                  | -                 | -                  | 1.5               | 2     | 2.5  | mA    |

|                                   |                       | -                     | 15                     | -                  | -                  | -                 | -                  | 3                 | 4     | 5    | mA    |

| Output Low (Sink) Current         | I <sub>OL</sub> (Min) | 0.5                   | 5                      | 100                | 96                 | 66                | 56                 | 80                | 160   | -    | μA    |

|                                   |                       | 5                     | 5                      | 1200               | 1155               | 787               | 672                | 960               | 1920  | -    | μΑ    |

|                                   |                       | 0.5                   | 10                     | 248                | 239                | 164               | 140                | 200               | 400   | -    | μΑ    |

|                                   |                       | 10                    | 10                     | 3000               | 2868               | 1968              | 1680               | 2400              | 4800  | -    | μΑ    |

| Output High (Source) Cur-<br>rent | I <sub>OH</sub> (Min) | 4.5                   | 5                      | -100               | -96                | -66               | -56                | -80               | -160  | -    | μΑ    |

|                                   |                       | 0                     | 5                      | -1200              | -1155              | -787              | -672               | -960              | -1920 | -    | μΑ    |

|                                   |                       | 9.5                   | 10                     | -248               | -239               | -164              | -140               | -200              | -400  | -    | μΑ    |

|                                   |                       | 0                     | 10                     | -3000              | -2868              | -1968             | -1680              | -2400             | -4800 | -    | μΑ    |

| Output Voltage Low Level          | V <sub>OL</sub> (Max) | -                     | 5                      | 0.15               | 0.15               | 0.15              | 0.15               | -                 | -     | 0.15 | V     |

|                                   |                       | -                     | 10                     | 0.15               | 0.15               | 0.15              | 0.15               | -                 | -     | 0.15 | V     |

| Output Voltage High Level         | V <sub>OH</sub> (Min) | -                     | 5                      | 4.85               | 4.85               | 4.85              | 4.85               | 4.85              | -     | -    | V     |

|                                   |                       | -                     | 10                     | 9.85               | 9.85               | 9.85              | 9.85               | 9.85              | -     | -    | V     |

| Input Low Voltage                 | V <sub>IL</sub> (Max) | 0.5, 4.5              | 5                      | 1.5                | 1.5                | 1.4               | 1.4                | -                 | 2.25  | 1.5  | V     |

|                                   |                       | 1, 9                  | 10                     | 3                  | 3                  | 2.9               | 2.9                | -                 | 4.5   | 3    | V     |

| Input High Voltage                | V <sub>IH</sub> (Min) | 0.5, 4.5              | 5                      | 3.6                | 3.6                | 3.5               | 3.5                | 3.5               | 2.25  | -    | V     |

|                                   |                       | 1, 9                  | 10                     | 7.1                | 7.1                | 7                 | 7                  | 7                 | 4.5   | -    | V     |

| Input Current                     | I <sub>IN</sub> (Max) | -                     | -                      | -                  | -                  | -                 | -                  | -                 | 10    | -    | pА    |

Refer to the CD4000B Series data book 250.5 for general operating and application considerations.

# CD22402

|                                                  | SYMBOL           | TEST<br>CONDITIONS  |     |     |     |       |

|--------------------------------------------------|------------------|---------------------|-----|-----|-----|-------|

| PARAMETER (NOTE 4)                               |                  | V <sub>DD</sub> (V) | MIN | ТҮР | МАХ | UNITS |

| Output State Propagation Delay Time (50% to 50%) |                  |                     |     |     |     |       |

| Low-to-High Level                                | t <sub>PLH</sub> | 5                   | -   | 40  | 80  | ns    |

| High-to-Low Level                                | t <sub>PHL</sub> | 10                  | -   | 20  | 40  | ns    |

| Output State Transition Time (10% to 90%)        |                  |                     |     |     |     |       |

| Low-to-High                                      | t <sub>TLH</sub> | 5                   | -   | 45  | 90  | ns    |

| High-to-Low                                      | t <sub>THL</sub> | 10                  | -   | 30  | 60  | ns    |

| Input Capacitance (Per Input)                    | Cl               | -                   | -   | 5   | -   | pF    |

NOTE:

4. The characteristics given are defined for unbuffered gate in the CMOS process of the CD22402.

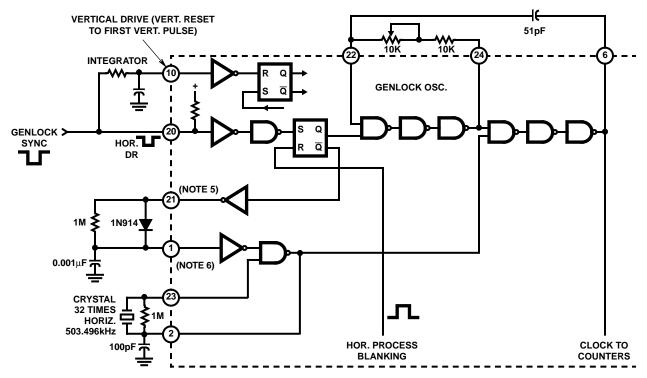

# Logic Diagram

NOTES:

5. Pin 21 high when pin 20 is high (or open).

6. Pin 1 high inhibits clock.

#### FIGURE 1. DETAIL OF THE OSCILLATOR/GENLOCK PORTION OF THE CD22402

FIGURE 7. EXPANDED VERTICAL-TIMING WAVEFORM DETAIL OF SYNC GENERATOR TIMING (VERTICAL PROCESSING BLANKING - PIN 17)

SEE NOTES 1, 2

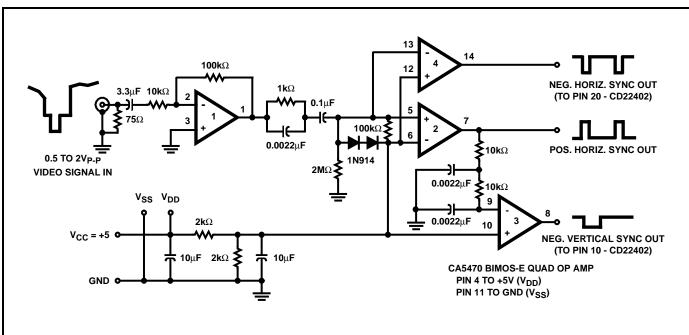

NOTE: The genlock input to pins 10 and 20 of the CD22402 are direct coupled to the output from Pins 8 and 14 of the CA5470. Refer to Application Note AN-8742 for additional information.

FIGURE 12. SUGGESTED SYNC-SEPARATOR CIRCUIT USING THE CA5470 BIMOS-E QUAD OP AMP IN THE V<sub>DD</sub> RANGE OF 4V TO 12V

All Harris Semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Harris Semiconductor products are sold by description only. Harris Semiconductor reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Harris is believed to be accurate and reliable. However, no responsibility is assumed by Harris or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Harris or its subsidiaries.

### Sales Office Headquarters

For general information regarding Harris Semiconductor and its products, call 1-800-4-HARRIS

#### NORTH AMERICA

Harris Semiconductor P. O. Box 883, Mail Stop 53-210 Melbourne, FL 32902 TEL: 1-800-442-7747 (407) 729-4984 FAX: (407) 729-5321

#### EUROPE

Harris Semiconductor Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

ASIA Harris Semiconductor PTE Ltd. No. 1 Tannery Road Cencon 1, #09-01 Singapore 1334 TEL: (65) 748-4200 FAX: (65) 748-0400