# MAPPA OTE

# **No. AN9759.1** October 1997

# Harris Multimedia

# **Signal Processing Blocks - A Tutorial**

Author: Mark E. Hazen

## Introduction

This Application Note was created to serve as a tutorial, or primer, on signal processing fundamentals relating to basic processing blocks and applications. Information is presented at a lower-than-engineering level as an aid to non-engineers such as sales and marketing personnel and customer representatives. Harris Semiconductor offers many fundamental building blocks that are needed to complete a wide range of end-products that employ analog and digital signal processing. This Application Note will help you understand these building blocks and learn how they are related to each other. To assist you in this learning process, an acronym has been created that will help you remember the blocks and a common order in which they are used - TAFMASAPDA.

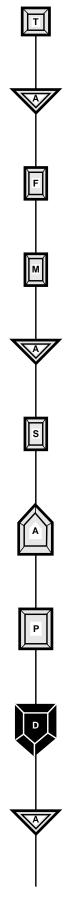

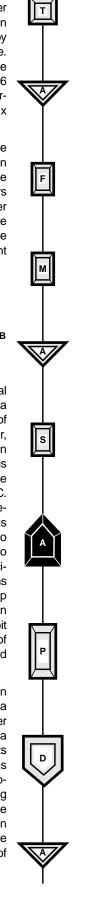

#### The TAFMASAPDA Model

#### A Mix of Analog and Digital

Signal processing systems are usually combinations of analog and digital circuits. In many cases the system begins and ends with analog circuits, and processing is done within the system using digital circuits, software, and microprocessor control. The reasons for this are fairly straightforward. Many common sources of audio and video information are analog in nature and involve the use of analog transducers to pick up or read the information. At the output end of the system, output transducers are normally driven with analog signals. Within the system,

digital processing is used instead of analog because it is not affected by temperature changes or aging of components and it allows computer control and programmability. Processing can be done more quickly and more accurately in the digital realm than in the analog.

#### **TAFMASAPDA**

An acronym-based learning aid has been developed to assist you in remembering and associating the common analog and digital blocks of a signal processing system. The acronym is TAFMASAPDA, pronounced TAF-MA-SAP'-DA.

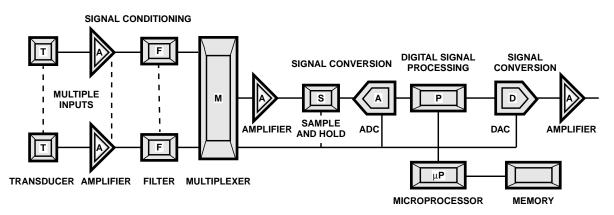

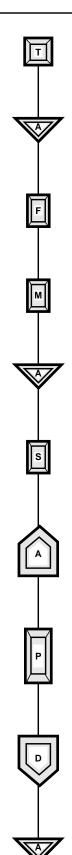

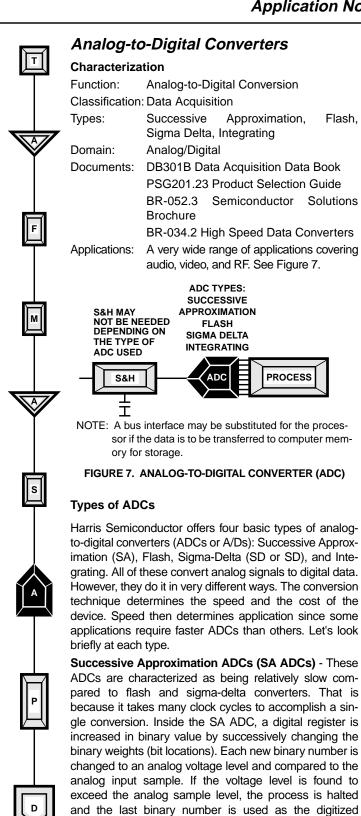

Figure 1 shows a diagram that represents TAFMASAPDA. In general terms, the transducer converts some natural parameter, such as temperature, pressure, light, sound, etc., to an electrical signal and/or vice versa. This signal is usually very weak so it must be amplified. Further signal conditioning usually involves filtering to limit the overall frequency range of the signal and reduce noise, both system noise and noise picked up by or created within the transducer. If there are many sources of analog information, a multiplexer can be used to allow each of many sources to be sampled one at a time at some repeated interval. Further amplification may be needed to provide the proper level of signal information to the sample and hold and Analog-to-Digital Converter (ADC). The sample and hold takes a quick snapshot of the analog signal and presents it to the Analog-to-digital converter.

FIGURE 1. THE TAFMASAPDA MODEL

The ADC converts the sample to a digital binary number, a process known as quantizing. Once the sample of analog signal has been converted to digital. it can be processed in what is called the digital domain. Processing usually involves some sort of compression, digital filtering, data manipulation, and/or storage using electronic memory or magnetic/optical media. The microprocessor (uP) serves as the conductor of the orchestra ensuring that all blocks work together in synchronization and, in some cases, determining what type of processing will take place. The microprocessor also serves to control output flow through the Digital-to-Analog Converter (DAC) and on through to the outside analog world. Finally, the output amplifier drives another system such as a chart recorder, audio or video power amplifier, video display, or some other device.

#### TAFMASAPDA is Only a Model!

You need to keep in mind that TAFMASAPDA is only a general model of which there are many variations. For example, a multiplexer is not needed if there is only one source of analog information. The second amplifier is not needed if the signal level is already sufficient for the sample and hold and ADC. A separate sample and hold is not needed if it is already built into the ADC or if the ADC does not require one. A simple clock circuit may take the place of the microprocessor if processing is immediate (real-time). An interface circuit may take the place of the microprocessor if the circuit is to reside under the cover of a PC. An output DAC and analog amplifier are not needed if the information is to remain in the digital domain. Nevertheless, the TAFMASAPDA model does give you a general understanding of the interaction of key players in signal processing. For that reason, we will allow TAFMASAPDA to be our escort as we explore important Harris products and applications throughout this application note.

Harris Semiconductor products, that relate to TAFMASAPDA, are amplifiers, multiplexers and related circuits, sample and hold circuits, ADCs, specialized digital processing blocks, and DACs. These will be covered in TAFMASAPDA order starting with amplifiers.

Harris Semiconductor does not offer audio/video transducers, such as microphone elements, or CCD arrays for video cameras. Also, Harris does not offer analog filters except for active filters that can be made using op-amps. Digital filters, which fall in the processing block (P) of TAFMASAPDA, are offered by Harris and will be discussed in detail later in this application note.

# High-Performance Amplifiers

#### Characterization

Function: Amplification/Buffering/Line Driving

Classification: Linear ICs

Types: Audio/Video/Broadband/Buffers

Domain: Analog

Documents: DB500.3 Linear ICs Data Book

PSG201.23 Product Selection Guide BR-052.3 Semiconductor Solutions Bro-

chure

BR-044 NA Op-Amps and Buffers Bro-

chure

Applications: Used for voltage amplification, current

gain, source/load isolation (buffering), and driving high capacitance loads (line driving) in audio and video equipment.

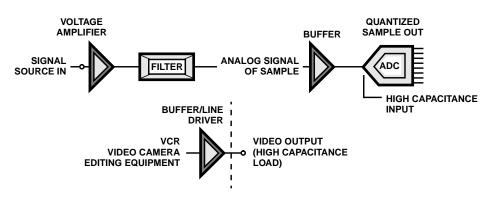

See Figure 2.

#### **Important Amplifier Parameters**

Every device has important parameters (technical specifications) that serve as figures of merit to determine the suitability of the device for a particular application. While amplifiers may seem to be very simple devices, they do have a wide range of significant parameters that are used in the selection process. We will describe the more important ones here.

Architecture - This is related to amplifier type and how it is used. Choices are: Current Feedback (CFB), Buffer (BUF), and Voltage Feedback (VFB). CFB amplifiers provide an output current that is directly related to input voltage applied to the amplifier and not at all related to the load that is connected to the amplifier. Current delivered to the load is independent of the resistance of the load. BUF amplifiers have a very low voltage gain (≤ 2) and are used to drive high-capacitance circuits and lines. BUFs are further characterized as having a high input impedance, so as not to load down a source, and low output impedance to quickly drive capacitance in some circuits and cables. Thus, the name "Buffer", because the BUF serves as a buffer between a source and a load. VFB amplifiers are used for voltage amplification and are placed where there is a need for voltage gain. However, the VFB amplifier may be operated with unity gain as a

$A_V$  = voltage amplification factor =  $V_{OUT}/V_{IN}$  = 1 and  $V_{OUT}$  =  $V_{IN}$

FIGURE 2. AMPLIFIER APPLICATIONS

-3dB Bandwidth - This is the frequency range of operation starting at 0Hz (DC) all the way up to a frequency at which the amplifiers output voltage has dropped to ~7/10 (3dB, decibels) of the output voltage that existed

at a much lower frequency. This is usually determined with the amplifier set at unity gain, but not always. A particular amplifier may have an internally established minimum gain of 10 or 2, etc., meaning the amplifier cannot be operated at gain of 1. This is indicated as the minimum Acl parameter in a selection guide or data sheet. Acl means closed-loop amplification factor.

#### Gain Flatness (±dB) -

This is the maximum variation in gain (amount of amplification) over a specified

range of frequency. For example, the HFA1145 has a gain flatness of  $\pm 0.1$ dB over a range of 0 to 75MHz. This is an important parameter especially for video amplifiers because variations in gain can cause a degradation of picture quality.

Slew Rate (V/µs) - This parameter is directly related to bandwidth. High-bandwidth amplifiers have high slew rates. Slew rate is a measure of how fast the output of the amplifier can rise from 0 to maximum output when a very fast-rising square wave is applied to its input. It is usually expressed as a rise of so many volts in a period of 1µs, the higher the better. For example, the HFA1100 has a slew rate of 2300V/µs. That means, if it were possible for the amplifier to reach 2300V at its output, which it is not, it would only take 1µs for it to do so. 2300V/µs is a very high slew rate!

**Differential Gain** - This is an indication of how well the amplifier is able to reject so-called common-mode signals. These are undesired signals picked up as noise and delivered to the amplifier with desired signals. The amplifier should amplify these undesired noise signals as little as possible. In many data sheets and selection guides, the differential gain is expressed as a percent,

i.e., 0.03%. It is desirable for this percent to be as low as possible. This is an important parameter for input amplifiers on video and medical equipment.

**Differential Phase** - In simple terms, this is an indication of the amount of phase distortion caused by the amplifier when operated in the differential, or balancedinput, mode. This parameter is expressed in degrees, the lower the better. For example, the maximum differential phase for the HFA1112 Buffer is 0.04 degrees.

**Output Current** - Op-amps and buffers are limited internally to supply a certain maximum output current to a load device. Most are in the range of 20 to 250mA (250mA = 0.250A). This is an important parameter used in selecting amplifiers and is based on the type of load the amplifier is driving into.

**Supply Voltage**  $(\pm V_{DC})$  - Many op-amps and buffers, though not all, require a positive and a negative supply voltage  $(\pm V_{DC})$ . Supply voltage specifications usually range from 4.5 to 22V.

#### **Special Amplifier Features**

Variations of Harris amplifier products includes the following special features:

- · Output Voltage Limiting

- Savings in Additional External Parts

- Internal Frequency Compensation

- Savings in Additional External Parts

- Enable Pin to Enable/Disable the Amplifier

- Adds Multiplexing Capability Without the Need for a Multiplexer

- Programmable Gain

- Additional External Components are Not Needed to Set the Gain of the Amplifier

- Multiple Amplifiers in One Package

- Savings in Cost and Board Space

Harris Semiconductor offers a wide range of high-performance op-amps and buffers featuring wide bandwidth, high slew rate, and low differential gain and phase shift.

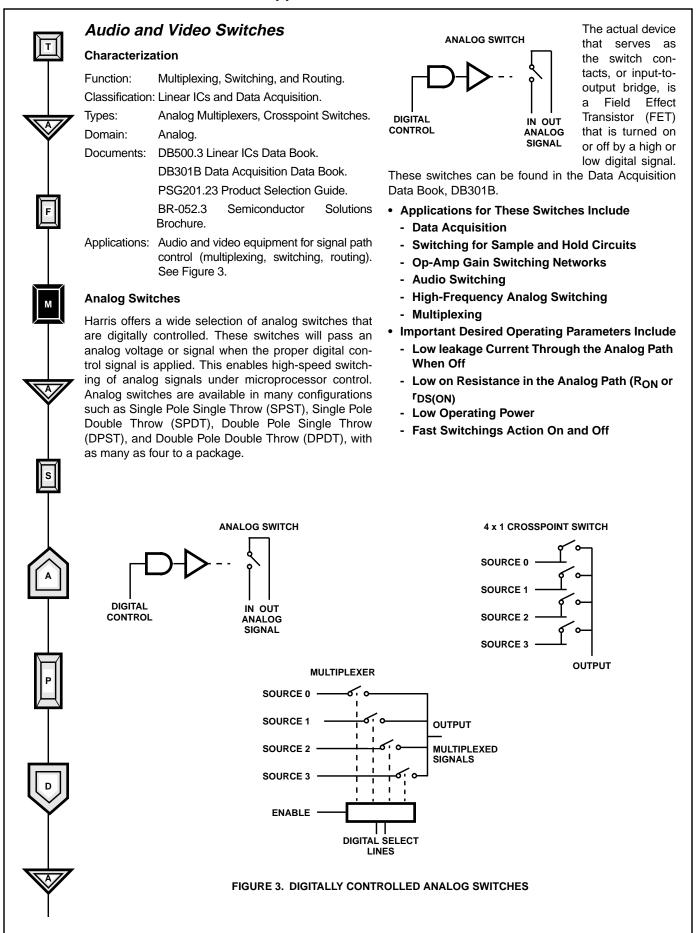

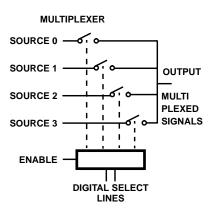

#### **Analog Multiplexers**

analog The multiplexer, often called "mux", featured in TAFthe **MASAPDA** model as the "M" block. Its purpose is to route many sources, one at a time, to the same out-

put line. Think of the word "multiplex" as meaning "many to one". A multiplexer can function as a low-switching rate source selector, such as selecting one of many audio sources to be routed to an amplifier, or it can function as a high-switching rate selector rapidly sampling many signal sources one at a time. The later is known as high-speed data acquisition and was illustrated in Figure 1 and here. Harris offers a wide selection of multiplexers from 4 to 16 channel designed for various applications. Multiplexers are found in the Data Acquisition Data Book, DB301B.

- Multiplexer Applications Include:

- Audio Source Selection

- Data Acquisition

- Medical Instrumentation

- Automatic Test Equipment

- Communication Systems

- Signal Multiplexing and Demultiplexing

- Microprocessor-Controlled Systems

Important desired operating parameters are the same as for analog switches. That's because the same switch technology is used in multiplexers.

#### **Video Crosspoint Switches**

Video crosspoint switches are used to route one of many video sources to one or more destinations, or loads. As such, they are used to make video routing equipment used in professional recording and broadcast studios. Crosspoint switches are similar in concept to the multiplexers just discussed. However, they are not intended for high-speed data acquisition switching. Also, the switch devices are video amplifiers that can be enabled and disabled, not field effect transistors that are turned on and off as in analog switches and multiplexers. Consequently, crosspoint switches are considered linear ICs and are found in the Linear ICs Data Book, DB500.3.

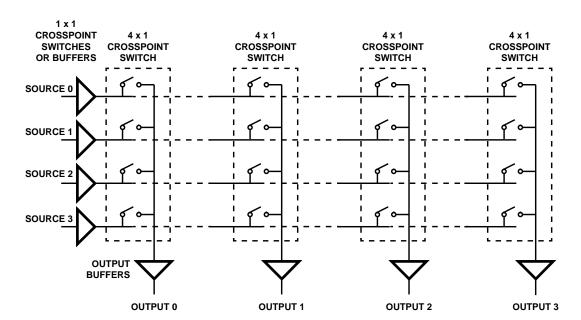

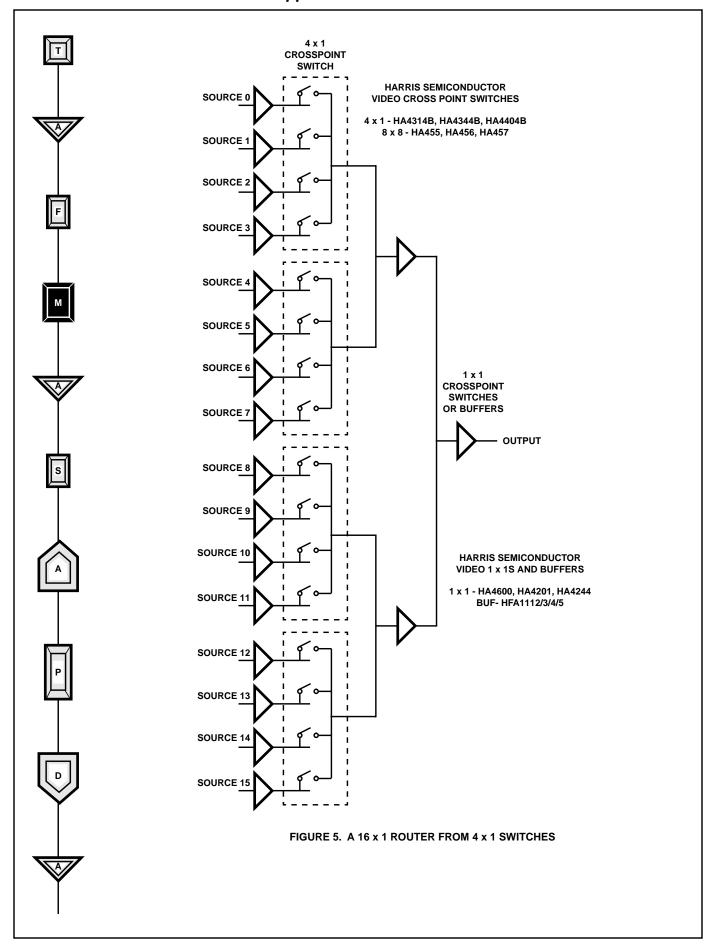

Harris crosspoint switches are available in configurations of 1 x 1, 4 x 1, and 8 x 8. A 1 x 1 crosspoint is actually a buffer amplifier with an enable control pin. It is used as a basic building block when combining 4 x 1 switches to form matrix routers such as 4 x 4, 16 x 1, etc. Examples of these are shown in Figures 4 and 5. An 8 x 8 crosspoint switch is actually a matrix, or array, that permits 8 video sources to be routed to one or all of 8 destinations. The entire array is packaged in one small quad flat pack (QFP), such as the HA455/6/7.

NOTE: Since crosspoint switches utilize video amplifiers, the important parameters are the same as those discussed earlier in the High Performance Amplification Section.

FIGURE 4. A 4 x 4 ROUTER FROM 4 x 1 SWITCHES

- Video Crosspoint Switch Applications Include:

- Professional Video Switching and Routing

- Security Video Surveillance

- Video Editing Systems

- Video Distribution Systems

- RF Switching and Routing

- Important Desired Operating Parameters Include:

- Wide Operating Bandwidth

- High Slew Rates

- Gain Flatness

- Low Differential Gain

- Low Differential Phase

- Low Power Dissipation

- High Off-State Isolation

- High Crosstalk Rejection or Low Crosstalk (Signal Leakage Between Neighboring Amplifiers on the Same Chip)

# Sample and Hold (S&H) Circuits

#### Characterization

Function: Analog Signal Sampling

Classification: Linear ICs

Types: Amplifiers

Domain: Analog

Documents: DB500.3 Linear ICs Data Book

PSG201.23 Product Selection Guide BR-052.3 Semiconductor Solutions

Brochure

Applications: Any application that involves analog-to-

digital conversion using an ADC that requires a sample and hold circuit.

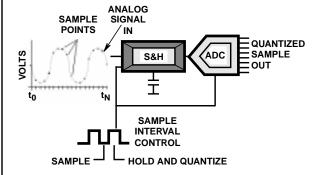

See Figure 6.

FIGURE 6. SAMPLE AND HOLD

#### **Sample and Hold Operation**

The purpose for a sample and hold circuit (S&H) is to capture voltage samples of a waveform at some sampling interval and present each sample to an

analog-to-digital converter so the sample can be quantized (converted to a binary number). As shown in Figure 6, a clock circuit or microprocessor is needed to orchestrate the process keeping the S&H and ADC synchronized. Usually, when the clock is in the low state, a sample is taken and a capacitor is quickly charged to the sample voltage level. When the clock goes into the high state, the sample is on hold (charged capacitor) and presented to the ADC for conversion. The rate at which samples are taken is usually kept at more than twice the highest analog frequency that is to be sampled. Such is the case illustrated in Figure 6. Note that the number of samples is approximately 10 samples for every analog cycle. This enables a fairly accurate dot-to-dot reproduction of the waveform when the process is reversed through digital-to-analog conversion. The S&H includes amplifiers and analog switches. Thus, desired parameters (specifications) that apply to amplifiers and switches also apply to S&H circuits.

#### **Important Sample and Hold Parameters**

Acquisition Time - This is the time required following a sample command for the output of the S&H to reach its final value. It is the minimum time that must be allowed for the S&H to function. The sample interval cannot be shorter than the acquisition time. Therefore, this is an important parameter considered in selecting a particular S&H for an application.

**Droop Rate** - While the sample is on hold, it is slowly dropping in voltage. In other words, the capacitor charge voltage is leaking off. Usually this is specified as so many microvolts per millisecond ( $\mu$ V/ms). The lower this value is, the better.

Amplifier Bandwidth - The amplifiers in the S&H must have bandwidths much greater than the highest frequency that is being sampled. This is sometimes called the Gain Bandwidth Product (GBP) which indicates the frequency at which the open-loop gain of the amplifier(s) drops to unity (1). A thorough discussion of this is beyond the scope of this application note. The higher this value is, the better.

Effective Aperture Delay Time (EADT) - This is the difference in time between two delay times. One delay time is the time for the sample switch to open once the hold command is given. The second delay time is the signal propagation delay from the analog input to the switch. If these two delays are equal, then there is effectively no delay between the hold command and the analog signal at the input. EADT should be as close to 0 as possible.

Harris Semiconductor offers a wide selection of sample and hold products. For a complete list and specifications, see the Linear ICs Data Book or Product Selection Guide. Also, there are several application notes available. These are listed at the back of the data book and on the Harris Semiconductor Web Site at: http://www.semi.harris.com/datasheets.

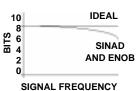

Flash,

Flash ADCs - These ADCs are very fast because they perform the analog-to-digital conversion in one step. The analog signal, or sample, is supplied to the ADC's input where it is distributed to a very large number of voltage comparator circuits. Each comparator is built upon another in a rising staircase representing tiny voltage increments. The number of comparators that are activated during a conversion depends on the voltage level of the input signal, or sample. For example, if each comparator represents a 1V step and the input sample is 4.2V, the lowest four comparator steps will be activated. The outputs of the four comparators represent a count of 4. This 4-count is then converted to a binary number egual to 4. The additional 0.2 V of the input signal is lost as a quantizing error. If we make more steps, each of lesser value, the quantizing error is reduced. More steps means there are more bits in the digital data that are being produced by the ADC. Examples: A 4-bit ADC has 15 steps (2<sup>4</sup> -1) and 15 voltage comparators. A 6-bit ADC has 63 steps (2<sup>6</sup> - 1) and 63 voltage comparators. An 8-bit ADC has 255 steps (28 - 1) and 255 voltage comparators. A 10-bit ADC has 1023 steps (2<sup>10</sup> - 1) and 1023 voltage comparators. If the maximum range of the input signal is 10V, and we use a 10-bit ADC, each tiny step will be less than 10mV (10V/1023). Therefore, each of the 1023 comparators must detect a change of less than 10mV.

Harris' high-performance flash ADCs are used for applications requiring the digitization of high-frequency and/or wide-bandwidth video, TV, and radio signals. Clock/sample rates range up to 500MHz and more.

Sigma-Delta ADCs (SD or SD) - These ADCs are very different from SA and flash ADCs. Sigma-Delta ADCs (SDs) follow the principles of delta modulation. The word "delta" means a "difference in" or a "change in" some parameter. In this case, we are interested in a change in the input signal voltage. In simple terms, SD ADCs operate as follows: The SD ADC samples the analog input signal very rapidly. With each sample, the SD is electronically asking, "Is the input signal increasing in value or is it decreasing?" If it is increasing, the SD ADC generates a binary 1. If the next sample is still increasing, another 1 is generated following the first 1. This continues until the signal is found to be decreasing at which time the SD begins to generate binary 0s and adds them to the serial string of binary 1s and 0s. If the analog signal levels out and neither increases nor decreases in voltage, the SD ADC will simply generate a stream of alternating 1s and 0s. Thus, a string of binary 1s and 0s is generated with each bit serving as a direction indicator, 1 is up and 0 is down, alternating 1s and 0s mean no change. 1-bit DAC can be used to convert this binary string back into an analog signal. Audio CD players use 1-bit DACs to convert the optically imprinted binary strings back into analog audio. Sigma-Delta ADCs are used for high-quality audio (music or voice) conversion and for high-accuracy instrumentation (laboratory equipment, medical instruments, etc.) Even though they are not as fast as flash ADCs, sigma-delta ADCs are very accurate.

(quantized) value. The register is reset and the process

is repeated for the next analog sample. The clock rate of

the ADC must be much higher than the sample rate to

allow time for these approximations to be made. Clock

rates are usually less than 1MHz. Applications include

audio/voice conversion and DC/AC signal conversion in

test instruments.

Integrating ADCs - While Harris has a wide selection of this type of ADC, it is not a choice for audio, video, or RF analog-to-digital conversion. The reason is because these ADCs are very slow due to the fact that they operate on a relatively lengthy process of charging a capacitor to the applied input voltage then counting how long it takes the capacitor to discharge. The count is stored or displayed digitally. Integrating ADCs are used in test instruments like digital multimeters. They are not intended for high-rate quantization of signals. Usually, they are only capable of 100 or less conversions per second.

#### Important ADC Parameters and Concepts

**Sample Frequency** - Sample frequency is also known as sample rate. This is the rate at which sample conversions are made. An important parameter for ADC selection is the maximum sample rate expressed as samples per second, such as, 40 Msps or 40 Ms/s.

**Bandwidth** - This is the analog input bandwidth of the ADC. At the input of, and internal to, the ADC, there is an amplifier whose bandwidth is limited. This parameter must be known for proper selection to be made. An ADC with a 10MHz bandwidth is not adequate for a 20MHz input signal.

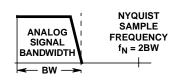

# Nyquist Frequency -

This is a minimum sample frequency (f<sub>S</sub>), or sample rate, which avoids aliasing and collects enough infor-

mation to reproduce the highest frequency sampled. The Nyquist frequency  $(f_N)$  is twice the input signal bandwidth (BW),  $(f_N = f_S = 2BW)$ .

Aliasing - This is the process of creating illegitimate frequency components that fall back within the input signal's bandwidth. Aliases are caused when the sample fre-

quency is too low, lower than the Nyquist frequency ( $f_N$ ). Aliases are recognized when the information that was digitized at too low of a rate is converted back to analog using a Digital-to-Analog Converter (DAC). In some cases, where the sampling rate is relatively low but still at or above Nyquist, a lowpass filter is used ahead of the ADC at its input to ensure that input sampling frequencies do not exceed  $f_S/2$ . This filter is called an antialiasing filter. Without its use, some high input frequencies above  $f_S/2$  would be converted to aliases that fall back into the signal BW.

**Oversampling** - This is the act of sampling at a rate higher than the Nyquist rate. Oversampling is usually desired, especially when using sigma-delta ADCs. Two-times oversampling (2X) would be twice the Nyquist rate and four times the input signal bandwidth.

**Resolution** - This is related to the number of bits for which the ADC is designed. A 10-bit ADC has a higher resolution than an 8-bit ADC. Resolution is often expressed in terms of step voltage which is calculated by dividing the number of steps into the input voltage range. For example, an 8-bit ADC has 255 steps ( $2^8$  - 1). If the input voltage range is 5V, the resolution is 5/255 = 0.0196 V per step. Another way to express resolution is as a percent. Using this same example, the resolution is  $100\% \times 1/255 = 0.392\%$ . Also,  $0.00392 \times 5V = 0.0196V$ .

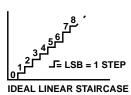

Linearity - This is a measure of the faithfulness of the input voltage-to-digital conversion at all step levels. In other words, does each step level of input voltage create the expected binary number and if these binary numbers were sent through an ideal digital-to-analog converter would they reproduce the exact steps? If a graph were drawn showing the relationship between voltage and the digitized binary numbers, would the graph be a straight line (linear)?

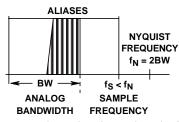

Effective Number of Bits (ENOB) - This parameter is based on the Signal-to-Noise-Plus-Distortion Ratio (SINAD) of the ADC. If the SINAD, expressed in dBs, is high, the effective number of

bits will be high. For example, assuming the input signal is making full use of the maximum input voltage range, a 10-bit ADC with a 55dB SINAD will have an ENOB of 8.8, almost 9-bits. So, because of quantization error, referred to as noise, and harmonic distortion components that make up the SINAD, this 10-bit ADC is effectively only 9-bits. The higher the SINAD and the higher the ENOB, the better the performance of the ADC. However, SINAD is inversely related to the input frequency that is being sampled. As the input frequency is made higher, SINAD decreases. If SINAD decreases, so does the ENOB. Therefore, ENOB is inversely related to input frequency. For that reason, ENOB is usually specified at a certain input frequency, as is SINAD, and graphs are available showing the ENOB/frequency relationship for each product. Interestingly, it has been shown that an 8-bit ADC can actually have the same ENOB as a 10-bit ADC at a given frequency. It depends on the quality of the products being compared and how they are used which determines the SINAD of each.

Spurious-Free Dynamic Range (SFDR) - This is an important parameter that is often used as a main criteria for selection. The range is expressed in dBs, the higher the better. SFDR shows the relationship between a recovered signal and the spurious harmonic elements that are recovered with it. "Recovered signal" means digital data created by an ADC is put through a Digital-to-Analog Converter (DAC) to return it to the analog domain. Nonlinearities in the ADC's signal path create these harmonic distortion elements that are then revealed in the recovered signal. DACs also contribute harmonic distortion elements to the process because of their signal path nonlinearities.

# Digital Filters Characterization Function: Filtering, Decimation Classification: Digital Signal Processing/One Dimensional Filters Types: FIR, Decimating, Half-band, Serial, Comb Domain: Digital Documents: DB302B Digital Signal Processing Data Book **DB314 DSP New Releases** PSG201.23 Product Selection Guide BR-052.3 Semiconductor Solutions **Brochure** Applications: A very wide range of applications covering audio, video, and RF. See Figure 8. ADC **BUS INTERFACE LOCAL BUS** MEMORY FIGURE 8. DIGITAL FILTER IMPLEMENTATION Introduction to Digital Filters Digital filters are digital signal processing blocks (the P in TAFMASAPDA) that perform many special functions based on mathematical algorithms. The algorithms can be changed under microprocessor control which changes the operating characteristics of the filter. Digital filters perform special functions by high-speed manipulation of the digital samples that are passed through the filter. These manipulations include elimination of redundant samples, resampling at a lower rate, summing and averaging samples, and multiplying samples by operational coefficients. These manipulations result in the implementation of special functions such as extremely accurate band shaping to reduce noise, antialiasing (elimination of alias frequency components in the digital domain), compensation for ADC

distortion, and elimination of redundant data. Harris

Semiconductor offers a selection of various high-qual-

ity digital filters designed for different applications.

Here we will discuss the various filter types which are

based on purpose or function.

#### Types of Digital Filters

Finite Impulse Response (FIR) - This type of filter is perhaps the most common digital filter used for video signal processing applications. Its name, finite impulse response, is descriptive of how it functions internally. A single digital sample, passed to the filter from the ADC, is the equivalent of a sharp voltage spike or impulse in the analog domain. A finite (limited) number of these digital samples (impulses) is shifted into the filter and mathematical weighting (multiplication) is performed by a finite number of coefficients programmed into the filter. The result is, the response of the filter is modified by the operation of the finite number of coefficients on the samples. FIR filters make excellent lowpass filters and post-sampling antialias filters. They are used widely in digital radio and video processing circuits.

**Decimating** - Decimating filters are actually FIR filters that are named and optimized according to their intended purpose. In this case, the purpose for the filter is decimation. Decimation is simply the removal of redundant digital samples and samples that represent noise elements. In so doing, the sample rate is effectively reduced. For example, a decimation factor of two would reduce a 10 Msps input rate to a 5 Msps output rate. The output bandwidth is reduced accordingly as well. These filters are commonly used in digital radio receiver/transmitter systems for up and down digital signal conversion in the digital domain.

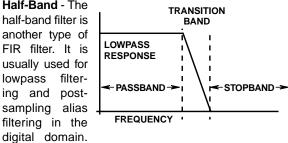

Half-Band - The half-band filter is another type of FIR filter. It is usually used for lowpass filtering and postsampling alias filtering in the

The slope of rolloff after frequency cutoff on the response curve for this filter is extremely sharp (steep) offering a narrow transition band and a high degree of out-of-band (stopband) rejection. These are frequently used in digital radio and video processing applications.

Serial - This is an FIR filter that has serial input and output data ports as opposed to parallel I/O data ports. Most digital filters have parallel input and output ports.

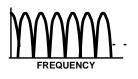

Comb - The comb filter is an FIR filter whose taps (internal sample registers) are weighted (multiplied by a coefficient) in such a way as to produce an output frequency response in the

analog domain (after the data is sent through a DAC) that is repeated bandpass responses. This is graphed

as alternating peaks and valleys, bandpass and notch responses, that look like the teeth of a comb. Thus, frequencies at specific intervals are passed and frequencies at in-between intervals are rejected. Comb filters are commonly used to separate luma and chroma signals from composite NTSC/PAL video with minimal damage to the color. That is because the luma and chroma information are interspaced or interleaved with each other in frequency. In other words, spreading a composite video signal out in frequency reveals alternating pockets of luma then chroma. The comb filter is programmed to pass the chroma pockets while rejecting the luma.

#### **Important Digital Filter Parameters and Concepts**

**Number of Bits** - This is the number of data bits the filter processes at one time. These bits may enter the filter all at once in parallel or in a serial stream.

**Clock Rate** - The clock rate is the maximum rate at which the digital data can be processed into the filter.

**Dynamic Range** - This parameter is expressed in dBs (decibels) and represents the difference in range between the maximum and minimum signals the filter can resolve. It is estimated quite closely by multiplying the number of bits by 6. For example, an 8-bit filter has a dynamic range of approximately  $8 \times 6 = 48$ dB. Often times an engineer will specify that a filter must have a dynamic range of so many dB. You can quickly calculate how many bits the filter must handle to accomplish that by simply dividing the dBs by 6. As an example, a 96-dB dynamic range requirement can be realized with a 96/6 = 16-bit filter.

**Number of Taps** - The number of taps indicates the number of input samples that a digital filter can store. Taps are digital data storage registers in which digital samples are temporarily stored. These stored samples are then acted upon, manipulated, by a set of mathematical coefficients to perform a filtering operation. A digital filter is more precise and of a higher quality if it has a large number of taps. Some digital filters have hundreds of taps.

Coefficient Length (in Bits) - A coefficient is a number that is multiplied by a variable to obtain a certain modified value. In digital filters, binary coefficients are used to modify digital samples that are stored in taps. When a digital filter is programmed, numbers of taps are selected and binary coefficients are loaded into coefficient registers to be used to modify the digital samples that are being processed. The coefficient length is simply the number of bits that are used to hold the coefficient. The coefficient length is equal to or greater than the number of data bits.

**Decimation Factor** - This is the ratio of input data rate to output data rate and is an indication of the reduction of data rate, and bandwidth, that the filter is capable of creating. In the process of decimation, unnecessary and unwanted digital data samples are removed thus, reducing the amount of data delivered to the output of the filter. It has the effect of reducing data rate, bandwidth, and provides a form of digital down-conversion (as in digital radio applications). The decimation factor for a digital filter is usually selectable over a specified range. Decimation factors can range into the thousands depending on filter design.

# Digital Video Signal Processors

#### Characterization

Function: Digital Video Signal Processing

Classification: Digital Signal Processing/Special

Function/ Video Processing

Types: Sequencer, Mixer, Buffer, Convolver,

Histogrammer

Domain: Digital

Documents: DB302B Digital Signal Processing Data

Book

**DB314 DSP New Releases**

PSG201.23 Product Selection Guide BR-052.3 Semiconductor Solutions

**Brochure**

Applications: A wide range of video signal process-

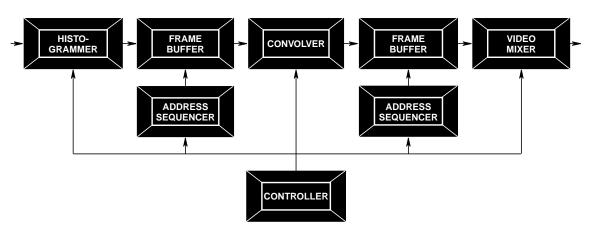

ing applications. See Figure 9.

FIGURE 9. VIDEO SIGNAL PROCESSING BLOCKS

**ORIGINAL EDGE DETECTED** FIGURE 12. EDGE DETECTION CONVOLUTION

(9 PIXELS)

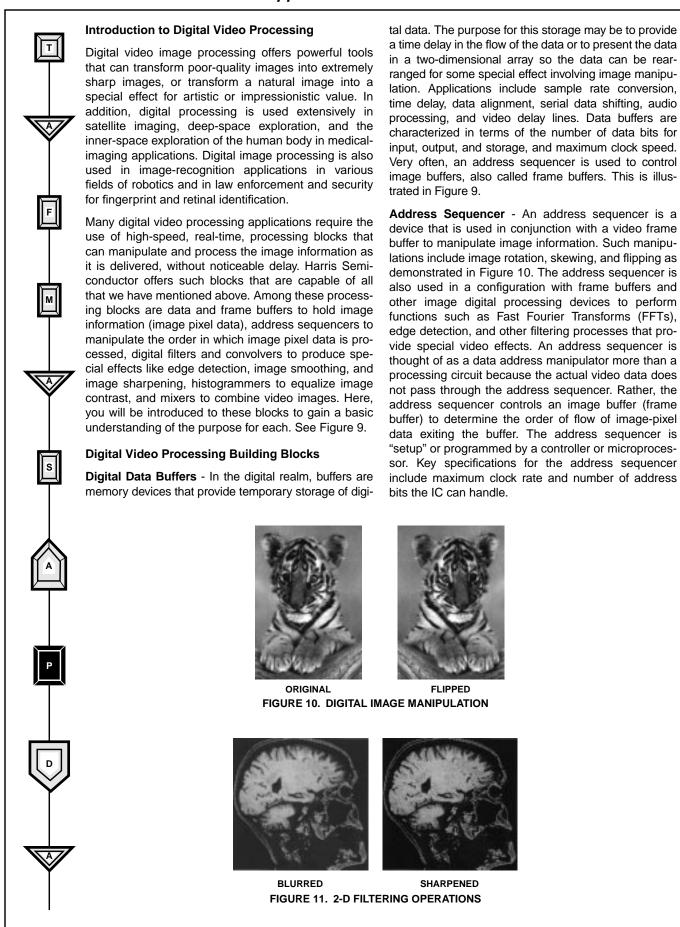

The Convolver - A convolver is a twodimensional filter. Two-dimensional filtering is referred to, in the digital world, as convolution. What is two-dimensional filtering? Two-dimensional filtering is related to two-dimensional video images

as opposed to one-dimensional streams of digital audio or digital radio signals. In 2-D filtering, a two-dimensional array of image pixel data is processed at one time. This two-dimensional array is called the kernel, a two-dimensional matrix, or array, of image pixel data. The 2-D size of the kernel the convolver can handle is directly related to its accuracy and speed of processing.

Applications for convolvers are wide and varied including the fields of robotics, medical imaging, satellite imagery, deep-space imaging, and professional video editing. Within these applications, convolvers perform image sharpening/blurring (Figure 11), edge detection (Figure 12), and other useful image enhancements. Important specifications for convolvers include maximum clock rate. input/output data word length in bits, and kernel size expressed two-dimensionally such as 3 x 3.

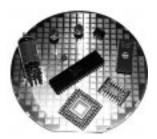

The Histogrammer - A histogrammer is a DSP device that maps an image in terms of the distribution of light and dark areas in the image. Furthermore, it can use this information to correct the contrast of the image. A poor image with very little variation of brightness can be converted to a very clear, high contrast image as demonstrated in Figure 13. Just like convolvers, there are many applications for histogrammers in the fields of medical imaging, satellite imagery, deep space probing, and professional video editing. Key parameters for histogrammers include maximum clock rate, input/output data word length in bits, and two-dimensional frame or kernel size.

Digital Video Mixer - The Digital Video Mixer is used to combine video images through averaging, summing, and multiplication of digital data. The result is a new image containing characteristics of the original source images. In this way, both natural and artificial images are produced with special effects. Important specifications for digital video mixers are maximum clock rate and input/output data word length in bits.

HISTOGRAM OF EQUALIZED IMAGE

FIGURE 13. HISTOGRAMMER IMPROVES CONTRAST

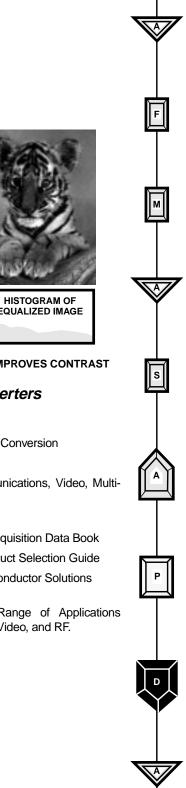

# Digital-to-Analog Converters

#### Characterization

Function: Digital-to-Analog Conversion

Classification: Data Acquisition

Types: General, Communications, Video, Multi-

Channel

Domain: Digital/Analog

Documents: DB301B Data Acquisition Data Book

PSG201.23 Product Selection Guide

**BR-052.3 Semiconductor Solutions**

**Brochure**

Applications: A Very Wide Range of Applications

Covering Audio, Video, and RF.

See Figure 14.

rate must be selected for the application.

was discussed for ADCs.

Resolution - As in ADCs, the resolution of a particular

DAC is given in terms of the number of bits the DAC is

designed to handle. A 10-bit DAC has a higher resolu-

tion than an 8-bit DAC. Resolution may also be

expressed in terms of step voltage which is calculated

by dividing the number of incremental output voltage

steps, allotted by the number of bits, into the input volt-

age range. It may also be expressed as a percent as

Linearity - This is a measure of the accuracy of the output voltage related to the binary data applied to the DAC. If a graph were drawn showing the relationship between output voltage

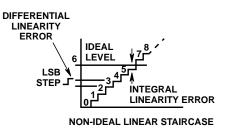

steps and applied incremented binary numbers, would the graph be a straight line (linear)? There are two types of linearity that are usually specified for a DAC, the Integral Linearity (INL) and the Differential Linearity (DNL). The Integral Linearity relates to how far off from ideal a voltage step actually is. It is expressed in terms of the least significant bit (LSB). The LSB represents the ideal individual step voltage size.

Recall this from our discussion earlier ADC resolution. The data sheet for a particular DAC mav state

that the maximum integral linearity is 1.3 LSB. That means that no step voltage on the complete full-range voltage staircase will be more than 1.3 x the height of a single ideal step away from its ideal value. In other words, if each step is 1V then, ideally, the 100th step should be right at 100V. However, the 100th step may actually be at 99.5V which is an error of 0.5V which is 1/2 step or 0.5 LSB. The differential linearity is simply a comparison of actual step size with ideal step size and is also expressed in relation to LSB. For example, if the ideal step size is 1V and it is found that no step varies more than ±0.25V, the differential linearity is 1/4 LSB or 0.25 LSB.

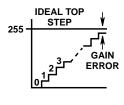

Gain Error - Gain error is the difference between the actual output voltage and the ideal output voltage at full range of the DAC. It is expressed in relation to the LSB or as a percent of the full-scale voltage range. As an example, if

the step voltage is 1V and it is an 8-bit DAC, the maximum output voltage, or full-scale voltage, ideally would be 255V. That is because an 8-bit DAC can generate 255 output voltage steps  $(2^8 - 1 = 255)$ . If the fullscale output voltage is actually 253V, there is a gain error of -2 LSB. In percent that would be 2/255 x 100% = 0.78%. Note that our use of 1-V steps and a fullscale voltage range of 255V is unrealistic but serves well for purposes of explanation. Steps are usually in the millivolts with a full-scale voltage of 5V or less.

**Settling Time** - The settling time is the time required for the output voltage, or current, of the DAC to settle to within  $\pm 0.5$  LSB after a digital input has been applied. This is expressed in microseconds or nanoseconds ( $\mu$ s or ns).

# **Acronyms**

ADC Analog-to-Digital Converter

BUF Abbreviation for Buffer

CFB Current Feedback

DAC Digital-to-Analog Converter

dB Decibel

Differential (Non-)Linearity DNL **EADT** Effective Aperture Delay Time **ENOB** Effective Number Of Bits **FFT** Fast Fourier Transform **GBP** Gain Bandwidth Product INL Integral (Non-)Linearity LSB Least Significant Bit MUX Abbreviation for Multiplexer

NOX NODICVIATION IN

QFP Quad Flat Pack

SA Successive Approximation

SFDR Spurious-Free Dynamic Range

TAFMASAPDA Transducer, Amplifier, Filte

Multiplexer, Amplifier, Sample and hold, Analog-to-digital Converter, Digital Signal Processor, Digitalto-Analog Converter, Amplifier

VFB Voltage Feedback

#### References and Resources

For Harris documents available on the web, see http://www.semi.harris.com/

Harris AnswerFAX (407) 724-7800.

- [1] Semiconductor Solutions for Multimedia, Video/Imaging, BR-052.3

- [2] Signal Processing Solutions For System Design, Foldout FO-001D

- [3] High-Speed Data Converters, BR-034.2

- [4] Analog Switches, Multiplexers and Interface Solutions. BR-064

- [5] High-Performance Op-Amps and Buffers, BR-044 NA

- [6] High-Speed Signal Processing, Harris Design Seminar, BR-043A

- [7] Harris Semiconductor Multimedia Annex Newsletter

- [8] Semiconductor Solutions for Multimedia, Video and Imaging at: http://www.semi.harris.com/multimedia/

- [9] Video/Imaging Product Listing and Application Notes http://www.semi.harris.com/datasheets/video-imaging/videoimaging\_family.html