# Gowin Software Quick Start Guide

SUG918-1.3E,2021-11-02

#### Copyright © 2021 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

**GOWIN**, **W**, Gowin, GowinSynthesis, and GOWINSEMI are trademarks of Guangdong Gowin Semiconductor Corporation and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

## **Revision History**

| Date       | Version | Description                                                                                          |

|------------|---------|------------------------------------------------------------------------------------------------------|

| 05/07/2020 | 1.0E    | Initial version published.                                                                           |

| 09/07/2020 | 1.1E    | <ul> <li>RTL schematic added.</li> <li>File encryption added.</li> <li>Tcl command added.</li> </ul> |

| 10/21/2020 | 1.1.1E  | Use GowinSynthesis $^{\ensuremath{\mathbb{R}}}$ as an example to describe synthesis.                 |

| 06/10/2021 | 1.2E    | <ul><li>Synplify Pro removed.</li><li>MIPI IP in the design modified.</li></ul>                      |

| 11/02/2021 | 1.3E    | Some descriptions updated.                                                                           |

# Contents

| Contentsi                                                                                     |

|-----------------------------------------------------------------------------------------------|

| List of Figuresiii                                                                            |

| List of Tablev                                                                                |

| 1 About This Guide1                                                                           |

| 1.1 Purpose                                                                                   |

| 1.2 Related Documents                                                                         |

| 1.3 Terminology and Abbreviations                                                             |

| 1.4 Support and Feedback                                                                      |

| 2 Introduction                                                                                |

|                                                                                               |

| 2.1 Design Flow                                                                               |

| 2.2 Design Diagram                                                                            |

| 3 Quick Start4                                                                                |

| 3.1 Create a New Project 4                                                                    |

| 3.1.1 Create a New Project4                                                                   |

| 3.1.2 Generate MIPI D-PHY IP5                                                                 |

| 3.1.3 Load File7                                                                              |

| 3.1.4 RTL Schematic                                                                           |

| 3.2 Use GowinSynthesis <sup>®</sup> to Synthesize                                             |

| 3.2.1 Configuration                                                                           |

| 3.2.2 Synthesize                                                                              |

| 3.3 Physical Constraints                                                                      |

| 3.3.1 Create New Physical Constraints                                                         |

| 3.3.2 Modify Physical Constraints                                                             |

| 3.4 Timing Constraint                                                                         |

| 3.4.1 Create New Timing Constraints       12         3.4.2 Modify Timing Constraints       15 |

| 3.4.2 Modify Timing Constraints                                                               |

| 3.5 GAO Configuration                                                                         |

| 3.5.2 Configure Standard Mode GAO                                                             |

| 3.6 GPA Configuration                                                                         |

| 3.6.1 Create GPA Config File                                                                  |

| 3.6.2 Configure GPA                                                                           |

| 3.7 Place & Route                                                                             |

| 3.7.1 Configuration                                                                           |

| 3.7.2 Run PnR                                                                                 |

| 3.8 Timing Optimization                                                                       |

| 3.8.1 Timing Analysis                                                                         |

| 3.8.2 Adjust Key Path                                                                         |

|   | 3.9 Download Bitstream                                                                                                                                                                                            | 28                                           |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 3.10 GAO Captures Data                                                                                                                                                                                            | 29                                           |

|   | 3.11 Output Files                                                                                                                                                                                                 | 30                                           |

|   | 3.11.1 Place & Route Report                                                                                                                                                                                       | 30                                           |

|   | 3.11.2 Ports and Pins Report                                                                                                                                                                                      | 30                                           |

|   | 3.11.3 Timing Report                                                                                                                                                                                              | 31                                           |

|   | 3.11.4 Power Analysis Report                                                                                                                                                                                      | 32                                           |

|   | 3.12 File Encryption                                                                                                                                                                                              | 32                                           |

|   | 3.12.1 Source File Encryption                                                                                                                                                                                     | 32                                           |

|   | 3.12.2 Simulation File Encryption                                                                                                                                                                                 | 34                                           |

| 4 | Tcl                                                                                                                                                                                                               | 36                                           |

|   |                                                                                                                                                                                                                   |                                              |

|   | 4.1 Tcl Execution                                                                                                                                                                                                 | 36                                           |

|   | 4.1 Tcl Execution<br>4.1.1 Tcl Editing Window                                                                                                                                                                     |                                              |

|   |                                                                                                                                                                                                                   | 36                                           |

|   | 4.1.1 Tcl Editing Window                                                                                                                                                                                          | 36<br>36                                     |

|   | 4.1.1 Tcl Editing Window<br>4.1.2 Tcl Command Line                                                                                                                                                                | 36<br>36<br>37                               |

|   | <ul><li>4.1.1 Tcl Editing Window</li><li>4.1.2 Tcl Command Line</li><li>4.2 Tcl Quick Start</li></ul>                                                                                                             | 36<br>36<br>37<br>37                         |

|   | <ul><li>4.1.1 Tcl Editing Window</li><li>4.1.2 Tcl Command Line</li><li>4.2 Tcl Quick Start</li><li>4.2.1 rm_file</li></ul>                                                                                       | 36<br>36<br>37<br>37<br>37                   |

|   | <ul> <li>4.1.1 Tcl Editing Window</li> <li>4.1.2 Tcl Command Line</li> <li>4.2 Tcl Quick Start</li></ul>                                                                                                          | 36<br>36<br>37<br>37<br>37<br>37             |

|   | <ul> <li>4.1.1 Tcl Editing Window</li> <li>4.1.2 Tcl Command Line</li> <li>4.2 Tcl Quick Start</li> <li>4.2.1 rm_file</li> <li>4.2.2 add_file</li> <li>4.2.3 set_file_enable</li> </ul>                           | 36<br>36<br>37<br>37<br>37<br>37<br>38       |

|   | <ul> <li>4.1.1 Tcl Editing Window</li> <li>4.1.2 Tcl Command Line</li> <li>4.2 Tcl Quick Start</li> <li>4.2.1 rm_file</li> <li>4.2.2 add_file</li> <li>4.2.3 set_file_enable</li> <li>4.2.4 set_option</li> </ul> | 36<br>36<br>37<br>37<br>37<br>37<br>38<br>38 |

# **List of Figures**

| Figure 2-1 MIPI Design Diagram                           | . 3  |

|----------------------------------------------------------|------|

| Figure 3-1 Create a New Project                          | . 4  |

| Figure 3-2 Project Directory                             | . 5  |

| Figure 3-3 MIPI RX Advance Configuration                 | .5   |

| Figure 3-4 MIPI RX Advance IP Directory                  | . 6  |

| Figure 3-5 MIPI TX Configuration                         | . 7  |

| Figure 3-6 Design Window                                 | .7   |

| Figure 3-7 Load Files                                    | . 8  |

| Figure 3-8 Synthesis Configuration                       | . 9  |

| Figure 3-9 Attributes and Instructions of GowinSynthesis | . 9  |

| Figure 3-10 Synthesis Completed                          | . 10 |

| Figure 3-11 gwsynthesis Directory                        | . 10 |

| Figure 3-12 I/O Constraints                              | . 11 |

| Figure 3-13 Physical Constraints Display                 | . 12 |

| Figure 3-14 Clock Constraints                            | . 13 |

| Figure 3-15 Timing Report Constraints                    | . 14 |

| Figure 3-16 Timing Constraints Display                   | . 14 |

| Figure 3-17 Create GAO Config File                       | . 15 |

| Figure 3-18 Trigger Options Configuration                | . 16 |

| Figure 3-19 Capture Options Configuration                | . 16 |

| Figure 3-20 GAO Config Files                             | . 17 |

| Figure 3-21 Create GPA Config File                       | . 18 |

| Figure 3-22 General Setting Configuration                | . 19 |

| Figure 3-23 Rate Setting Configuration                   | . 20 |

| Figure 3-24 Clock Setting Configuration                  | . 21 |

| Figure 3-25 GPA Config Files                             | . 22 |

| Figure 3-26 Place & Route Configuration                  | . 23 |

| Figure 3-27 Place & Route Completed                      | . 23 |

| Figure 3-28 PnR Directory                                | . 24 |

| Figure 3-29 GAO Directory                                | . 25 |

| Figure 3-30 Max. Frequency                               | . 25 |

| Figure 3-31 Timing Path                                  | . 26 |

| Figure 3-32 Timing Path Highlighted                      |      |

| Figure 3-33 Timing Path Adjusted                         | . 27 |

| Figure 3-34 Programmer                                   | . 28 |

| Figure 3-35 GAO Interface                                | . 29 |

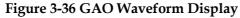

| Figure 3-36 GAO Waveform Display                         |      |

| Figure 3-37 Place & Route Report                         |      |

| Figure 3-38 Ports & Pins Report                          | . 31 |

| Figure 3-39 Timing Report                                |      |

| Figure 3-40 Power Analysis Report                        | . 32 |

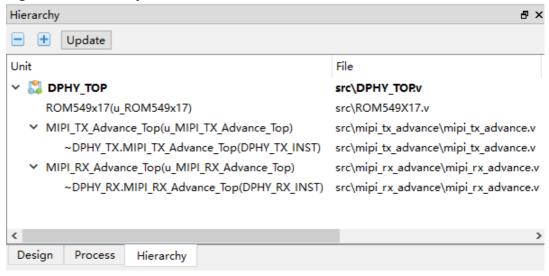

| Figure 3-41 Hierarchy Window            | . 33 |

|-----------------------------------------|------|

| Figure 3-42 Pack User Design Dialog Box | . 34 |

| Figure 4-1 Tcl Editing Window           | . 36 |

| Figure 4-2 Tcl Command Line             | . 36 |

| Figure 4-3 Tcl Script File              | . 37 |

# List of Table

# **1** About This Guide

## 1.1 Purpose

This manual uses MIPI as an example to introduce Gowin Software and aims to help you get familiar with the usage and improve the design efficiency.

# **1.2 Related Documents**

You can find the related documents at <u>www.gowinsemi.com</u>:

- <u>SUG100</u>, Gowin Software User Guide

- <u>SUG935</u>, Gowin Design Physical Constraints User Guide

- <u>SUG101</u>, Gowin Design Timing Constraints User Guide

- <u>SUG114</u>, Gowin Analyzer Oscilloscope User Guide

- <u>SUG282</u>, Gowin Power Analyzer User Guide

- <u>SUG502</u>, Gowin Programmer User Guide

- <u>SUG550</u>, GowinSynthesis User Guide

- <u>SUG755</u>, Gowin HDL Schematic Viewer User Guide

# **1.3 Terminology and Abbreviations**

Table 1-1 shows the abbreviations and terminology used in this manual.

**Table 1-1 Terminology and Abbreviations**

| Terminology and Abbreviations | Meaning                     |

|-------------------------------|-----------------------------|

| PnR                           | Place & Route               |

| GAO                           | Gowin Analyzer Oscilloscope |

| GPA                           | Gowin Power Analyzer        |

| AO Core                       | Analysis Oscilloscope Core  |

# 1.4 Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: www.gowinsemi.com

E-mail: support@gowinsemi.com

# 2 Introduction

# 2.1 Design Flow

Gowin Software is available in Windows and Linux. It supports GUI running mode and commands running mode. Take the GUI running mode in Windows and MIPI design as an instance to introduce quick start of Gowin Software.

The design uses FloorPlanner to add physical constraints, uses Timing Constraints Editor to add timing constraints, uses GAO to add GAO config file and to capture data, GPA to add GPA config file, and Programmer to download bitstream.

# 2.2 Design Diagram

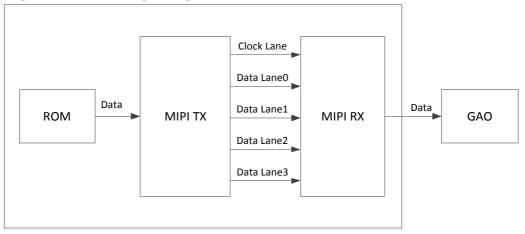

Gowin MIPI D-PHY TX RX IP applies to the serial display interface and serial camera interface for receiving or transmitting the image or video data. MIPI D-PHY provides its physical layer definition.

The design integrates MIPI RX Advance IP and MIPI TX Advance IP. pROM provides data for MIPI TX Advance. MIPI TX Advance transmits data and MIPI RX Advance receives data. GAO captures the data received by MIPI RX Advance to verify MIPI RX Advance and MIPI TX Advance. The design diagram is as shown in Figure 2-1.

#### Figure 2-1 MIPI Design Diagram

# **3** Quick Start

## 3.1 Create a New Project

#### 3.1.1 Create a New Project

Open Gowin Software and click "Start Page > Quick Start > New Project" to create a new project named as MIPI\_RX\_TX\_Advance. The device selected is as shown in Figure 3-1.

- Series: GW1N

- Device: GW1N-9

- Package: PBGA256

- Speed: C6/I5

- Part Number: GW1N-LV9PG256C6/I5

Click "Next" until the project creation completed. For the details, please refer to <u>SUG100</u>, Gowin Software User Guide.

#### Figure 3-1 Create a New Project

| Project Name<br>Select Device<br>Sunmary | Specify a target device for y | our project |                             |         |         |     |      |     |

|------------------------------------------|-------------------------------|-------------|-----------------------------|---------|---------|-----|------|-----|

| -                                        | Series: GW1N                  |             | <ul> <li>Device:</li> </ul> | GW1N-9  |         |     |      | •   |

|                                          |                               |             | Package:                    | PBGA256 |         |     |      | •   |

|                                          |                               |             | Speed:                      | C6/I5   |         |     |      | •   |

|                                          | Part Number                   | Device      | Package                     | Speed   | Voltage | ю   | LUT  | FF  |

|                                          | GW1N-LV9PG256C6/I5            | GW1N-9      | PBGA256                     | C6/I5   | LV      | 207 | 8640 | 648 |

|                                          | GW1N-UV9PG256C6/I5            | GW1N-9      | PBGA256                     | C6/I5   | UV      | 207 | 8640 | 648 |

|                                          | <                             |             |                             |         |         |     |      |     |

After the project is created, the impl and src folders are generated under the project creation path, as shown in Figure 3-2. impl contains synthesis and PnR files and src contains the source files.

#### **Figure 3-2 Project Directory**

| Name                         | Date modified   | Туре        | Size |

|------------------------------|-----------------|-------------|------|

| impl                         | 6/10/2021 17:17 | File folder |      |

| src                          | 6/10/2021 17:17 | File folder |      |

| 🐝 MIPI_RX_TX_Advance.gprj    | 6/10/2021 17:07 | GPRJ File   | 1 KB |

| MIPI_RX_TX_Advance.gprj.user | 6/10/2021 17:17 | USER File   | 3 KB |

#### 3.1.2 Generate MIPI D-PHY IP

Click "Tools > IP Core Generator" to open the IP Core Generator window. Double-click "Interface and Interconnect > MIPI RX Advance" to open the IP Customization dialog box to configure as required. The MIPI RX Advance configuration in this design is shown in Figure 3-3. Then click "OK" to generate MIPI RX Advance IP.

Figure 3-3 MIPI RX Advance Configuration

| Options                         |                             |

|---------------------------------|-----------------------------|

| MIPI D-PHY Mode: () 1:8 () 1:16 |                             |

| CLK IO TYPE: O TLVDS            |                             |

| D-PHY Lane0 Lane0 IO TYPE:      | ELVDS -                     |

| ☑ D-PHY Lane1 Lane1 IO TYPE:    | ELVDS 🔻                     |

| ☑ D-PHY Lane2 Lane2 IO TYPE:    | ELVDS 🔻                     |

| ☑ D-PHY Lane3 Lane3 IO TYPE:    | ELVDS 🔻                     |

| Data0 Before Lane Alignment     | HS DATA0 IO Delay Value 0 🔹 |

| Data1 Before Lane Alignment     | HS DATA1 IO Delay Value 0   |

| Data2 Before Lane Alignment     | HS DATA2 IO Delay Value 0   |

| Data3 Before Lane Alignment     | HS DATA3 IO Delay Value 0   |

| LP mode on clock lane           |                             |

| LP mode on data lane 0          | LP mode on data lane 1      |

| LP mode on data lane 2          | LP mode on data lane 3      |

| ✓ Turns on byte alignment       | ☑ Turns on lane alignment   |

| D-PHY RX using external Clock   |                             |

| Generation Config               |                             |

| Disable I/O Insertion           |                             |

| L                               |                             |

After generation, IP design files and simulation files are generated

under the IP creation path, as shown in Figure 3-4.

- .v file is an IP design file, encrypted.

- \_tmp.v is an IP design template file.

- .vo file is an IP simulation model file, unencrypted.

- .ipc file is an IP configuration file. The user can load the file to modify the configuration.

- temp contains the files required to generate the IP.

- The doc, model, sim, and tb contain the simulation files: readme text, simulation model, simulation script, and testbench.

#### Note!

At present, for some IPs, the created path still generates doc, model, sim, and tb folders, indicating readme text, simulation model, simulation script, and testbench simulation file. The IP directory is subject to IP Core Generator in use.

#### Figure 3-4 MIPI RX Advance IP Directory

| Name                    | Date modified   | Туре        | Size   |  |

|-------------------------|-----------------|-------------|--------|--|

| temp                    | 6/10/2021 17:17 | File folder |        |  |

| 📓 mipi_rx_advance.ipc   | 6/10/2021 13:42 | IPC File    | 1 KB   |  |

| 📓 mipi_rx_advance.v     | 6/10/2021 13:43 | V File      | 427 KB |  |

| 📓 mipi_rx_advance.vo    | 6/10/2021 13:43 | VO File     | 734 KB |  |

| 🎽 mipi_rx_advance_tmp.v | 6/10/2021 13:43 | V File      | 2 KB   |  |

|                         |                 |             |        |  |

Double-click MIPI TX Advance to open the IP Customization dialog box to configure as required. The MIPI TX Advance configuration in this design is shown in Figure 3-5. Then click "OK" to generate MIPI TX Advance IP.

Figure 3-5 MIPI TX Configuration

| Options                                       |

|-----------------------------------------------|

| MIPI D-PHY Mode: () 8:1 () 16:1               |

| D-PHY CLK CLK IO TYPE: ELVDS -                |

| ☑ D-PHY Lane0 Lane0 IO TYPE: ELVDS ▼          |

| ☑ D-PHY Lane1 Lane1 IO TYPE: ELVDS ▼          |

| ☑ D-PHY Lane2 Lane2 IO TYPE: ELVDS ▼          |

| ☑ D-PHY Lane3 Lane3 IO TYPE: ELVDS ▼          |

| LP mode on clock lane                         |

| LP mode on data lane 0 LP mode on data lane 1 |

| LP mode on data lane 2 LP mode on data lane 3 |

| DPHY TX with Internal PLL                     |

| PLL Reference Clock: 50MHz                    |

| Generation Config                             |

| Disable I/O Insertion                         |

After MIPI RX Advance and MIPI TX Advance IPs generated, the Design window is as shown in Figure 3-6.

Figure 3-6 Design Window

| Design                                | Design 🗗 🕹                            |           |  |  |

|---------------------------------------|---------------------------------------|-----------|--|--|

| ✓                                     |                                       |           |  |  |

| @ GW1N-LV9PG256C6/I5                  |                                       |           |  |  |

| × 📂                                   | 🗸 🗁 Verilog Files                     |           |  |  |

|                                       | src\mipi_rx_advance\mipi_rx_advance.v |           |  |  |

| src\mipi_tx_advance\mipi_tx_advance.v |                                       |           |  |  |

|                                       |                                       |           |  |  |

|                                       |                                       |           |  |  |

|                                       |                                       |           |  |  |

| Design                                | Process                               | Hierarchy |  |  |

#### 3.1.3 Load File

In order to test MIPI RX Advance and MIPI TX Advance, some design files need to be loaded or created, as shown in Figure 3-7.

| Design |                                                           | 8 ×                                                                             |

|--------|-----------------------------------------------------------|---------------------------------------------------------------------------------|

| -      | GW1N-LV9<br>Verilog File<br>src\DPH<br>src\mip<br>src\mip | dvance - [E:\IDE\MIPI_RX_TX_Advance\MIPI_RX_TX_Advance.gprj]<br>PG256C6/I5<br>s |

| Design | Process                                                   | Hierarchy                                                                       |

#### **Figure 3-7 Load Files**

#### 3.1.4 RTL Schematic

After the source file is loaded, you can view the design schematic by clicking "Tools > Schematic Viewer" to help you better understand the logic. For details, see <u>SUG755</u>, Gowin HDL Schematic Viewer User Guide.

# 3.2 Use GowinSynthesis® to Synthesize

#### 3.2.1 Configuration

Select "Process > Synthesize > Configuration" to open Configurations dialog box. For details, refer to <u>SUG550</u>, GowinSynthesis User Guide.

The top module/entity is DPHY\_TOP, as shown in Figure 3-8.

| Synthesize         |                                    |

|--------------------|------------------------------------|

| General            |                                    |

| Synthesis Tool:    | <ul> <li>GowinSynthesis</li> </ul> |

| Top Module/Entity: | DPHY_TOP                           |

| Include Path:      |                                    |

| GowinSynthesis     |                                    |

| Verilog Language:  | System Verilog 2017 🔻              |

| VHDL Language:     | VHDL 1993 -                        |

| Looplimit:         | 2000                               |

| Disable Insert P   | ad                                 |

| Ram R/W Check      | د                                  |

| DSP Balance        |                                    |

| Show All Warnin    | gs                                 |

Figure 3-8 Synthesis Configuration

In addition, you can add some attributes and instructions to the source file to control synthesis. For the details, see <u>SUG550</u>, GowinSynthesis User Guide. As shown in Figure 3-9, in this design, a specific net is retained without optimization during the synthesis by using the/\* synthesis syn\_keep=1 \*/ attribute.

#### Figure 3-9 Attributes and Instructions of GowinSynthesis

| 417 | `ifdef GEN_MIPI_RX_16                                              |

|-----|--------------------------------------------------------------------|

| 418 | reg [63:0] data_in;                                                |

| 419 | reg [15:0] data0, data1, data2, data3;                             |

| 420 | reg [15:0] dout, dout1;                                            |

| 421 | <pre>reg [15:0] data_cntr;</pre>                                   |

| 422 | <pre>reg hactive_flag_RX;</pre>                                    |

| 423 |                                                                    |

| 424 | <pre>wire [1:0] lp_clk_out,lp_data0_out;</pre>                     |

| 425 | <pre>wire [1:0] lp_data1_out,lp_data2_out,lp_data3_out;</pre>      |

| 426 |                                                                    |

| 427 | <pre>wire [15:0] data_out3, data_out2, data_out1, data_out0;</pre> |

| 428 | <pre>wire D0_delay,D1_delay,D2_delay,D3_delay;</pre>               |

| 429 | reg [63:0] data out reg;                                           |

| 430 | <pre>wire clk_byte_out/* synthesis syn_keep=1 */;</pre>            |

| 431 | wire sclk_tx ;                                                     |

| 432 | `endif                                                             |

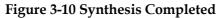

## 3.2.2 Synthesize

After synthesis configuration, you can start to synthesize.

Double-click "Synthesize" in Process window to synthesize, as shown in Figure 3-10. When the icon changes to ", you can double-click Synthesis Report to view the report and double-click Netlist File to view the netlist file.

| Process                     | 8 | x |

|-----------------------------|---|---|

| 📗 Design Summary            |   |   |

| 4 厚 User Constraints        |   |   |

| 📕 FloorPlanner              |   |   |

| 🔀 Timing Constraints Editor |   |   |

| 🔺 🥝 Synthesize              |   |   |

| Synthesis Report            |   |   |

| Netlist File                |   |   |

| 🔺 🔡 Place & Route           |   |   |

| 🧾 Place & Route Report      |   |   |

| 🧾 Timing Analysis Report    |   |   |

| 🧾 Ports & Pins Report       |   |   |

| Power Analysis Report       |   |   |

| 📲 Program Device            |   |   |

|                             |   |   |

| Design Process Hierarchy    |   |   |

| nezrku trocezz mierarcuh    |   |   |

After synthesis, the gwsynthesis folder is generated under the \impl path. The folder contains all the files and folders generated in synthesis, as shown in Figure 3-11.

#### Figure 3-11 gwsynthesis Directory

| Name                                 | Date modified   | Туре            | Size   |

|--------------------------------------|-----------------|-----------------|--------|

| MIPI_RX_TX_Advance.log               | 6/10/2021 15:09 | LOG File        | 4 KB   |

| MIPI_RX_TX_Advance.prj               | 6/10/2021 15:09 | PRJ File        | 2 KB   |

| MIPI_RX_TX_Advance.vg                | 6/10/2021 15:09 | VG File         | 464 KB |

| MIPI_RX_TX_Advance_syn.rpt.html      | 6/10/2021 15:09 | 360 se HTML Doc | 29 KB  |

| MIPI_RX_TX_Advance_syn_resource.html | 6/10/2021 15:09 | 360 se HTML Doc | 3 KB   |

| MIPI_RX_TX_Advance_syn_rsc.xml       | 6/10/2021 15:09 | XML Document    | 1 KB   |

# **3.3 Physical Constraints**

After synthesis, you can use FloorPlanner or write manually to add physical constraints. In this design, FloorPlanner is selected. For more details, please refer to the <u>SUG935</u>, Gowin Design Physical Constraints User Guide

#### 3.3.1 Create New Physical Constraints

Click "Process > User Constraints > FloorPlanner" to open FloorPlanner, which supports I/O, Primitive, and Group physical constraints. This design only adds I/O constraints and uses it as an instance.

You can create I/O constraints in I/O Constraints window. Drag the port row to be constrained in the Netlist or I/O Constraints window to a specific location in the Package View or Chip Array view. After finished, the port location displays in the IOB, as shown in Figure 3-12.

| Netlist      |            |               | ₽×       | Chip Ar   | ray 🗈 | I          | ackas            | ge Vi | ew 🗵 |    |         |   |        |    |       |    |    |     |      |      |    |

|--------------|------------|---------------|----------|-----------|-------|------------|------------------|-------|------|----|---------|---|--------|----|-------|----|----|-----|------|------|----|

| Y 📓 DPH      | Y_TOP      |               | ^        |           | 1     | 2 3        | 4                | 5     | 6    | 7  | 8       | 9 | 10     | 11 | 12    | 13 | 14 | 15  | 16   |      | ^  |

| Y 🛅 P        | orts(26)   |               |          | A         | ≱     | <b>(</b>   |                  |       | Þ    | Þ  | Þ       | 8 | Þ      | Þ  | Þ     | Þ  | Þ  | Þ   | ≱    | Δ    |    |

| 1            | HS_CLK_    | -             |          |           |       | •          |                  |       |      | *  |         | * |        |    |       |    |    | •   |      | A    |    |

| 1            | HS_CLK_    | -             |          | В         | Ð     | ÷          | ₽₽               | •     | Ð    | ₽  | Ð       | Ð | Ð      | Ð  | Ð     | Ð  | Ð  | ÷   | ٩    | в    |    |

| 7            | HS_DATA    |               |          | С         | ₽     |            | - Đ              | Ð     | Ð    | Ð  | Ð       | Ð | Ð      | Ð  | Ð     | Þ  | ÷  | Ð   | Ð    | С    |    |

| 7            | HS_DATA    |               |          | D         | Ð     | Т          | <mark>ي ب</mark> | ≑     | Ð    | Ð  | Þ       | Ð | Þ      | Ð  | ≱     | ÷  | Ð  | Þ   | Ð    | D    |    |

| 1            | _          |               |          | Е         | Ð     | e t        |                  | 1     | Ð    | Ð  | 6       | Ð | Ð      |    | ÷     | \$ |    | Ð   |      | Е    |    |

| 1            |            |               |          |           |       |            |                  | =     |      |    |         | - |        |    | _     |    |    |     |      |      |    |

| 1            |            |               |          | F         | Ð     | Ð          | Ð                | Ð     | ÷    | Ð  | Ð       | Ð | Ð      | ÷  | ۲     | ٢  | ٢  | ٢   | ٢    | F    |    |

| 7            | HS_DATA    |               |          | G         | Ð     |            | ≥ €              |       | Ð    | ≯  | ≉       | ≯ | ≯      | Ð  | Ð     | Ð  | ٩  | ٩   | ۲    | G    |    |

| 1            |            |               |          | н         | Ð     | Т          | ● €              |       | Ð    | ≉  | ÷       | ÷ | ≉      | Ð  | Ð     | ٢  | Þ  | ۲   | ٩    | н    |    |

| 1            | HS_DATA    | N0_RX_N       |          | J         | ⊅     | Ðđ         | Ð                | Ð     | Ð    | ≉  | ÷       | ÷ | ≯      | Þ  | Ð     | Ð  |    |     | 6    | J    |    |

| 1            |            |               |          | к         |       |            |                  |       |      | -  | -<br>\$ | ≱ | ,<br>≯ | Ð  |       | Ð  |    |     |      | к    |    |

| 1            | clkx2x4    | TYD           |          |           | Ð     | € 6        |                  |       | •    | \$ |         |   |        |    |       |    | -  |     | 2    |      |    |

|              | HS_CLK_    | -             |          | L         | Ð     | •          | ≥ €              | (D)   | ÷    | ₽  | Ð       | Ð | Ð      | ÷  | ۲     | Ð  | Ð  | Ð   | ۲    | L    |    |

|              |            | -             |          | М         |       | • (        | ≥ \$             | ÷     | Ð    | Ð  | Ð       | Ð | Ð      | Ð  | ÷     |    | Ð  | Ð   | ۲    | М    |    |

|              | HS_DATA    |               |          | N         |       | <b>(</b> ) | <mark>ي ا</mark> | ≱     | Ð    | Ð  | Ð       | Þ | Ð      | Ð  | ≱     | ÷  | Ð  | Ð   | Ð    | N    |    |

| 1            | HS_DATA    |               |          | Р         | 6     |            |                  |       |      | Ð  | A       | A |        |    |       | Ð  | 1  | Ð   |      | Р    |    |

| -            | HS_DATA    |               |          |           |       |            |                  |       |      |    |         |   |        |    |       |    | =  |     |      |      |    |

| -            | HS DATA    |               |          | R         | 2     | ÷          |                  | ₽     |      | Ð  | Ð       | Ð | ۲      |    | Ð     | Ð  | Ð  | ÷   | Ð    | R    |    |

|              | HS_DATA    |               |          | Т         | ≯     |            | Ð                |       |      | Ð  | Ð       | Ð | Ð      | Ð  | Ð     | Ð  | Ð  | Ð   | ≯    | Т    |    |

|              | HS DATA    |               | <b>v</b> |           | 1     | 2 3        | 4                | 5     | 6    | 7  | 8       | 9 | 10     | 11 | 12    | 13 | 14 | 15  | 16   |      | ~  |

| Summary      | Netlist    |               |          | <         |       |            |                  |       |      |    |         |   |        |    |       |    |    |     |      |      | >  |

| E/O Constrai | nts        |               |          |           |       |            |                  |       |      |    |         |   |        |    |       |    |    |     |      |      | ð× |

| P            | ort        | Direction     |          | Diff Pair |       | Lo         | ocatio           | on    |      | В  | ank     |   |        | Ex | clusi | ve |    | 10  | о ту | pe   | ^  |

| 1 HS_CLK_    | RX_P       | input         | H        | S_CLK_RX  | N     | к          | 14,K1            | 5     |      |    | 0       |   |        | F  | alse  |    |    | LVC | MOS  | S33D |    |

| 2 HS_CLK_    | TX_P       | output        | н        | S_CLK_TX  | N     | I          | 2,M1             |       |      |    | 2       |   |        | F  | alse  | •  |    | LVC | MOS  | S33D |    |

| 3 HS_DATA    | A0_RX_P    | input         | HS       | DATA0_R   | X_N   | J          | I5,K1            | 6     |      |    | 0       |   |        | F  | alse  | ,  |    | LVC | MOS  | S33D |    |

| 4 HS_DATA    | AO TX P    | output        | HS       | DATA0 T   | хN    | ſ          | 13,N             | 1     |      |    | 2       |   |        | F  | alse  | ,  |    | LVC | MOS  | S33D |    |

| 5 HS_DATA    | A1 RX P    | input         | HS       | DATA1_R   | XN    | J          | 16,J1            | 4     |      |    | 0       |   |        | F  | alse  | •  |    | LVC | MOS  | S33D | +  |

| 6 HS_DATA    |            | output        | -        | DATA1_T   | -     |            | R1,P2            |       |      |    | 2       |   |        | F  | alse  | •  |    | LVC | MOS  | S33D |    |

| 7 HS DATA    |            | input         | -        | DATA2 R   | -     |            | 15,G1            |       |      |    | 0       |   |        |    | alse  |    | -  |     |      | 533D | +  |

|              |            |               |          |           |       |            |                  |       |      |    | -       |   |        |    |       |    |    |     |      |      |    |

| <            |            |               |          |           |       |            |                  |       |      |    |         |   |        |    |       |    |    |     |      |      | >  |

| Message      | I/O Constr | raints Primit | ive C    | onstraint | s     |            |                  |       |      |    |         |   |        |    |       |    |    |     |      |      |    |

Figure 3-12 I/O Constraints

After constraints finished, click "Save" to generate physical constraints

| files as shown ir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Figure 3-13 Physic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | cal Constraints Display |

| Design     Image: Section of the section | <pre></pre>             |

| Design Process Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MIPI_RX_TX_Advance.cst  |

In PnR, if there is no physical constraints file, the PnR will be automatically performed. If there is a physical constraint file, the PnR will be performed according to the physical constraints file.

### 3.3.2 Modify Physical Constraints

After physical constraints files generated, you can modify the constraints by FloorPlanner. Click "Save" to finish.

# 3.4 Timing Constraint

After synthesis, you can use Timing Constraints Editor or write manually to add timing constraints. In this design, Timing Constraints Editor is selected. For more details, please refer to <u>SUG101</u>, Gowin Design Timing Constraints Guide.

### 3.4.1 Create New Timing Constraints

Click "Process > User Constraints > Timing Constrains Editor" to open Timing Constrains Editor, which supports clock, I/O and timing report constraints. This design adds clock and timing report constraints and uses them as instances.

#### **Clock Constraints**

Select "Timing Constraints > Clocks" and right-click to select "Create Clock" as shown in Source Object: get\_pins { u\_MIPI\_RX\_Advance\_Top/DPHY\_RX\_INST/u\_idesx8/Inst3\_CLKDIV /CLKOUT}

Figure 3-14. The constraints are as follows:

- Clock name: clk\_rx

- Period: 10

- Rising: 0

- Falling: 5

- Source Object: get\_pins

{ u\_MIPI\_RX\_Advance\_Top/DPHY\_RX\_INST/u\_idesx8/Inst3\_CLKDIV

/CLKOUT}

Figure 3-14 Clock Constraints

| 🐳 Create Cl     | ock                       |         |        |                   |          | ?     | ×   |

|-----------------|---------------------------|---------|--------|-------------------|----------|-------|-----|

| Clock name:<br> | clk_rx                    |         |        |                   |          |       |     |

| Period:         | 10                        | ns      |        |                   |          |       |     |

| Frequency:      | 100                       | MCHz    |        |                   |          |       |     |

| Rising:         | 0                         | ns      |        |                   |          |       |     |

| Falling:        | 5                         | ns      |        | ) E               | i        | 10    | -   |

| Objects: u_M    | IPI_RX_Advance_Top/DPHY_R | X_INST/ | u_i de | sx8/Inst3_CLKDIV/ | CLKOVT}] | 🗌     | Add |

|                 |                           |         |        |                   | OK       | Cance | 1   |

#### **Timing Report Constraint**

Select "Timing Constraints > Report > Report Timing" and right-click to select "Create Report". You can configure parameters in Report Timing dialog box. The max.setup path is 100, as shown in Figure 3-15.

| Report Timing   |        |                  | ? >       |

|-----------------|--------|------------------|-----------|

| Clocks          |        |                  |           |

| From clock: 🔻   | clk_rx |                  | ~         |

| To clock: 🔻     | clk_rx |                  | ~         |

| Objects         |        |                  |           |

| From: 🔻         |        |                  |           |

| Through:        |        |                  |           |

| To: 🔻           |        |                  |           |

| Analysis Type   |        |                  |           |

| 🖲 Setup         | ⊖ Hold | 🔿 Recovery       | 🔿 Removal |

| Path            |        |                  |           |

| Max Paths:      | 100    | Min Logic Level: |           |

| Max Common Path | s:     | Max Logic Level: |           |

| Module Instance | :      |                  |           |

|                 |        |                  |           |

#### **Figure 3-15 Timing Report Constraints**

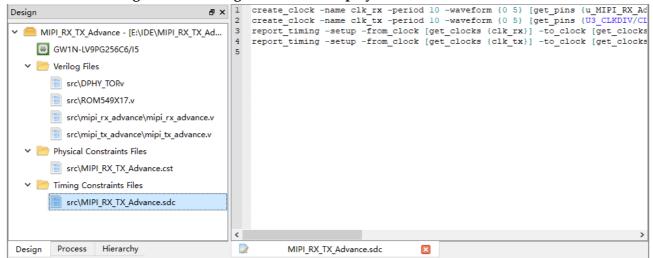

After constraints is finished, click "Save" to generate timing constraints, as shown in Figure 3-16.

Figure 3-16 Timing Constraints Display

In PnR, if there is no timing constraints file, the PnR will be automatically performed. If there is a timing constraint file, the PnR will be performed according to the timing constraints file.

## 3.4.2 Modify Timing Constraints

After timing constraints files are generated, you can modify the constraints by Timing Constrains Editor. Click "Save" to finish.

# 3.5 GAO Configuration

After synthesis, you can create GAO config file to capture data and verify the design. Gowin Software provides Standard Mode GAO and Lite Mode GAO. For the usage, see <u>SUG114</u>, Gowin Analyzer Oscilloscope User Guide.

This design uses Standard Mode GAO and takes it as an instance.

#### 3.5.1 Create Standard Mode GAO Config File

Select "Design > New File..." to open "New" dialog box, and select "GAO Config File" in "New", as shown in Figure 3-17. Click "OK". Select For Post-Synthesis Netlist in Type, Standard in Mode. Click "Next". The file name is MIPI\_RX\_TX. Then click "Next" until finished.

| Figure 3-17 | <b>'Create GAO</b> | <b>Config File</b> |

|-------------|--------------------|--------------------|

|-------------|--------------------|--------------------|

| 🐝 New                            | ?      | × |

|----------------------------------|--------|---|

| Timing Constraints File          |        | ^ |

| GowinSynthesis Constraints File  |        |   |

| 📘 User Flash Initialization File |        |   |

| GAO Config File                  |        |   |

| GPA Config File                  |        |   |

| Memory Initialization File       |        |   |

|                                  |        | × |

| Create a GAO Config File.        |        |   |

|                                  |        |   |

|                                  |        |   |

| OK                               | Cancel | - |

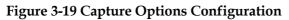

#### 3.5.2 Configure Standard Mode GAO

After file created, you can configure the number of AO cores, trigger options and capture options. The trigger options include match unit, trigger port, match type and expressions; The capture options include sample clock, capture, capture utilization and capture signals. In this design the number of AO cores is 1 and the trigger options and capture options configuration are shown in Figure 3-18 and Figure 3-19.

| ore O             |        |          |         |              |                 |          |           |       |   |                 |

|-------------------|--------|----------|---------|--------------|-----------------|----------|-----------|-------|---|-----------------|

| Trigger Options ( | Captur | e Op     | tions   |              |                 |          |           |       |   |                 |

| Trigger Ports     |        | Matc     | h Units |              |                 |          |           |       |   | Expressions     |

| Trigger Port 0    |        | Mat      | ch Unit | Trigger Port | Match Type      | Function | Counter   | Value | - | 🖲 Static 🔘 Dyna |

| ready_c           |        | <b>V</b> | M0      | Trigger 0    | Basic w/edges   | ==       | Disabled  | R     |   | MO              |

| Trigger Port 1    |        |          |         |              | basic ii, cages |          | 0.000.000 |       |   |                 |

| Trigger Port 2    |        |          | M1      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 3    |        |          | M2      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 4    |        |          |         |              |                 |          |           |       |   |                 |

| Trigger Port 5    |        |          | M3      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 6    |        |          | M4      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 7    |        |          |         | Home         |                 |          | bibabiea  |       |   |                 |

| Trigger Port 8    |        |          | M5      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 9    |        |          | M6      | NONE         | Basic           | ==       | Disabled  |       | _ |                 |

| Trigger Port 10   | 0      |          | INIO    | NONE         | Dasie           |          | Disabicu  |       | Ξ |                 |

| Trigger Port 1    | 1      |          | M7      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 12   | 2      |          | M8      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 13   | 3      |          | INIO    | NONE         | Dasie           |          | Disabicu  |       |   |                 |

| Trigger Port 14   | 4      |          | M9      | NONE         | Basic           | ==       | Disabled  |       |   |                 |

| Trigger Port 1    | 5      |          | M10     | NONE         | Basic           | ==       | Disabled  |       |   |                 |

Figure 3-18 Trigger Options Configuration

| ore 0               |                |     |             |                  |        |

|---------------------|----------------|-----|-------------|------------------|--------|

| rigger Options C    | apture Options |     |             |                  |        |

| Sample Clock        |                | Ca  | oture Signa | als              |        |

| Clock: clk_byt      | te_out         |     | Add         | Add From Trigger | Remove |

| Sample On: 🖲 Risir  | ng 🔿 Falling   | >   | data_out(   | 0[15:0]          |        |

| Cantura             |                | >   | data_out1   | 1[15:0]          |        |

| Capture             |                | >   | data_out2   | 2[15:0]          |        |

| Storage Size:       | 1024           | - > | data_out3   | 3[15:0]          |        |

| Windows Number:     | 1              | -   | ready       |                  |        |

| Capture Amount:     | 1024           | -   |             |                  |        |

| Trigger Position:   | 100            |     |             |                  |        |

| Capture Utilization |                |     |             |                  |        |

| BSRAM Usage : 4/2   | 6              |     |             |                  |        |

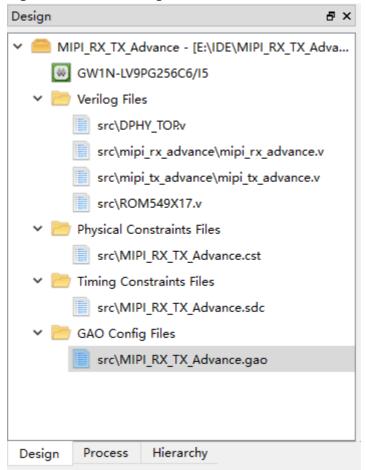

After configuration, click "Save" to finish and the design window is as shown in Figure 3-20.

Figure 3-20 GAO Config Files

# 3.6 GPA Configuration

After synthesis, you can create a GPA config file to analyze power. For the usage, please refer to <u>SUG282</u>, Gowin Power Analyzer User Guide.

# 3.6.1 Create GPA Config File

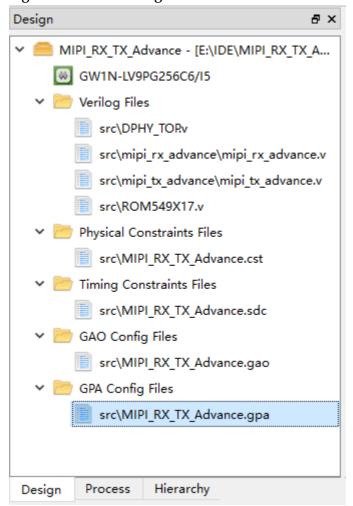

Select "Design > New File..." to open "New" dialog box, and select "GPA Config File" in "New", as shown in Figure 3-21. Click "OK". The file name is MIPI\_RX\_TX\_Advance, and the file is under src by default. Then click "OK" to finish.

| New       |                                                                                              | ?   | ×   |

|-----------|----------------------------------------------------------------------------------------------|-----|-----|

|           | Timing Constraints File<br>GowinSynthesis Constraints File<br>User Flash Initialization File |     | ^   |

|           | GAO Config File<br>GPA Config File<br>Memory Initialization File                             |     |     |

|           | · ·                                                                                          |     | ¥   |

| GOWIN Pow | er Analyzer Config File.                                                                     |     |     |

|           | ОК                                                                                           | Can | cel |

#### Figure 3-21 Create GPA Config File

#### 3.6.2 Configure GPA

After GPA config file is created, configure General Setting, Rate Setting and Clock Setting.

- General Setting includes the parameters of device, package, speed grade, temperature grade, thermal impedance, and voltage.

- Rate Setting is used to configure signal transition rate. You can set transition rate of IO or Net, or use the default value.

- Clock Setting is used to configure clock and enable features of BSRAM, I/O and DFF.

#### **General Setting**

In this design, the general setting is configured as follows: commercial temperature,  $25^{\circ}$ C ambient temperature, no heat sink, VCCX 3.3V and VCC 1.2V, as shown in Figure 3-22.

| Device<br>Device: GW1N-LV9PG256C6/I5<br>Operating Condition: COMMERCIAL ▼ Process: TYPICAL ▼<br>Environment<br>Ambient Temperature: 25.000°C ▼<br>Custom Theta JA: 25.000°C/W ↓<br>Heat Sink<br>● None ○ Low Profile ○ Medium Profile ○ High Profile ○ Custo<br>Air-flow: 0 ▼ (LFM)<br>Custom Theta SA: 25.000°C/W ↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Condition: COMMERCIAL ▼ Process: TYPICAL ▼   Invironment    Imbient Temperature: 25.000°C ▼   Imbient Temperature: 25.000°C/W ↓   Heat Sink    Image: |

| invironment<br>Ambient Temperature: 25.000℃ ♀<br>Custom Theta JA: 25.000℃/W ♀<br>Heat Sink<br>● None ○ Low Profile ○ Medium Profile ○ High Profile ○ Custo<br>Air-flow: 0 ▼ (LFM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| mbient Temperature: 25.000℃ ♀<br>Custom Theta JA: 25.000℃/W ♀<br>Heat Sink<br>● None ○ Low Profile ○ Medium Profile ○ High Profile ○ Custo<br>Air-flow: 0 ▼ (LFM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Custom Theta JA: 25.000°C/W ↓<br>Heat Sink<br>● None ○ Low Profile ○ Medium Profile ○ High Profile ○ Custo<br>Air-flow: 0 ▼ (LFM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Custom Theta JA: 25.000°C/W ↓<br>Heat Sink<br>● None ○ Low Profile ○ Medium Profile ○ High Profile ○ Custo<br>Air-flow: 0 ↓ (LFM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Heat Sink<br>● None ○ Low Profile ○ Medium Profile ○ High Profile ○ Custo<br>Air-flow: 0 ▼ (LFM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

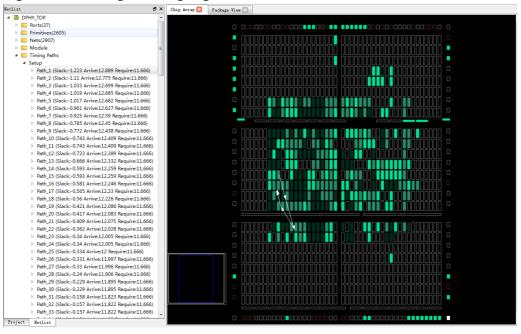

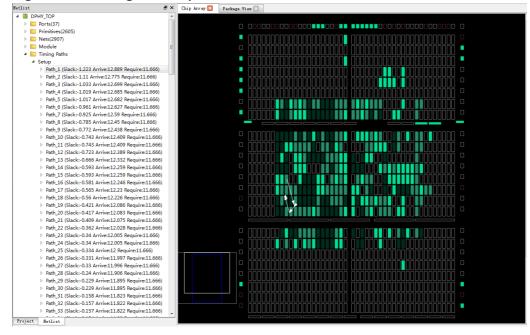

| <ul> <li>None ○ Low Profile ○ Medium Profile ○ High Profile ○ Custo</li> <li>Air-flow: 0</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |