## **HCS08 Family**

Reference Manual

M68HCS08 Microcontrollers

HCS08RMv1/D Rev. 2 05/2007

## **List of Chapters**

| Chapter 1 General Information and Block Diagram | 15  |

|-------------------------------------------------|-----|

| Chapter 2 Pins and Connections                  | 19  |

| Chapter 3 Modes of Operation                    | 25  |

| Chapter 4 On-Chip Memory                        | 37  |

| Chapter 5 Resets and Interrupts                 | 65  |

| Chapter 6 Central Processor Unit (CPU)          | 79  |

| Chapter 7 Development Support                   | 145 |

| Appendix A Instruction Set Details              | 197 |

| Appendix B Equate File Conventions              | 295 |

**List of Chapters**

Chapter 1

General Information and Block Diagram

|        | General information and block blagiant                         |    |

|--------|----------------------------------------------------------------|----|

| 1.1    | Introduction to the HCS08 Family of Microcontrollers           | 15 |

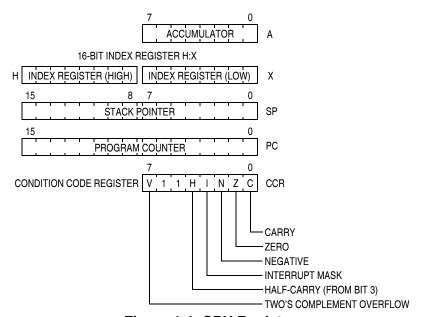

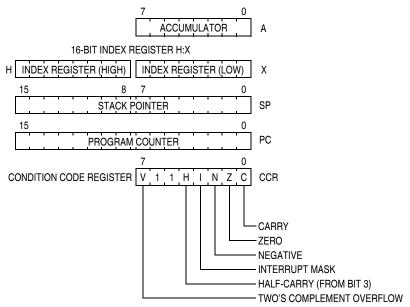

| 1.2    | Programmer's Model for the HCS08 CPU                           | 16 |

| 1.3    | Peripheral Modules                                             | 16 |

| 1.4    | Features of the MC9S08GB60                                     |    |

| 1.4.1  | Standard Features of the HCS08 Family                          |    |

| 1.4.2  | Features of MC9S08GB60 MCU                                     |    |

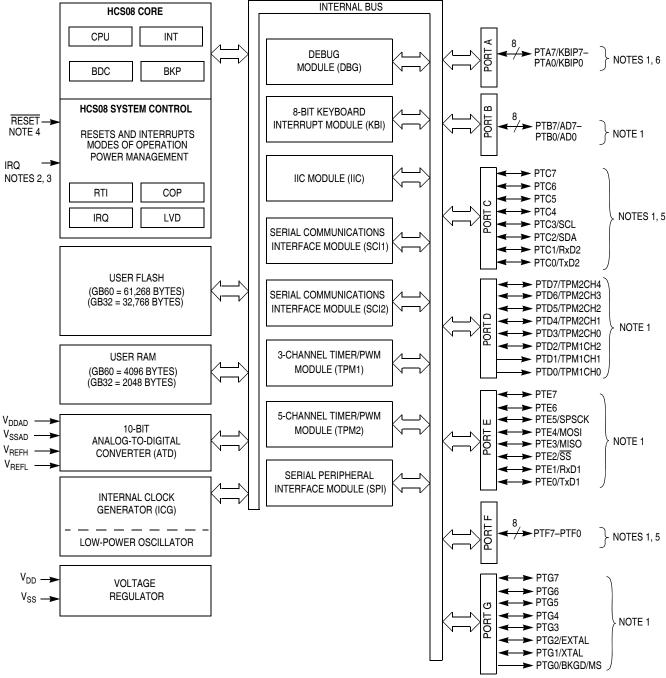

| 1.5    | Block Diagram of the MC9S08GB60                                |    |

|        | Chapter 2                                                      |    |

|        | Pins and Connections                                           |    |

| 2.1    | Introduction                                                   | 19 |

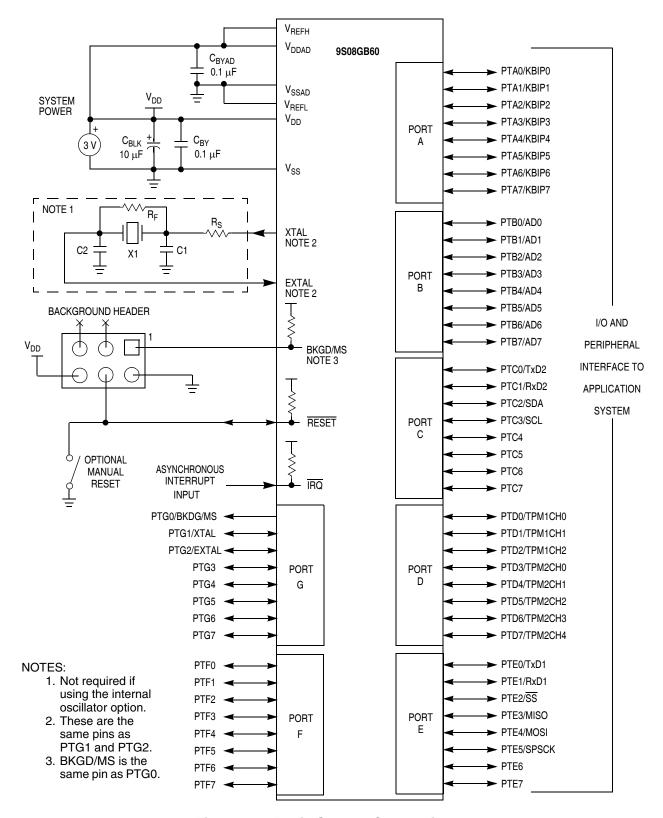

| 2.2    | Recommended System Connections                                 | 19 |

| 2.2.1  | Power                                                          |    |

| 2.2.2  | MC9S08GB60 Oscillator                                          |    |

| 2.2.3  | Reset                                                          |    |

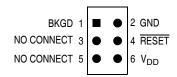

| 2.2.4  | Background/Mode Select (BKGD/MS)                               |    |

| 2.2.5  | General-Purpose I/O and Peripheral Ports                       | 22 |

|        | Chapter 3                                                      |    |

|        | Modes of Operation                                             |    |

| 3.1    | Introduction                                                   | 25 |

| 3.2    | Features                                                       | 25 |

| 3.3    | Run Mode                                                       | 25 |

| 3.4    | Active Background Mode                                         | 25 |

| 3.5    | Wait Mode                                                      | 26 |

| 3.6    | Stop Modes                                                     |    |

| 3.6.1  | Stop1 Mode                                                     |    |

| 3.6.2  | Stop2 Mode                                                     |    |

| 3.6.3  | Stop3 Mode                                                     |    |

| 3.6.4  | Active BDM Enabled in Stop Mode                                | 29 |

| 3.6.5  | OSCSTEN Bit Set                                                | 30 |

| 3.6.6  | LVD Enabled in Stop Mode                                       | 30 |

| 3.6.7  | On-Chip Peripheral Modules in Stop Modes                       |    |

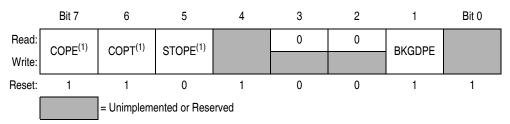

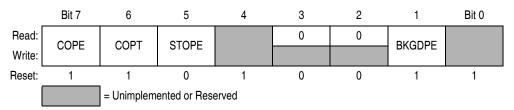

| 3.6.8  | System Options Register (SOPT)                                 |    |

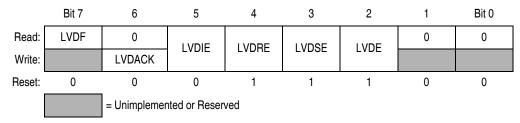

| 3.6.9  | System Power Management Status and Control 1 Register (SPMSC1) |    |

| 3.6.10 | System Power Management Status and Control 2 Register (SPMSC2) | 34 |

## Chapter 4 On-Chip Memory

| 4.1            | Introduction                                                                      | 37        |

|----------------|-----------------------------------------------------------------------------------|-----------|

| 4.2            | HCS08 Core-Defined Memory Map                                                     | 37        |

| 4.2.1          | HCS08 Memory Map                                                                  | 37        |

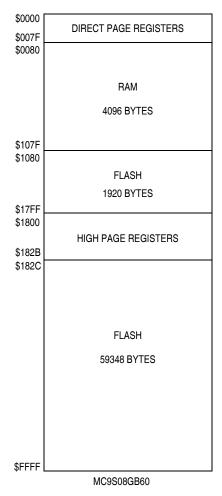

| 4.2.2          | MC9S08GB60 Memory Map                                                             | 38        |

| 4.2.3          | Reset and Interrupt Vector Assignments                                            | 39        |

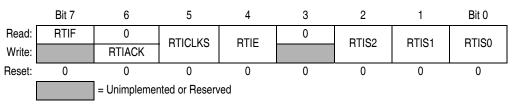

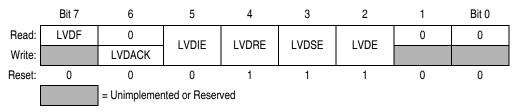

| 4.3            | Register Addresses and Bit Assignments                                            | 41        |

| 4.4            | RAM                                                                               | 46        |

| 4.5            | 60-Kbyte FLASH                                                                    | 46        |

| 4.5.1          | Features                                                                          |           |

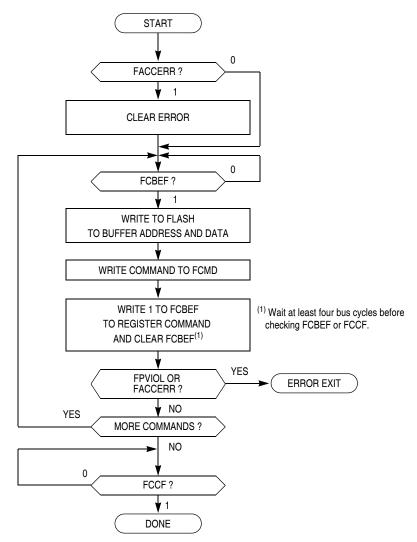

| 4.5.2          | Program, Erase, and Blank Check Commands                                          |           |

| 4.5.3          | Command Timing and Burst Programming                                              |           |

| 4.5.3.1        | Rows and FLASH Organization                                                       |           |

| 4.5.3.2        | <b>5</b> 1                                                                        |           |

| 4.5.4          | Access Errors                                                                     |           |

| 4.5.5<br>4.5.6 | Vector Redirection                                                                |           |

|                | FLASH Block Protection (MC9S08GB60)                                               |           |

| 4.6            | Security (MC9S08GB60)                                                             |           |

| 4.7            | FLASH Registers and Control Bits (MC9S08GB60)                                     |           |

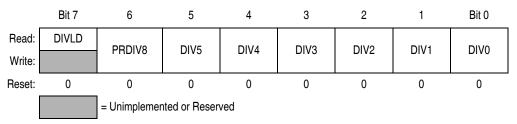

| 4.7.1<br>4.7.2 | FLASH Clock Divider Register (FCDIV)                                              |           |

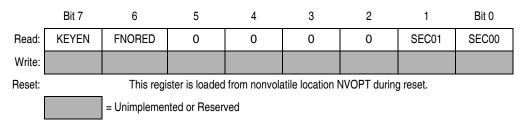

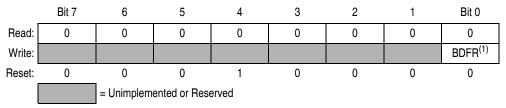

| 4.7.2<br>4.7.3 | FLASH Options Register (FOPT and NVFOPT)                                          |           |

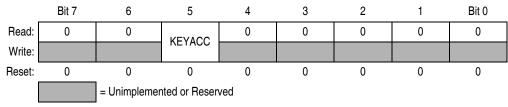

| 4.7.3<br>4.7.4 | FLASH Configuration Register (FCNFG)FLASH Protection Register (FPROT and NVFPROT) |           |

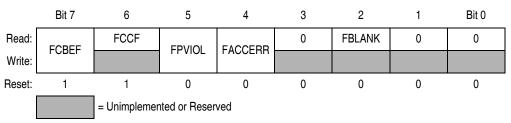

| 4.7.5          | FLASH Status Register (FSTAT)                                                     |           |

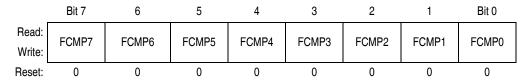

| 4.7.6          | FLASH Command Register (FCMD)                                                     |           |

| 4.8            | FLASH Application Examples                                                        |           |

| 4.8.1          | Initialization of the FLASH Module Clock.                                         |           |

| 4.8.2          | Erase One 512-Byte Page in FLASH                                                  |           |

| 4.8.3          | DoOnStack Subroutine                                                              |           |

| 4.8.4          | SpSub Subroutine                                                                  |           |

| 4.8.5          | Program One Byte of FLASH                                                         | 64        |

|                |                                                                                   |           |

|                | Chapter 5                                                                         |           |

|                | Resets and Interrupts                                                             |           |

| 5.1            | Introduction                                                                      |           |

| 5.2            | Reset and Interrupt Features for MC9S08GB60                                       | 65        |

| 5.3            | MCU Reset                                                                         | 66        |

| 5.4            | Computer Operating Properly (COP) Watchdog                                        | 66        |

| 5.5            | Interrupts                                                                        | 66        |

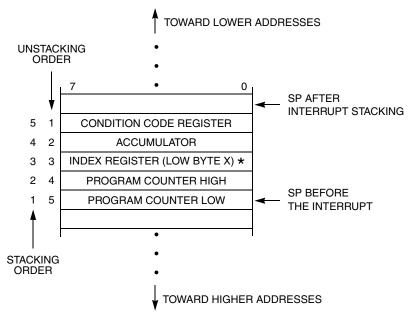

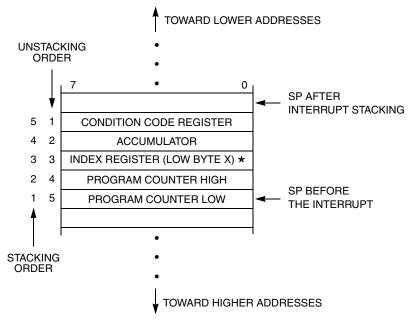

| 5.5.1          | Interrupt Stack Frame                                                             |           |

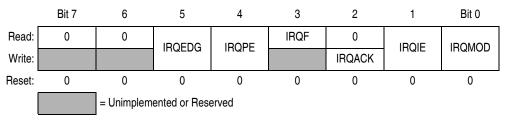

| 5.5.2          | External Interrupt Request (IRQ) Pin                                              | 67        |

| 5.5.2.1        | Pin Configuration Options                                                         |           |

| 5.5.2.2        | 3 · · · · · · · · · · · · · · · · · · ·                                           |           |

| 5.5.3          | Interrupt Vectors, Sources, and Local Masks                                       | <b>69</b> |

HCS08 Family Reference Manual, Rev. 2

| 69 |

|----|

| 69 |

| 69 |

| 69 |

| 69 |

| 71 |

| 71 |

| 72 |

| 73 |

| 74 |

| 74 |

| 75 |

| 76 |

| 77 |

| 78 |

|    |

|    |

|    |

| 79 |

| 80 |

| 80 |

| 81 |

| 82 |

| 84 |

| 84 |

| 89 |

| 90 |

| 90 |

| 91 |

| 91 |

| 92 |

| 92 |

| 92 |

| 92 |

| 92 |

| 93 |

| 93 |

| 93 |

| 94 |

| 94 |

| 94 |

| 95 |

| 96 |

| 96 |

| 96 |

|    |

|    |

| 6.5            | Instruction Set Description by Instruction Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 97   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.5.1          | Data Movement Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 6.5.1.1        | Loads and Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98   |

| 6.5.1.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.1.3        | Memory-to-Memory Moves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 101  |

| 6.5.1.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.2          | Math Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 6.5.2.1        | Add, Subtract, Multiply, and Divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 6.5.2.2        | Increment, Decrement, Clear, and Negate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107  |

| 6.5.2.3        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 6.5.2.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.3          | Logical Operation Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 6.5.3.1        | AND, OR, Exclusive-OR, and Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 6.5.3.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.4          | Shift and Rotate Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 6.5.5          | Jump, Branch, and Loop Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 6.5.5.1        | Unconditional Jump and Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 6.5.5.2        | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 6.5.5.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.5.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.5.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.5.6        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.5.6          | Stack-Related Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 6.5.7          | Miscellaneous Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 6.6            | Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121  |

| 6.7            | Assembly Language Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 6.7.1          | Parts of a Listing Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 6.7.2          | Assembler Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 133  |

| 6.7.2.1        | BASE — Set Default Number Base for Assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 6.7.2.2        | t variable to the state of the |      |

| 6.7.2.3        | NOLIST/LIST — Turn Off or Turn On Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 134  |

| 6.7.2.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 6.7.2.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |