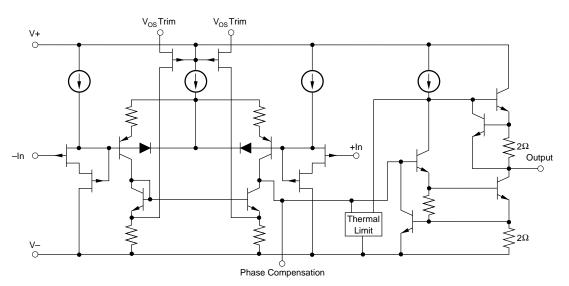

## **OPA654**

# Wide Bandwidth, High Output Current Difet ® OPERATIONAL AMPLIFIER

## **FEATURES**

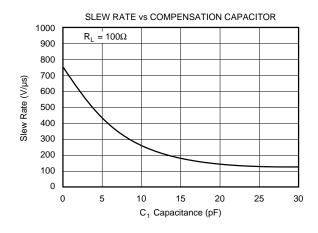

• HIGH SLEW RATE: 750V/μs

HIGH OUTPUT CURRENT: 200mA

WIDE GAIN-BANDWIDTH: 700MHz

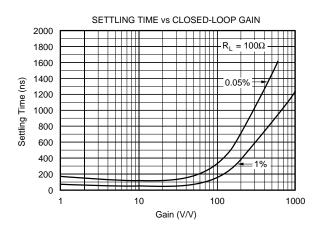

FAST SETTLING: 150ns to 0.1%

• FET INPUT:  $I_R = 50pA max$

## DESCRIPTION

The OPA654 is a high-speed monolithic operational amplifier featuring 200mA output current. Fabricated using Burr-Brown's Complementary-Bipolar, *Difet* process, it provides an excellent combination of high speed and high output current.

The OPA654 is versatile, operating from power supplies ranging from  $\pm 5V$  to  $\pm 18V.$  It can deliver up to  $\pm 10V$  signals into a  $50\Omega$  load at slew rates of  $750V/\mu s$ . Its speed and output current make it useful for line driver and automatic test applications.

## **APPLICATIONS**

- LINE DRIVERS

- PIN DRIVERS

- HIGH-SPEED DATA ACQUISITION

- WAVEFORM GENERATORS

The OPA654 is externally compensated, allowing openloop gain and phase characteristics to be optimized for the desired closed-loop gain, load and dynamic characteristics.

The OPA654 is available in an 8-pin metal TO-3 package that provides excellent thermal characteristics and is specified for the industrial temperature range.

Difet ®, Burr-Brown Corp.

International Airport Industrial Park

- Mailing Address: PO Box 11400

- Tel: (520) 746-1111

- Twx: 910-952-1111

- Cable: BBRCORP

- Tucson, AZ 85734

- Tucson, AZ 85734

- Street Address: 6730 S. Tucson Blvd.

- Tucson, AZ 85706

- Tucson, AZ 85706

- Telex: 066-6491

- FAX: (520) 889-1510

- Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

### **ELECTRICAL**

$T_A = +25$ °C,  $V_S = \pm 15$ V unless otherwise noted.

|                                                                                                                                                                                                           |                                                                                 | OPA654AM          |                                                    |                     |                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|----------------------------------------------------|---------------------|-----------------------------------------------|

| PARAMETER                                                                                                                                                                                                 | CONDITION                                                                       | MIN               | TYP                                                | MAX                 | UNITS                                         |

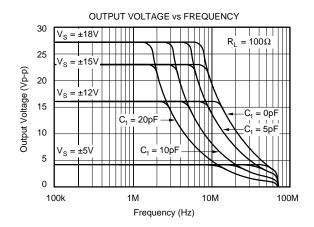

| FREQUENCY RESPONSE Gain-Bandwidth Product (2) Slew Rate (2,3) Settling Time (2) 0.01% 0.1% 1%                                                                                                             | G = -1, 20V Step<br>G = -1, 10V Step<br>G = -1, 10V Step<br>G = -1, 10V Step    |                   | See Typical Curve<br>750<br>240<br>150<br>85       |                     | V/μs<br>ns<br>ns<br>ns                        |

| OFFSET VOLTAGE<br>Input Offset Voltage<br>Average Drift<br>Power Supply Rejection                                                                                                                         | V <sub>s</sub> = ±5 to ±15V                                                     | 72                | ±0.1<br>±40<br>82                                  | ±3                  | mV<br>μV/°C<br>dB                             |

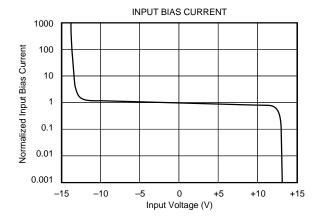

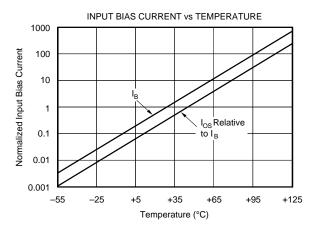

| INPUT BIAS CURRENT <sup>(1)</sup> Input Bias Current Input Offset Current                                                                                                                                 | $V_{CM} = 0V$ $V_{CM} = 0V$                                                     |                   | 3<br>2                                             | 50<br>25            | pA<br>pA                                      |

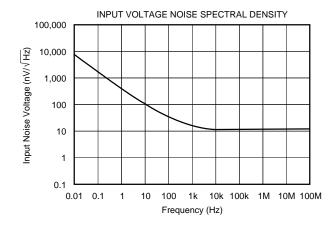

| NOISE Input Voltage Noise Noise Density,  Voltage Noise, Input Bias Current Noise Current Noise Density, f = 0.1Hz to 20kHz                                                                               | f = 10Hz<br>f = 100Hz<br>f = 1kHz<br>f = 10kHz<br>f <sub>B</sub> = 10Hz to 1MHz |                   | 115<br>37<br>19<br>14<br>85                        |                     | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>μVp-p |

| INPUT VOLTAGE RANGE<br>Common-Mode Input Range<br>Common-Mode Rejection                                                                                                                                   | V <sub>CM</sub> = ±10V                                                          | ±12<br>70         | ±13<br>76                                          |                     | V<br>dB                                       |

| INPUT IMPEDANCE<br>Differential<br>Common-Mode                                                                                                                                                            |                                                                                 |                   | 10 <sup>12</sup>    2.5<br>10 <sup>12</sup>    3.2 |                     | Ω    pF<br>Ω    pF                            |

| OPEN-LOOP GAIN<br>Open-Loop Voltage Gain                                                                                                                                                                  | $V_O = \pm 10V, R_L = 1k\Omega$<br>$V_O = \pm 10V, R_L = 50\Omega$              | 80                | 94<br>82                                           |                     | dB<br>dB                                      |

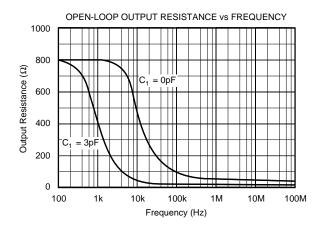

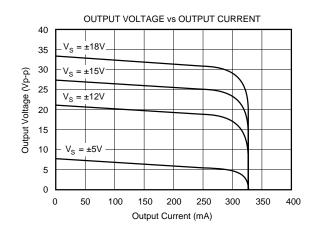

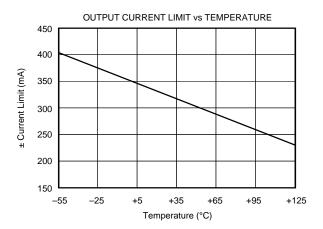

| OUTPUT Voltage Output Current Output Short Circuit Current Output Resistance, Open-Loop                                                                                                                   | $R_{L} = 50\Omega$ $V_{O} = \pm 10V$ $DC$                                       | ±11               | ±12.3<br>200<br>325<br>800                         |                     | V<br>mA<br>mA<br>Ω                            |

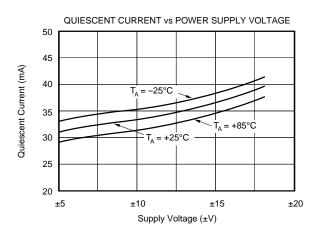

| POWER SUPPLY Specified Operating Voltage Operating Voltage Range Quiescent Current                                                                                                                        |                                                                                 | ±5                | ±15<br>±38                                         | ±18<br>±43          | V<br>V<br>mA                                  |

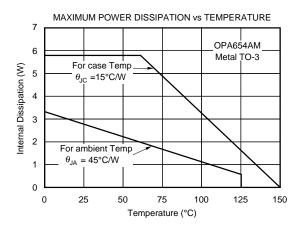

| $\begin{tabular}{ll} \textbf{TEMPERATURE RANGE} \\ \textbf{Specification} \\ \textbf{Operating} \\ \textbf{Storage} \\ \textbf{Thermal Resistance, } \theta_{\tt JC} \\ \theta_{\tt JA} \\ \end{tabular}$ |                                                                                 | -25<br>-55<br>-55 | 15<br>45                                           | +85<br>+125<br>+150 | °C<br>°C<br>°C/W<br>°C/W                      |

NOTES: (1) High-speed test at  $T_j = 25^{\circ}$ C. (2) Varies with external phase compensation,  $C_1$ . See typical curves for performance with other gains and  $C_1$ . (3) Slew rate is rate of change from 10% to 90% of output voltage step.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

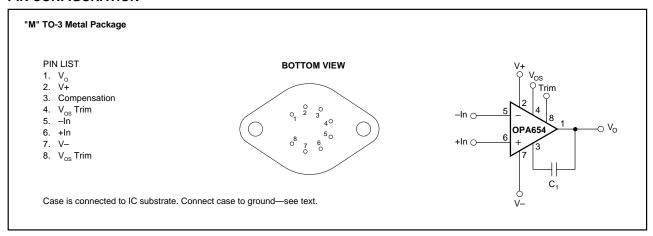

### **PIN CONFIGURATION**

## **ABSOLUTE MAXIMUM RATINGS**

| ±18V                |

|---------------------|

| ±V <sub>S</sub> ±1V |

| 10s                 |

| –55°C to +125°C     |

| –55°C to +150°C     |

| +165°C              |

| +300°C              |

|                     |

## PACKAGE INFORMATION(1)

| MODEL    | PACKAGE          | PACKAGE DRAWING<br>NUMBER |

|----------|------------------|---------------------------|

| OPA654AM | 8-Pin Metal TO-3 | 030                       |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

## **ORDERING INFORMATION**

| MODEL    | PACKAGE          | TEMPERATURE RANGE |

|----------|------------------|-------------------|

| OPA654AM | 8-Pin Metal TO-3 | −25°C to +85°C    |

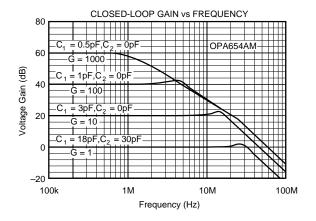

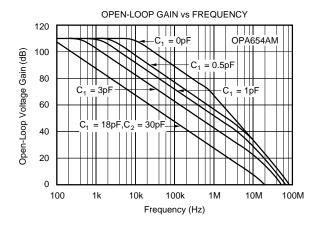

## **TYPICAL PERFORMANCE CURVES**

$T_A = +25$ °C,  $V_S = \pm 15$ V unless otherwise noted.

## TYPICAL PERFORMANCE CURVES (CONT)

$T_A = +25$ °C,  $V_S = \pm 15$ V unless otherwise noted.

## **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A = +25$ °C,  $V_S = \pm 15$ V unless otherwise noted.

### **CIRCUIT LAYOUT**

With any wide-bandwidth circuitry, careful circuit layout will ensure best performance. Make short, direct circuit interconnections and avoid stray wiring capacitance—especially at the inverting input pin. A component-side ground plane will help ensure low ground impedance. Do not place the ground plane under or near the inputs and feedback network.

Power supplies should be bypassed with good high-frequency capacitors positioned close to the op amp pins. In most cases, a  $2.2\mu F$  solid tantalum capacitor for each power supply is adequate. The OPA654 can deliver load currents up to 200mA. Even if steady-state load currents are lower, signal transients may demand large current transients from the power supplies. It is the power supply bypass capacitors which must supply these current transients. Larger bypass capacitors such as  $10\mu F$  solid tantalum capacitors may improve dynamic performance in these applications.

#### **CASE CONNECTION**

The case of the TO-3 metal package should be connected to ground. Failure to connect the case to ground will not damage the device but will degrade its AC performance. The case is internally connected to the substrate of the dielectrically isolated IC. This substrate is DC-neutral—it is not connected to the V– power supply as it would be with most analog ICs. In principle, it could be connected to any AC ground potential such as one of the power supplies, but DC ground is usually most convenient. Do not connect the case to DC potentials which exceed the power supply voltages,  $\pm V_s$ .

## **OFFSET ADJUSTMENT**

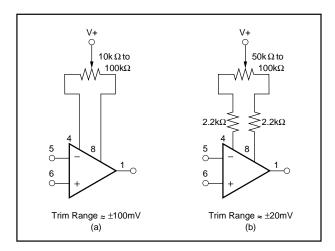

Many applications require no external offset voltage adjustment. Figure 1a shows connection of an optional offset voltage trimming potentiometer. Use a small, non-inductive potentiometer with short connections to the trim pins. Avoid stray capacitance from the input or output nodes. The added resistors in Figure 1b help decouple the potentiometer from

these sensitive nodes, making the type and location of the potentiometer less critical. This also reduces the trim range, providing more adjustment resolution. Do not use an offset voltage adjustment to correct for offsets produced in other circuitry since this can introduce large offset voltage drift.

#### **COMPENSATION**

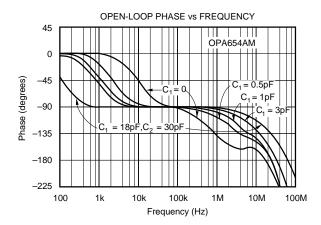

The OPA654 uses external compensation capacitors. This tailors the open-loop response characteristics to the application. Its effect can be seen in the open-loop gain and phase curves.

FIGURE 1. Optional Offset Voltage Trim Circuits.

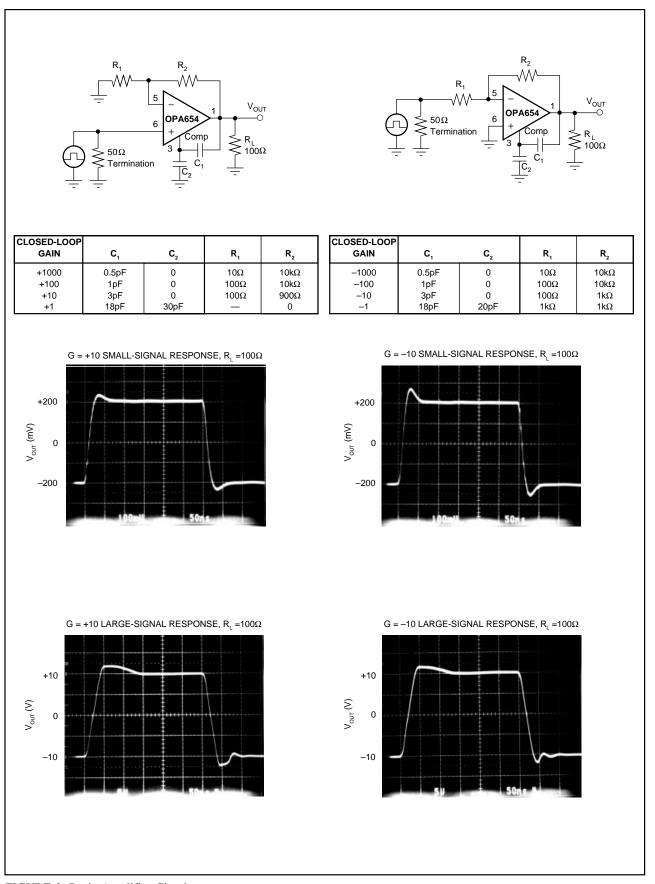

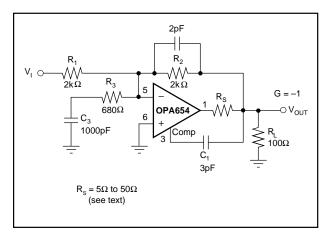

Figures 2 shows typical capacitor values for various closed-loop gains. This chart should be considered a starting point for optimizing an application. Many variables including circuit layout, source and load characteristics, and desired dynamic behavior will affect the optimum capacitor values. Capacitive loads change op amp behavior and higher compensation capacitor values are generally required. Resistor  $R_{\rm s}$ , shown in Figure 3, can improve the ability to drive a capacitive load. Typical values for  $R_{\rm s}$  range from  $5\Omega$  to  $50\Omega$ , depending on the load and how much voltage drop can be tolerated.

FIGURE 2. Basic Amplifier Circuits.

Figure 3 also demonstrates a compensation technique using an additional network,  $R_3$ - $C_3$ . This allows use of a smaller value for  $C_1$ , producing a corresponding increase in slew rate. It reduces the high frequency loop gain by placing the op amp in a higher noise gain at high frequency. This technique improves large-signal response at the sacrifice of small-signal behavior. Settling time is increased and high frequency noise performance will be somewhat degraded.

FIGURE 3. High Slew Rate Compensation Circuit.

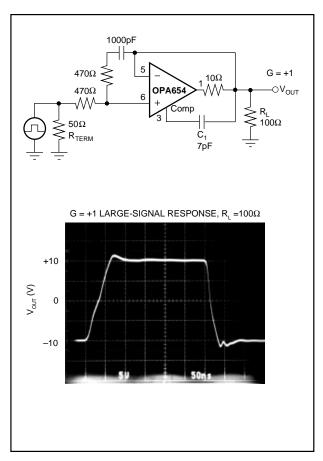

Figure 4 shows an alternative compensation network for unity gain. This technique provides a small amount of positive feedback, reducing the net negative feedback factor. Large signal response and load driving capability is improved with this approach.

The compensation for a given application can be evaluated by observing amplifier pulse response. Both small-signal and large-signal response should be checked to assure that both are acceptable. Large overshoot or many cycles of ringing in the small-signal response is a sign of instability and the circuit may require further optimization. Good practice dictates a somewhat conservative approach to allow for device-to-device variation.

### **POWER DISSIPATION**

Many applications do not require an external heat sink. However, with high ambient temperature or heavy load conditions, a heat sink may be required. The heat sink should be electrically connected to ground—see "Connections to Case". Operate within the power derating curve (Maximum Power Dissipation vs Temperature) shown in the typical performance curve section.

Exceeding the maximum die temperature of 165°C may activate the internal thermal limit circuitry, disabling the output stage. This thermal limit is set for a junction temperature of approximately 185°C.

FIGURE 4. G = +1 Amplifier with Alternative Compensation.

The OPA654 may be operated at reduced power supply voltage, thus reducing internal power dissipation. This can eliminate the need for heat sinking in some applications.

#### **OUTPUT CURRENT LIMIT**

Output current is limited by internal circuitry to approximately 325mA at 25°C. The limit current decreases with increasing junction temperature as shown in the typical curves. The combination of current limit and thermal limit protects the device from short circuits to ground.

#### **INPUT BIAS CURRENT**

The OPA654 is fabricated with Burr-Brown's dielectrically isolated *Difet* process, giving it very low input bias current. Like other FET amplifiers, input bias current doubles for every 10°C increase in junction temperature. This increase can be minimized by providing a heat sink and, if possible, operating with reduced power supply voltage to minimize power dissipation.