# **Building an APB3 Core for SmartFusion FPGAs**

## Introduction

The Advanced Microcontroller Bus Architecture (AMBA®) specification defines an on-chip communications standard for designing high-performance embedded microcontrollers. Several distinct buses are defined within the AMBA specification, including advanced high-performance bus (AHB) and advanced peripheral bus (APB). The AMBA-AHB is used to connect high-performance modules and the AMBA-APB is used for low-power and low-speed peripherals.

Actel SmartFusion™ intelligent mixed-signal FPGAs include a hard embedded microcontroller subsystem (MSS) with FPGA fabric and high-performance analog block. The MSS is composed of a 100 MHz ARM® Cortex™-M3 processor and integrated peripherals, which are interconnected via a multi-layer AHB bus matrix (ABM). The MSS can be connected to the FPGA fabric through a configurable fabric interface controller (FIC) that allows either an AHB to AHB or AHB to APB3 (also known as APB v3) bridging function between the ABM and an AHB or APB3 bus implemented in the FPGA fabric. APB3 is much simpler than AHB and the user logic in the FGPA normally communicates with the MSS via APB3 register mapping. This document describes how to create an APB3 wrapper interface for the user's logic or IP and how to connect it to the MSS through the FIC.

# Overview of APB, APB3, AHB, and AHB-Lite

The AMBA bus specification is an open standard introduced by ARM Ltd. and details a strategy for the interconnection and management of functional blocks in an embedded microcontrollers or system-on-chip (SoC). Several distinct buses are defined within the AMBA specification. The AMBA AHB is for high-performance, high clock frequency system modules to support efficient connection of processors, on-chip memories, and off-chip external memory interfaces. It allows high performance, pipelined operation, multiple bus masters, burst transfers, and split transactions. AHB-Lite, defined in the AMBA 3 protocol (third generation of the AMBA specification), is a subset of the full AHB specification for use in designs where only a single bus master is used. AMBA APB is used to interface with any peripherals that are low bandwidth and do not require the high performance of a pipelined bus interface. This bus has an address and data phase similar to AHB, but a much reduced low complexity signal list; for example, no bursts. APB3, defined in the AMBA 3 protocol allows extending an APB transfer and transferring failure information.

# **APB3 Slave in the AMBA System**

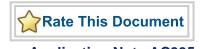

Figure 1 on page 2 shows a typical AMBA system. It shows the ARM processor connected to the AHB-Lite bus and to the APB3 bus via a bridge. There are several peripherals connected to the AHB-lite and APB3 buses. The peripherals on the AHB-lite bus are in general more complex, high performance, high throughput devices requiring an important amount of the bus bandwidth. In comparison, APB3 allows the connection of low throughput peripherals requiring lesser bandwidth. APB3 is much simpler than AHB-Lite and requires fewer gates.

1

Figure 1 • APB3 Slave in the AMBA System

As stated earlier, the FIC in SmartFusion allows bridging between the MSS and either an AHB-Lite or an APB3 interface. In most SmartFusion applications, the FPGA fabric is used for low bandwidth peripherals or blocks. You need to create an APB3 interface to the custom peripherals or blocks and then connect them to MSS via the FIC bridge.

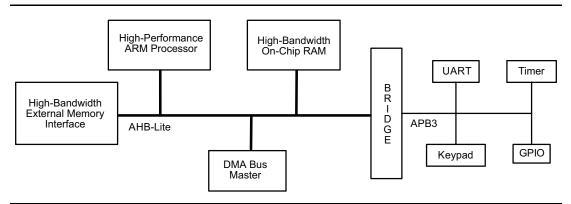

Figure 2 shows a custom logic block with APB3 interface connected to the MSS through CoreAPB3 in SmartFusion.

Figure 2 • Custom Logic with APB3 Interface Connected to MSS in SmartFusion

An APB3 interface is needed on custom low bandwidth peripherals in order to connect to an APB3 bus. The APB3 slave interface acts as a bridge between the APB3 bus and the peripheral device to which the bus is connected. It receives the APB3 bus signals and converts them to a form understood by the connected peripheral. The most common application of the APB3 interface is to read and write registers associated with the connected peripheral. The APB3 slave interface would be implemented to interface with the APB3 bus at one end and registers at the other end. It receives the control signals from the APB3 bus and uses them to generate the read and write enable signals for the registers. The write data and address signals of the APB3 bus are forwarded by the APB3 interface to the registers during write operations. During read operations, the data read from the registers is transmitted onto the APB3 bus.

The following sections describe APB3 in detail and provide examples of how to create an APB3 slave wrapper interface on the user custom logic or IP.

## **APB3 Bus Operation**

Table 1 gives the APB3 signals.

The AMBA specification defines an on-chip communications standard for designing high-performance embedded microcontrollers. AMBA-Lite APB, also known as APB V3 or APB3, is used to interface to any peripherals that are low bandwidth and do not require the high performance of a pipelined bus interface.

Table 1 • APB3 Signals

| Signal Name | Description                                                                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK        | Clock. The rising edge of PCLK times all transfers on the APB.                                                                                                                                                                                                                        |

| PRESETn     | Reset. The APB reset signal is active Low. This signal is usually connected directly to the system bus reset signal.                                                                                                                                                                  |

| PADDR       | Address. This is the APB address bus. It can be up to 32 bits wide and is driven by the peripheral bus bridge unit.                                                                                                                                                                   |

| PSELx       | Select. The APB bridge unit generates this signal to each peripheral bus slave. It indicates that the slave device is selected and that a data transfer is required. There is a PSELx signal for each slave.                                                                          |

| PENABLE     | Enable. This signal indicates the second and subsequent cycles of an APB transfer.                                                                                                                                                                                                    |

| PWRITE      | Write/read. This bus does a write to slave when PWRITE is High. It reads slave when PWRITE is Low. This is 1 bit.                                                                                                                                                                     |

| PWDATA      | Write data. This bus is driven by the peripheral bus bridge unit during write cycles when PWRITE is High. This bus can be up to 32 bits wide.                                                                                                                                         |

| PREADY      | Ready. The slave uses this signal to extend an APB transfer.                                                                                                                                                                                                                          |

| PRDATA      | Read data. The selected slave drives this bus during read cycles when PWRITE is Low. This bus can be up to 32 bits wide.                                                                                                                                                              |

| PSLVERR     | Slave error. This signal indicates a transfer failure. APB peripherals are not required to support the PSLVERR pin. This is true for both existing and new APB peripheral designs. Where a peripheral does not include this pin, the appropriate input to the APB bridge is tied Low. |

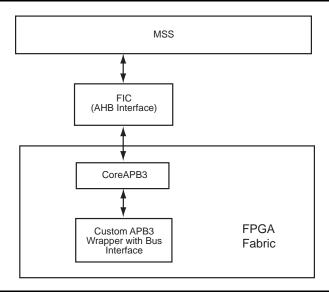

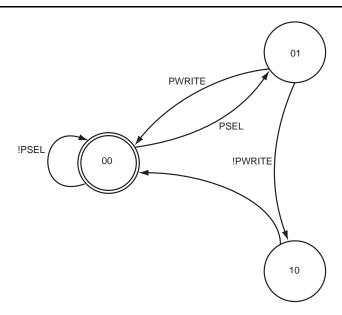

Figure 3 on page 4 shows the state diagram for APB3 bus specification. It has three states as explained below:

- IDLE: This is the default state for the peripheral bus.

- SETUP: When a transfer is required, the bus moves to this state where the appropriate select signal PSELx is asserted. The bus remains in this state for one clock cycle only and always moves to the ACCESS state on the next rising edge of the clock.

- ACCESS: In this state, the enable signal PENABLE is asserted. The address, write, and select signals should be stable during the transition from SETUP to ACCESS state. The transition from the ACCESS state is controlled by the PREADY signal from the slave:

- If PREADY is held Low by the slave then the peripheral bus remains in the ACCESS state.

- If PREADY is held High by the slave and no more transfers are required, the bus transitions from the ACCESS state to the IDLE state. Alternatively, if another transfer follows, the bus moves directly to the SETUP state.

Figure 3 • APB3 State Diagram

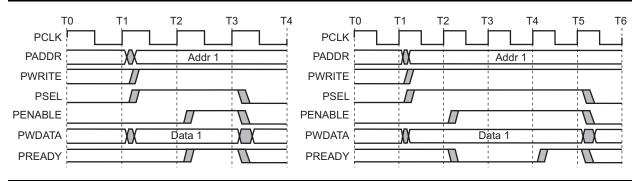

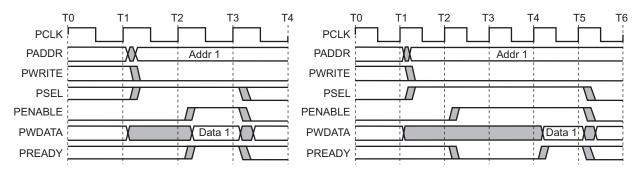

Figure 4 and Figure 5 show the APB3 timing diagrams. The APB write transfer starts with the address, write data, write signal, and select signal—all changing after the rising edge of the PCLK. In the next clock edge, the enable signal is asserted. PENABLE indicates that the Access phase is taking place. The address, data, and control signals all remain valid throughout this Access phase. The transfer completes at the end of this cycle. The enable signal, PENABLE, is deasserted at the end of the transfer. The select signal, PSELx (or PSEL), also goes Low unless the transfer is to be followed immediately by another transfer to the same peripheral. During an Access phase, when PENABLE is High, the transfer can be extended by driving PREADY Low. During a read transfer, the timing of the address (PADDR), write (PWRITE), select (PSEL), and enable (PENABLE) signals are as described in Write transfers. The slave must provide the data before the end of the read transfer. The transfer is extended if PREADY is driven Low during an Access phase.

Figure 4 • APB3 Write Transfer with and without Wait State

Figure 5 • APB3 Read Transfer with and without Wait State

# Implementing an APB3 Interface for a Custom Logic Block

This section introduces two design examples of how to create a custom APB3 wrapper for a user logic block. You can follow the same process and create an APB3 interface for your custom logic blocks implemented in the FPGA fabric. After creating the interface wrapper, connect it to the MSS and run the FPGA flow. The two appendices at the end of this document guide you through the FPGA flow using the Actel Libero<sup>®</sup> Integrated Design Environment (IDE):

- "Appendix A: Creating a Subsystem Design with a Custom APB3 Slave"

- "Appendix B: Simulating the User Logic Block"

To create an APB3 slave, sample the address and control and send the appropriate PREADY response. If the user logic block can accept or send the data in the next cycle, asserting PREADY is not necessary; otherwise insert wait state and assert PREADY. The logic block must have a dedicated register/memory interface that communicates with the MSS via an APB3 bus. This also helps in avoiding any timing problems. When writing RTL, define the specific register that communicates with the APB3 bus.

This document presents two design examples:

- "Example 1: Memory Block with APB3 Wrapper"

- "Example 2: Counter with APB3 Wrapper"

### **Example 1: Memory Block with APB3 Wrapper**

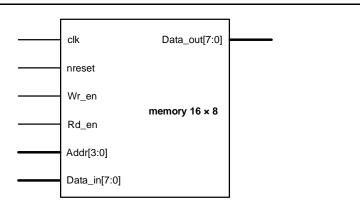

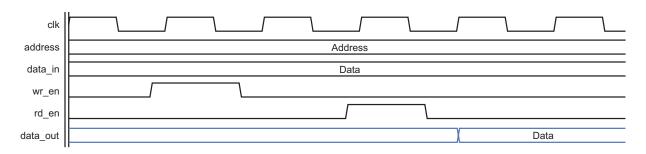

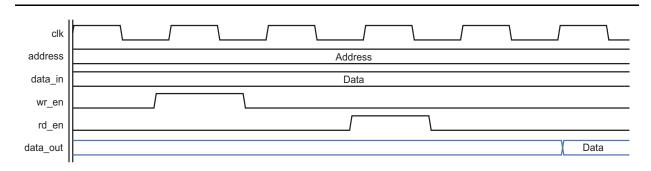

The example design uses a memory block of 8 bits wide by 16 bits deep that is memory mapped to the APB3 system. The memory acts like an APB3 slave. This memory is used in both regular and pipelined mode. Figure 6 shows the block diagram. Figure 7 and Figure 8 on page 6 show the timing diagrams for both regular and pipelined mode.

Figure 6 • Block Diagram - Memory Block

Figure 7 • Timing Diagram for Regular Mode

Figure 8 • Timing Diagram for Pipelined Mode

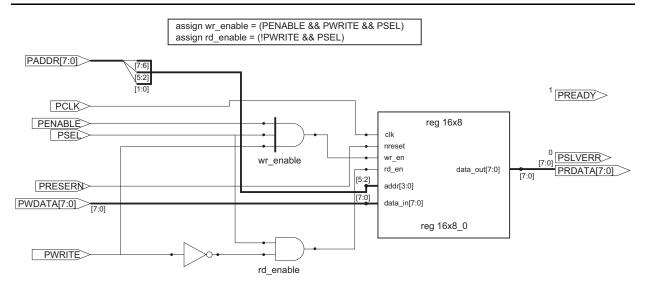

Creating an APB3 slave memory module is very simple. Create a wrapper that interfaces between APB3 signal and memory block. The wrapper logic must generate the write enable when the PSEL, PWRITE, and PENABLE signals are active. For read enable, user logic must generate the signal during the first cycle so that data is ready on the bus during the second cycle. The address and data signals connect directly to the memory block address and data ports. Figure 9 shows the RTL view for the wrapper. The write enable and read enable signals are generated as shown in the verilog code example below:

```

assign wr_enable = (PENABLE && PWRITE && PSEL);

assign rd_enable = (!PWRITE && PSEL);

```

Figure 9 • RTL View for the APB Slave Wrapper

To create an APB3 wrapper on the pipelined memory, user logic must use the PREADY signal to insert a wait state. Additionally, the user logic must generate the write enable when the PSEL, PWRITE, and PENABLE signals are active. For read enable, the user logic must generate the signal during the first cycle. However, there is a need to add an extra cycle due to the pipeline option. Figure 10 on page 7 shows the state diagram and sample verilog code for this wrapper.

```

begin

rd_enable <= 1'b0;

wr_enable <= 1'b1;

PREADY <= 1'b1;

end

else

begin

rd_enable <= 1'b1;

wr_enable <= 1'b0;

PREADY <= 1'b0;

end

end

end

2'b01 : begin

if (PWRITE)

begin

rd_enable <= 1'b0;

wr_enable <= 1'b0;

PREADY <= 1'b1;

fsm <= 2'b00;

end

else

begin

rd_enable <= 1'b0;

wr_enable <= 1'b0;</pre>

PREADY <= 1'b0;

fsm <= 2'b10;

end

end

2'b10 : begin

fsm <= 2'b00;

PREADY <= 1'b1;

end

default : fsm <= 2'b00;

```

Figure 10 • State Diagram and Sample Verilog Code for APB3 Slave Wrapper with Wait State

The memory block with APB3 wrapper can be connected to the MSS as described in the "Appendix A: Creating a Subsystem Design with a Custom APB3 Slave".

The sample Libero IDE project is available for download as a part of the design files from http://actel.com/download/rsc/?f=SmartFusion\_Build\_APB3core\_DF.

## **Example 2: Counter with APB3 Wrapper**

This design example uses a simple 32-bit counter. A wrapper is used to interface the counter to the APB3 bus. For illustration purposes, the master on the APB3 bus can load the counter value and can also enable the counter. The master can also read the counter value and check the status. Three registers are used in the wrapper to interface with the APB3 bus. Following is the sample VHDL code for this wrapper:

```

constant COUNTERLOADA

: std_logic_vector(4 downto 0) := "00000";

constant COUNTERVALUEA : std_logic_vector(4 downto 0) := "00100";

constant COUNTERCONTROLA : std_logic_vector(4 downto 0) := "01000";

p_reg_seq : process (PRESETn, PCLK)

begin

if (PRESETn = '0') then

TimerEn

<= (others => '0');

LoadEnReg <= '0';

elsif (PCLK'event and PCLK = '1') then

if (PWRITE = '1' and PSEL = '1' and PENABLE = '1' and PADDR = COUNTERCONTROLA)

then

TimerEn

<= PWDATA (0);

LoadEnReg <= '0';

elsif (PWRITE = '1' and PSEL = '1' and PENABLE = '1' and PADDR = COUNTERLOADA)

then

<= PWDATA(31 downto 0);

LoadEnReq <= '1';

end if;

end if;

end process p_reg_seq;

my_counter: Count32

port map(Clock

=> PCLK.

=> Count,

Aclr

=> PRESETn

Enable

=> TimerEn.

Sload

=> LoadEnReg,

Data

=> Load,

Tcnt

=> TIMINT);

-- Output data generation

p_data_out : process (PWRITE, PSEL, PADDR, Load, Count, TimerEn)

begin

DataOut <= (others => '0'); -- Drive zeros by default

if (PWRITE = '0' and PSEL = '1') then

case PADDR is

when COUNTERLOADA =>

DataOut(31 downto 0) <= Load;

when COUNTERVALUEA =>

DataOut(31 downto 0) <= Count;</pre>

when COUNTERCONTROLA =>

DataOut(0) <= TimerEn;</pre>

when others =>

DataOut <= (others => '0');

end case;

else

DataOut <= (others => '0');

end if;

end process p_data_out;

-- Generate PRDATA on falling edge

p_PRDATA : process (PRESETn, PCLK)

begin

```

The counter with APB3 wrapper can be connected to the MSS as described in the "Appendix A: Creating a Subsystem Design with a Custom APB3 Slave".

The sample Libero IDE is available for download as a part of the design files from <a href="http://actel.com/download/rsc/?f=SmartFusion\_Build\_APB3core\_DF">http://actel.com/download/rsc/?f=SmartFusion\_Build\_APB3core\_DF</a>.

# **Appendix A: Creating a Subsystem Design with a Custom APB3 Slave**

This appendix describes how to connect the custom APB slave interface to the MSS.

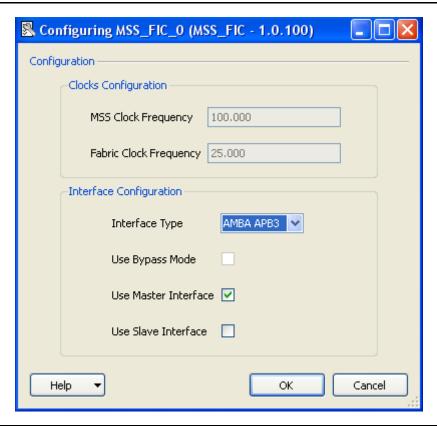

In the Actel SmartDesign Framework, configure the Fabric Interface inside the MSS configurator by double-clicking the Fabric Interface sub-configurator (Figure 11) and configure the FIC with APB3 interface.

Figure 11 • Configuring the Fabric Interface Controller

Select MSS\_Master\_APB bus interface on Fabric Interface and promote to the top level as shown in Figure 12.

Figure 12 • Promoting MSS\_Master\_APB Bus Interface to Top Level

- 3. Configure the Clock Management block and promote FAB\_CLK to the top level. Similarly, configure the Reset Management block and promote M2F\_RESET\_N to the top level.

- 4. Configure the other blocks inside the MSS configurator as needed and generate the MSS.

- Expand the Bus Interfaces section in the IP catalog. Select CoreAPB3 3.0.103 and drag it into the canvas.

- 6. Import or create the RTL code for the custom APB3 slave and select the RTL source code for the custom APB/AHB wrapper and drag it onto the canvas.

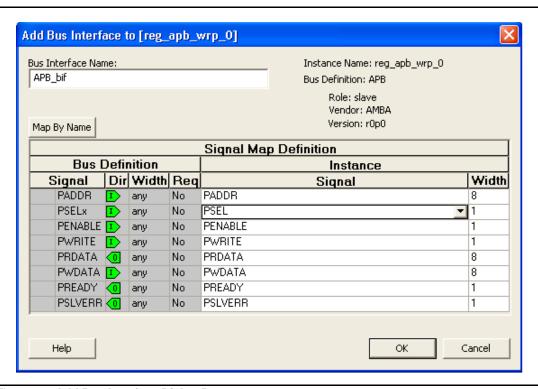

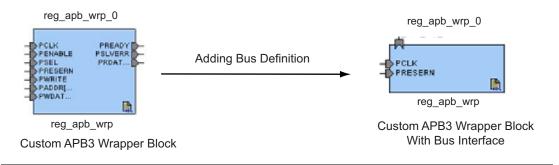

- 7. Add a bus interface to your APB/AHB wrapper instance. Select a bus definition from the **Bus Definition** tab in the Catalog and drag it onto your APB3 wrapper instance.

The Add Bus Interface dialog box opens (Figure 13). Select **Map by Name** to map the signals automatically. The tool attempts to map any similar signal names between the bus definition and pin names on the instance. Map other signals manually that are not mapped by **Map by Name**.

Figure 13 • Add Bus Interface Dialog Box

Figure 14 • Adding Bus Interface to Custom AHB Wrapper

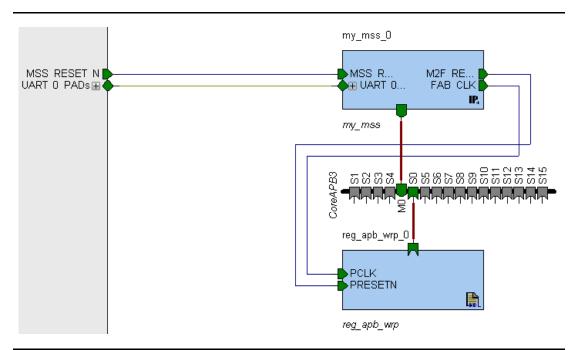

8. Connect the MSS to the custom APB3 slave via CoreAPB3, as shown in Figure 8 on page 6. Connect all other subsystem signals as needed.

Figure 15 • Connection Between Custom APB3 Slave and MSS

- 9. Connect the FAB\_CLK clock signal to the PCLK clock signal of the MSS.

- 10. Connect the M2F\_RESET\_N signal from FIC to the PRESETN signals of the fabric APB3 slave.

- 11. Connect other signals present on the fabric AMBA subsystem as needed, and generate the SmartDesign block.

# **Appendix B: Simulating the User Logic Block**

This section describes how to simulate user logic or an IP block using the BFM models. When the RTL code is generated by SmartDesign, the tool also creates three BFM files: test.bfm, User.bfm, and Subysystem.bfm. You need a customized User.bfm file to emulate Cortex-M3 transactions in the system. The following section describes the simulation setup for the memory block with APB3 wrapper design. Follow the same process for a user APB3 interface.

Open the BFM test script file (User.bfm) in the Libero IDE editor or any text editor. The script file appears under Simulation files for the SmartDesign component on the **Libero Files** tab.

Figure 16 • test.bfm Script File

2. Add or modify the lines shown in bold font below to test.bfm. Note that the BFM command should map the address and register setting for your design.

```

procedure user_main;

# uncomment the following include if you have soft peripherals in the fabric

# that you want to simulate. The subsystem.bfm file contains the memory map

# of the soft peripherals.

include "subsystem.bfm"

# add your BFM commands below:

";

print "

";

print "*****************************

print "Testing custom APB slave";

write

b reg_apb_wrp_0

0x00 0x01;

write b reg_apb_wrp_0 0x04 0x05;

write b reg_apb_wrp_0

0x08 0x09;

wait 5;

readcheck b reg_apb_wrp_0

0x00 0x01; # Expect value 01

readcheck b reg_apb_wrp_0 0x04 0x05; # Expect value 05

readcheck b reg_apb_wrp_0

0x08 0x09; # Expect value 09

return

```

- 3. Save the file user.bfm.

- **Important:** Note that the BFM test script as test.bfm will be overwritten if the core is regenerated. Actel recommends that you keep a backup copy.

- 4. Change simulation runtime to meet your needs and click the **Simulation** button in the Libero IDE Design Flow window to run pre-synthesis simulation. You must add the correct waveform to see the signal toggling.

Actel is the leader in low-power FPGAs and mixed-signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at www.actel.com.

### **Actel Corporation**

2061 Stierlin Court Mountain View, CA 94043-4655 USA Phone 650.318.4200 Fax 650.318.4600

### Actel Europe Ltd.

River Court, Meadows Business Park Station Approach, Blackwater Camberley Surrey GU17 9AB United Kingdom

### Phone +44 (0) 1276 609 300

Fax +44 (0) 1276 607 540

### **Actel Japan**

EXOS Ebisu Buillding 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan Phone +81.03.3445.7671 Fax +81.03.3445.7668 http://jp.actel.com

# **Actel Hong Kong**

Room 2107, China Resources Building 26 Harbour Road Wanchai, Hong Kong Phone +852 2185 6460 Fax +852 2185 6488 www.actel.com.cn

© 2010 Actel Corporation. All rights reserved. Actel, Actel Fusion, IGLOO, Libero, Pigeon Point, ProASIC, SmartFusion and the associated logos are trademarks or registered trademarks of Actel Corporation. All other trademarks and service marks are the property of their respective owners.